MSP432 Online Training Series - Part 4

MSP432™ MCUs Training

Part 4: Clock System & Memory

1

CS |

High-level Features

• Flexible clock sources & distribution:

– 5 clocks from 7 sources (2 external, 5 internal)

– Selections suitable for high-speed & low-power operations

• Wide range of operating frequency

– 10kHz to 48 MHz

– Fine intermediate steps with dividers & tuning

• Configurable & robust system:

– Run-time lockable configuration

– Failsafe mechanism with interrupts for external sources

CS |

HF & LF Oscillators

Frequency Oscillator s

1-48

MHz

DCO

MCLK SMCLK HSMCLK ACLK BCL

K

✔ ✔ ✔

1-48

MHz

HFXT

24MHz MODOSC

5MHz SYSOSC

32kHz LFXT

32kHz

128kHz

REFO

10kHz VLO

✔

✔

✔

✔

✔

✔

✔

✔

✔

✔

✔

✔

✔

✔

✔

✔

✔

✔

✔

✔

Comments

Internal integrated digitally controlled oscillator.

High frequency crystal.

Frequency range is SW configurable.

Internal osc. option for peripherals such as ADC

Internal, direct clock for

ADC failsafe for HFXT

Low-frequency oscillator

Internal low-frequency oscillator.

Failsafe* (32kHz) for

LFXT

Internal ULP LF oscillator

Clock selection for WDT

CS |

High-accuracy tune-able DCO

• 6 tune-able frequency ranges

– Each range has calibrated center frequency

– Example: [8-16MHz] range has a calibrated 12MHz center frequency

• Tune-able within each frequency range

– Center Frequency +/- 2 12 steps DCOTUNE register

• DCO accuracy:

– Internal resistor: + 2.65 % [Calibrated]

– External resistor : + 0.4 % [91kΩ + 0.1% ]

• Failsafe for internal resistor mode

Frequency Range

1.5

3MHz

4MHz

6MHz

8MHz

12MHz

16MHz

24MHz 48MHz

Calibrated Center Frequency

4

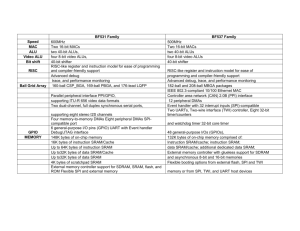

Memory |

Overview

Memory

Flash

Size

256kB + 4kB

Sector: 4kB

Speed

16MHz

SRAM

64kB

Bank: 8kB

ROM

32kB

48MHz

48MHz

BSL

8kB 16MHz

Features

Speed boost with 128-bit buffer & pre-fetch

Powerful security features

Dynamic bank power-down & retention options for low power

Robust DriverLib APIs integrated to save application space

Lower power execution

UART/I2C/SPI Boot-Strap Loader provided

*Possible change: programmable BSL in next devices/revisions

5

Memory |

Flash

Bank 1

Bank 2

INFO

4kB 4kB

4kB

4kB

128kB

Individually [un-]protected from write/erase

> 10 5 erase cycles

}

• Independent banks simultaneous read/execute and program/erase operations

• 128-bit buffer Power savings & higher effective speed with ARM’s pre-fetch

• Hardware assisted operations

– Burst data comparison for fixed patterns (data fill check)

– Flash program modes with auto-computed parity & auto-verify :

– Write immediate, 128-bit full word write, or 4*128-bit burst mode

• Flexible Code security & protection options:

– Individual Flash IP sector protection, further secured/protected with MPU

– Up to 4 IP-protection memory zones

6

Memory |

RAM

• Up to 64KB of banked SRAM architecture

• 8 dynamically configurable banks:

– Enable/disable banks to optimize active mode power consumption

– Retain/not retain content in LPM3 to minimize SRAM leakage power consumption

Memory size

8KB

SRAM banks

Bank 0 enable/retention (always enabled)

Bank 1 enable/retention

Bank 2 enable/retention

. . .

Bank 6 enable/retention

Bank 7 enable/retention

16KB

24KB

…

56KB

64KB

Memory |

Memory Map

0x00000000 Flash

0x01000000 ROM

0x20000000 SRAM

Bit-Band

0x22000000 Bit-banded SRAM

0x40000000 Peripherals (Registers)

Bit-Band

0x42000000 Bit-banded Peripherals

0xE0000000 Instrumentation, ETM, etc.

256kB + 4kB

- Interrupt Vector Table

- Application Code

Peripheral Driver Library

Ultra-low-leakage SRAM

64kB = 8 x 8kB banks

Bit-banded

Peripheral Space

Register directly accessible

Bit-banded

Power, Clock, & Memory |

Overall System

Design

• Regulator: DC-DC or LDO

– DC-DC yields higher efficiency than LDO at higher speed

– DC-DC requires longer start-up time and transitions from Sleep Modes

• Flash wait states

– @ MCLK > 12MHz for VCORE = 0

– @ MCLK > 16MHz for VCORE = 1

SystemFrequency VCORE

• VCORE level @ MCLK > 24MHz

0-12MHz 0

LDO/DC-DC* Flash Wait States

LDO 0

12-16MHz

16-24MHz

24-32MHz

32-48MHz

0

0

1

1

LDO

LDO

DC-DC

DC-DC

1

1

1

2

9