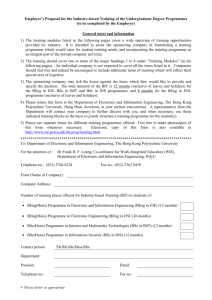

08200345 - Introduction - University of Hertfordshire

advertisement

School of Electronic, Communication and Electrical Engineering BEng Final Year Project Report Electrical and Electronics Engineering Final Year Project Report School of Electronic, Communication and Electrical Engineering University of Hertfordshire Colour Space Conversion Using Distributed Arithmetic Report by: Han Feng Supervisor: F. Bensaali Date: 14 April 2010 Number : 08200345 School of Electronic, Communication and Electrical Engineering BEng Final Year Project Report Abstract This project is base on Field-Programmable Gate Array (FPGA) and VHDL, using distributed arithmetic (DA) to achieve color space conversion (CSC). The project mainly focused on how to convert RGB to YCrCb research and analysis, Description distributed arithmetic and mathematical equations derived. Colour space conversion mainly by comprises parallel ACCumulator (ACC) and a right shifter and ROM. Research and analysis of the individual components that make up the complete system is explained. Using distributed arithmetic method for processing CSC has a smaller delay and higher data throughput to meet treatment needs CSC. Finally, the program is fine tuned for improvement and the possibility of further development assessed. School of Electronic, Communication and Electrical Engineering BEng Final Year Project Report Acknowledgements I would like to thank my project supervisor F. Bensaali for his unconditional technical support and guidance throughout. Also, the author would like to thank his colleagues in giving the author full cooperations, moral support and technical advice. Besides that, the author would also like to thank his family for all the support that they give. Finally, the author would like to thank the university for giving him the opportunity to expose himself in something that never been meet before. Thanks School of Electronic, Communication and Electrical Engineering BEng Final Year Project Report Table of contents Abstract .......................................................................... 2 Acknowledgements ........................................................ 3 Table of contents ............................................................ 4 LIST OF FIGURES ............................................................. 6 Glossary .......................................................................... 7 1. Introduction ............................................................... 8 1.1 Colour Space .......................................................... 8 1.2 Distributed Arithmetic............................................ 9 1.3 FPGA .................................................................. 10 1.3.1 Advantage of FPGA ........................................ 11 1.4 Very-High-Speed Integrated Circuit HardwareDescription Language (VHDL) ............... 12 1.5 AIMS ..................................................................... 12 1.6 OBJECTIVES........................................................... 12 1.7 Chapter Organization .............................................. 13 2. Background theory................................................... 13 School of Electronic, Communication and Electrical Engineering BEng Final Year Project Report 2.1 Mathematical background of Distributed Arithmetic ................................................................................... 14 2.2 Into the contents of ROM..................................... 16 2.3 Shifter register...................................................... 18 2.4 Software to be use ................................................ 18 3. Proposed architecture ............................................... 19 4 VHDL implementation ............................................ 20 5 Result and simulation .............................................. 23 6 conclusion and future work ....................................... 27 7 Project Time plan ..................................................... 28 Reference ..................................................................... 29 APPENDICES .................................................................. 30 School of Electronic, Communication and Electrical Engineering BEng Final Year Project Report LIST OF FIGURES Figure 1 general block diagram for RGB to YCrCb……………………………… 9 Figure 2 FPGA generally block……………………………………………………..10 Figure 3 Conversion formulas………………………………………………………12 Figure 4 Content of the ROM……………………………………………………….14 Figure 5 The content of the ROMs (RGB to YCrCb)……………………………….15 Figure 6 ROM 1 decimal to binary…………………………………………………..15 Figure 7 ROM 2 decimal to binary…………………………………………………..16 Figure 8 ROM 3 decimal to binary…………………………………………………..16 Figure 9 Serial CSC based DA architecture block…………………………………..18 Figure 10 output of ROM……………………………………………………………19 Figure 11 ROM1 simulation…………………………………………………………21 Figure 12 ROM2 simulation…………………………………………………………22 Figure 13 ROM3 simulation…………………………………………………………23 School of Electronic, Communication and Electrical Engineering BEng Final Year Project Report Glossary CSC: colour space conversion VHDL: Very-High-Speed Integrated Circuit HardwareDescription Language FPGA: Field Programmable Gate Array DA: Distributed Arithmetic School of Electronic, Communication and Electrical Engineering BEng Final Year Project Report 1. Introduction In the world today, digital image, video technology has been in computers, cell phones, digital television and other field has been very widely used. In the digital signal for display, the most common are RGB (red, green, blue) color space, which is the most common computer color space, are widely used in computer graphics, imaging systems and color televisions. The YCbCr color space describes the concept of gray and color, as is easy to implement compression to facilitate the transmission and processing, it is widely used in radio and television system. Therefore, in order to be used in many video devices, color space converter has a huge market. The most basic function is to realize from one space to another space conversion. This project is base on Field-Programmable Gate Array (FPGA) and VHDL, using distributed arithmetic (DA) to achieve color space conversion (CSC). 1.1 Colour Space Color space is a three-dimensional coordinate system, each color expressed by a point. In the RGB color space, red, green, blue are basic element. For a true color image, the red, green, and blue components of a pixel are each with eight bits width. Overall, it may be 16 million possible colors. Each component has a range of 0 to 255, all three 0's production of black and white production of three 255s [1]. YCbCr is also a color space, Where Y refers to the color Luminance, is image gray value, is the role of the human eye color brightness caused by the feeling, CbCr express Chrominance, reflecting the color of the category, are called blue color and red color. The human eye on the Y component video is more sensitive to color components for the adoption of the sub-sampling to reduce the chroma components, the eye will be aware of any changes in image quality. The main sub-sampling format YCbCr 4:2:0, YCbCr 4:2:2 and YCbCr 4:4:4. 4:2:0 that every 4 pixels with 4 brightness component, two color components (YYYYCbCr), only sample odd scan lines, the portable video device School of Electronic, Communication and Electrical Engineering BEng Final Year Project Report (MPEG-4) and videoconferencing (H.263) the most common format; 4:2:2 that every 4 pixels with 4 luminance components, 4 color components (YYYYCbCrCbCr), a DVD, digital TV, HDTV and other consumer video equipment, the most common format; 4:4:4 that the whole pixel matrix (YYYYCbCrCbCrCbCrCbCr), for high quality video applications, studio and professional video products. Luminance Y is through RGB input signal to create. Method is a specific part of the RGB signal superimposed together, and Cb reflects the blue part of RGB input signal and the RGB signal intensity differences between the values, while Cr is reflected in the red part of RGB input signal and RGB signal intensity value between differences. In image processing, RGB color in the production of any of its three-color all need the same bandwidth, processing efficiency is not high; while YCbCr is has a very high compression rate and transmission rate. In the image processing so often have to use YCbCr and RGB color space conversion. The following is the conversion between RGB to YCRCB general block diagram figure 1[1]. Figure 1 general block diagram for RGB to YCrCb. 1.2 Distributed Arithmetic Distributed Arithmetic (DA) is an important technique to implement colour space School of Electronic, Communication and Electrical Engineering BEng Final Year Project Report conversion functions in FPGAs. Distributed Arithmetic which is a bit level rearrangement of a multiply accumulate to hide the multiplications. The two proposed architectures are based on serial and parallel manipulation of pixels [1]. DA is a very efficient mechanism for computations that are dominated by inner products (convolution). DA is good way to trade combinational logic with memory for high-performance computation [2]. At present, some FPGA internal has multiplier, i.e hardware multiplier. Distributed algorithm to complex multi-digit multiplication into a simple "and" operation, but also by the number of bits into a shift right operation, effectively improving the operation speed, reduces the complexity of the structure. Convolution algorithm using distributed computing. colour space conversion using this algorithm has the following advantages: reduced memory cell size, shared memory cell contents, reducing the data bus bit width. FPGA chip resources in order to save a serial distributed algorithm. The following mathematical concepts will be referred to DA. 1.3 FPGA Field Programmable Gate Array (FPGA) is a silicon chip device and made up of an array of logic blocks. The blocks can be configured and connected together by a user to create an electronic circuit [3]. FPGA usually consists of several components. 1. A matrix of programmable logic blocks. 2. I/O cells, which connect the logic cells to external signals. 3. A programmable routing network interconnecting the cells [3]. School of Electronic, Communication and Electrical Engineering BEng Final Year Project Report Figure 2 FPGA generally block 1.3.1 Advantage of FPGA Advantages of FPGA are: fast and flexible application. 1. Performance advantage for highly parallel applications. 2. Hardware "load files" can be updated through software patches. 3. The same circuitboard arrayed with FPGA chips can run multiple algorithms. 4. That has performance advantages of hardware-level algorithms, but can also be modified through software updates [4]. Using the FPGA to achieve Color space conversion has high speed, low cost, easy to implement. School of Electronic, Communication and Electrical Engineering BEng Final Year Project Report 1.4 Very-High-Speed Integrated Circuit HardwareDescription Language (VHDL) VHDL is a language for describing digital electronic systems [5]. VHDL, mainly has the following advantages: 1. VHDL language has strong language structure, using simple VHDL program can describe complex hardware, and it also has a multi-level description of circuit design features, can describe the system-level circuit, and also can describe the gate-level circuit. 2. Using VHDL describe to hardware, the designer does not need to first consider the choice to design the device. The benefit of this is to make designers to concentrate on the optimization of circuit design, without the need to consider other issues. 3. VHDL language is a description, simulation, synthesis, optimization, and routing of standard hardware description language, so it can make between design results in the designer to easily exchange and sharing, thus reducing the workload of the hardware circuit design, shorten the development cycle [5]. The project is use VHDL to write ROM, accumulator and shift register. 1.5 AIMS The aim of this project is to propose and implement on FPGA an area and time efficient colour space converter using distributed arithmetic approach which is a bit level rearrangement of a multiply accumulate to hide the multiplications. Schematic and/or VHDL will be used for the hardware implementation. 1.6 OBJECTIVES 1. Using distributed arithmetic to design a CSC 2. Using VHDL description language School of Electronic, Communication and Electrical Engineering BEng Final Year Project Report 3. To describe CSC architecture 4. Simulation and analysis. 1.7 Chapter Organization This section contains a very brief summary of all of the chapters that will be included later in this report. It is intended as a guideline for the reader of this project to extract the right information that maybe be in interest to himself. Chapter 1: This chapter introduce the project in a general manner, with objectives of the project and also the project overview. Chapter 2: This chapter will describe the theoretical background of color space conversion. Chapter 3: This chapter will describe structure of color space Chapter 4: This chapter will describe about the programming language, VHDL implementation. Chapter 5: Testings that is made to verify the project is described here in this chapter. Chapter 6: This chapter will have a conclusion on this report and also possible further enhancement. 2. Background theory Before making any kind of optimisation, design and implementation even for the simplest forms of colour space conversion, it is important for the engineer to have a deep and broad knowledge of the parts that make up the system and how everything connects together. The project involves a number of important theoretical backgrounds, which includes background mathematical theory of distributed arithmetic, read-only memory (ROM), School of Electronic, Communication and Electrical Engineering BEng Final Year Project Report the shifter and accumulator. Colour space conversion can be expressed as a Matrix-Vector (MV) multiplication. ROM-based DA uses a ROM table to store the precomputed data, which makes it regular and efficient in the use of the silicon area, in a VHDL implementation. Right shifter the function of the shift register are input data storage, and under the control signal at the input of data output shift. 2.1 Mathematical background of Distributed Arithmetic For each pixel, from one color space to another color space conversion formulas can be summarized as follows [1]: Figure 3 Conversion formulas Where, (A, B, C) may correspond to (Y, Cb, Cr) component, or (R, G, B) component, and (X0, X1, X2) corresponds to the opposite of (R, G, B) component or (Y, Cb, Cr) component [1]. Here the distributed algorithm to achieve the above matrix vector multiplication method: Due to the symmetry, so just study a component, as follows: Here, F show A, B or C; a0, a1, a2, a3, respectively, (1) in the coefficient matrix of a row factor. School of Electronic, Communication and Electrical Engineering BEng Final Year Project Report Since each Xi is an integer between 0-255, so Xi can be expressed as 8-bit binary as follows: Here, Xi, m, said Xi each value, value is 0 or 1; to (3) into (2), so: To (4) to begin in the following partial product can be expressed as sum of the form: Because ai is coefficients value and Xi.m can only take 0 or 1, so only 23 = 8 possible values. Therefore given the table below , School of Electronic, Communication and Electrical Engineering BEng Final Year Project Report Figure 4 Content of the ROM 2.2 Into the contents of ROM ROM has a storage function. A colour in the RGB colour space is converted to the Y0CrCb colour space using the following equation [1]: According to the above formula and table show that table of below: School of Electronic, Communication and Electrical Engineering BEng Final Year Project Report Figure 5 The content of the ROMs (RGB to YCrCb) Because the ROM is memory binary data, it must first be converted decimal to binary then the data memory to ROMs. ROM 1 decimal Binary 0 00000000 0.098 00011001 0.504 10000001 0.602 10011010 0.257 01000001 0.355 01011010 0.761 11000010 0.859 11011010 Figure 6 ROM 1 decimal to binary ROM 2 decimal Binary 0 00000000 -0.071 11101110 -0.368 10100010 -0.439 10010000 0.439 01110000 0.368 01011110 School of Electronic, Communication and Electrical Engineering 0.071 00010010 0 00000000 BEng Final Year Project Report Figure 7 ROM 2 decimal to binary ROM 2 decimal Binary 0 00000000 0.439 01110000 -0.291 10110110 0.148 00100001 -0.148 11011111 0.291 01001010 -0.139 10010000 0 00000000 Figure 8 ROM 3 decimal to binary 2.3 Shifter register Register is a computer and other digital systems used to store code or data logic components. Its main component is the trigger. A flip-flop can store a binary code, binary code to store n-bit register will need to use n-flip-flop. 2.4 Software to be use This project uses the main software is Altium designer 6 and Xilinx ISE. Altium Designer 6 broadens the traditional boundaries of board-level design, fully integrated design features and SOPC FPGA design implementation capabilities, allowing engineers can design in the FPGA and PCB design, and integrated embedded design. Support both schematic and HDL hardware description input mode; also supports the design of VHDL-based simulation, mixed-signal circuit simulation, layout, front / rear signal integrity analysis [6]. School of Electronic, Communication and Electrical Engineering BEng Final Year Project Report 3. Proposed architecture This project only to convert between RGB to Ycrcb so the proposed architecture consists of three identical Processing Elements (PEs) and one memory blocks. Each PE comprises a parallel ACCumulator (ACC) and a right shifter and each memory block consists of three ROMs with the size of 23=8 each. See figure 9 Figure 9 Serial CSC based DA architecture block As shown in Figure 9 assume b0,m b1,m and b2,m is R,G,B and C0,C1,C2 is Y, Cr, Cb. First of all, RGB to binary input to ROM1 according to the formula and table (figure 5 ) and Po output value can be learned. R G B Po P1 P2 0 0 0 00000000 00000000 00000000 0 0 1 00011001 11101110 0 1 0 10000001 10100010 10110110 01110000 School of Electronic, Communication and Electrical Engineering BEng Final Year Project Report 0 1 1 10011010 10010000 00100001 1 0 0 01000001 01110000 11011111 1 0 1 01011010 01011110 1 1 0 11000010 00010010 10010000 1 1 1 11011010 00000000 00000000 01001010 Figure 10 output of ROM According to Figure 5 calculated values into the ROM1 when the input value is 000-111 output the corresponding 8-bit value. This 8-bit value input through ACCumulator and a right shifter to output Co. Such a conversion can be done. 4 VHDL implementation VHDL can describe most of the devices such as ROM, shifter and ACCumulator. This is ROM code: entity ROM1_ENT is port ( CLK1 : in std_logic; CE1 : in std_logic; RE1 : in std_logic; ADDR : in std_logic_vector(2 downto 0); DATA : out std_logic_vector (7 downto 0) ); end ROM1_ENT; architecture ROM1_arch of ROM1_ENT is type ROM1 is array(0 to 7) of std_logic_vector (7 downto 0); constant Content: ROM1 := ( 0 => "00000000", 1 => "00011001", 2 => "10000001", 3 => "10011010", 4 => "01000001", 5 => "01011010", 6 => "11000010", 7 => "11011010" ); begin Used to describe the color space conversion ROM is because Color space conversion School of Electronic, Communication and Electrical Engineering BEng Final Year Project Report can be expressed as a matrix, vector (MV) multiplication, DA distributes arithmetic operations rather than grouping them as multipliers do [1]. Conventional DA, called ROM based DA, decomposes the variable input of the inner product to bit level in order to generate precomputed data [1]. Therefore, color space conversion module can be quickly selected ROM data processing. Describe the shift register can be used in IF statement or CASE statement, case statement is used to describe bus behavior, encoder and decoder structure. Case statement, readable, very simple, case statement, the general form: Comparison Case statement and If statement: 1. The behavior selector can also be used with IF statement case statement. 2. If statement is ordered, the first dealing with the most start, the conditions of the highest priority, the priority of the conditions of post-processing times. 3. Case statement is disordered, all expression values are processed in parallel. 4. Case statement in the conditional expression cannot be repeated Therefore, the use CASE statements describe the shift register is the best option. if rising_edge(CLK) then CASE i is School of Electronic, Communication and Electrical Engineering BEng Final Year Project Report when 0 => TEMP_data_out <=DATA; when 1 => TEMP_data_out(6 downto 0) <=DATA (7 downto 1)&"0"; when 2 => TEMP_data_out(5 downto 0) <=DATA (7 downto 2)&"00"; when 3 => TEMP_data_out(4 downto 0) <=DATA (7 downto 3)&"000"; when 4 => TEMP_data_out(3 downto 0) <=DATA (7 downto 4)&"0000"; when 5 => TEMP_data_out(2 downto 0) <=DATA (7 downto 5)&"00000"; when 6 => TEMP_data_out(1 downto 0) <=DATA (7 downto 6)&"000000"; when 7 => TEMP_data_out(0 downto 0) <=DATA (7 downto 7)&"0000000"; when others => null; end case; end if; i<=i+1; end process; School of Electronic, Communication and Electrical Engineering BEng Final Year Project Report 5 Result and simulation Figure 11 ROM1 simulation ROM1 the simulation results same with the theoretical value R G B DATA 0 0 0 00000000 0 0 1 00011001 0 1 0 10000001 0 1 1 10011010 1 0 0 01000001 1 0 1 01011010 1 1 0 11000010 1 1 1 11011010 School of Electronic, Communication and Electrical Engineering BEng Final Year Project Report Figure 12 ROM2 simulation ROM2 the simulation results same with the theoretical value R G B DATA1 0 0 0 00000000 0 0 1 11101110 0 1 0 10100010 0 1 1 10010000 1 0 0 01110000 1 0 1 01011110 1 1 0 00010010 1 1 1 00000000 School of Electronic, Communication and Electrical Engineering BEng Final Year Project Report Figure 13 ROM3 simulation ROM3 the simulation results same with the theoretical value. R G B DATA2 0 0 0 00000000 0 0 1 01110000 0 1 0 10110110 0 1 1 00100001 1 0 0 11011111 1 0 1 01001010 1 1 0 10010000 1 1 1 00000000 School of Electronic, Communication and Electrical Engineering BEng Final Year Project Report This diagrams shows that integrated into all of the ROM up. Since all the devices connected to simulation has error so have not result. School of Electronic, Communication and Electrical Engineering BEng Final Year Project Report 6 conclusion and future work With the development of integrated circuit technology, FPGA because of its flexibility and parallelism, more and more in the use of modern electronic system design. This report describes using distributed arithmetic (DA) to achieve color space conversion (CSC). From one color space to another color space conversion, mainly referred to the conversion between RGB to YCrCb. Through the use of VHDL description of the device can achieve the functions of the device. The project is very hard and complex, so it can improve the ability of independent thinking. What’s more, much information should be searched on the books and internet, so it offers new non-traditional possibilities how to improve and complete the classical educational methods. The whole of this colour space conversion project have enhancement to further develop it. For example: Other devices can be used to replace ROM, optimization and compression algorithms that can reduce the computation delay and reduce the hardware area. School of Electronic, Communication and Electrical Engineering 7 Project Time plan BEng Final Year Project Report School of Electronic, Communication and Electrical Engineering BEng Final Year Project Report Reference [1]. F. Bensaali; A. Amira; ‘Accelerating colour space conversion on reconfigurable hardware’ 27 June 2004. [2] Applications of Distributed Arithmetic to Digital Signal Processing from http://twins.ee.nctu.edu.tw/courses/vsp_04/handout/DA.pdf [3] F. Bensaali “Microelectronics & VLSI” University of Hertfordshire, page. [4] Leveraging FPGAs to Empower Research and Reduce Operational Costs from http://www.timelogic.com/technology_fpga.html [5] Peter J. Ashenden “The VHDL Cookbook” July, 1990 [6] Altium Designer 6 from http://www.microchipzone.com/html/ruanjianxiazai/2009/0220/472.html School of Electronic, Communication and Electrical Engineering APPENDICES ROM1 CODE BEng Final Year Project Report School of Electronic, Communication and Electrical Engineering ROM 2 code BEng Final Year Project Report School of Electronic, Communication and Electrical Engineering ROM 3 code BEng Final Year Project Report School of Electronic, Communication and Electrical Engineering ROM code BEng Final Year Project Report School of Electronic, Communication and Electrical Engineering Shifter code BEng Final Year Project Report School of Electronic, Communication and Electrical Engineering ACCumulator code BEng Final Year Project Report