Memory Interface & The 3 Buses

advertisement

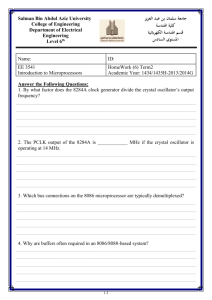

Khaled A. Al-Utaibi alutaibi@uoh.edu.sa Memory Interface and the 3 Buses Interfacing the 8088 Processor Interfacing the 8086 Processor Interfacing the 386 and 486 Processors Interfacing the Pentium Processor Address Decoding Techniques When interfacing memory, all three system buses-the address, control, and data buses-are involved. The address bus specifies the memory locations to be accessed. The control bus specifies the direction of the data transfer (into or out of the processor) The data bus carries the transferred data. Example 1: Show how to interface a (64K x 8) SRAM chip to an 8088 processor. Interface 8088 Microprocessor 64Kx8 SRAM (1) Because the 8088 has an 8-bit data bus, only a single SRAM chip is required (one memory bank). (2) The memory space of the 8088 processor is 1MB which consists of 1MB/64KB =220/216=24 =16 different address ranges each of size 64K as shown in Figure 1. (3) We can map the SRAM chip to any one of these address ranges (say the 14th address range 1110). (4) The SRAM chip has 64K different memory locations. Hence, it requires 16 address lines (64K =26x210 = 216). (5) The address bus of the 8088 (20 address lines A19-A0) will be interfaced to the SRAM as follows: The least significant address lines A15-A0 are used to address memory locations in the SRAM chip as shown in Figure 3. The most significant address lines A19-A16 are used to select the required address range in the memory space of the 8088 (i.e. select the SRAM chip) as shown in Figure 4. A19 A18 A17 decoding A16 A15 A14 A13 A12 A11 A10 A9 A8 A7 addressing A6 A5 A4 A3 A2 A1 A0 (6) The control-bus of the 8088 is interfaced to the SRAM as follows: Decode the M/IO’, RD’, and WR’ signals to generate 4 signals Memory Read (MEMR’), Memory Write (MEMW’), I/O Read (IOR’) and I/O Write (IOW’) as shown in Figure 2. Connect MEMR’ to OE’ and MEMW’ to WE’ as shown in Figure 3. (7) The data-bus of the 8088 is interfaced to the SRAM by connecting the buffered data lines D7-D0 to input/output lines (I/O7-I/O0) of the SRAM as shown in Figure 3. Figure 1: Address ranges of the 8088 microprocessor M / IO 0 RD WR MEMR MEMW IOR 0 1 1 1 0 1 0 1 0 1 1 1 0 1 0 1 0 1 1 1 1 1 0 1 0 1 1 Figure 2: Decoding the RD’, WR’ and M/IO’ signals. IOW Figure 3: Memory interface of Example 1. Figure 4: Memory interface of Example 1 with address decoder. Example 2: Show the decoder required to map the 64K memory interface the previous figure to the address range C0000H to CFFFFH. A19 A18 A17 A16 A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 Starting 1 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 Address Ending 1 1 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 Address decoding addressing Figure 5: Address decoding for Example 2. Example 3: Show how to interface a (64K x 8) SRAM chip(s) to an 8086 processor. Interface 8086 Microprocessor 64Kx8 SRAM (1) Because the 8086 has a16-bit data bus, two SRAM chips are required (two memory banks 2x64KB = 128KB). (2) The memory space of the 8086 processor is 1MB which consists of 1MB/128 KB = 220 / 217 = 23 = 8 different address ranges each of size 128K as shown in Figure 6. (3) We can map the each one of the two SRAM chips to one of these address ranges (say the 6th address range 111). (4) The SRAM chip has 64K different memory locations. Hence, it requires 16 address lines (64K =26 x 210 = 216). (5) The address bus of the 8086 (20 address lines A19-A0) will be interfaced to the SRAM as follows: The least significant address lines A16-A1 are used to address memory locations in the SRAM chip as shown in Figure 6. The most significant address lines A19-A17 are used to select the required address range in the memory space of the 8086 (i.e. select the two SRAM chips) as shown in Figure 6. The address line A0 and BHE’ signal are used to select even byte, odd byte or both as shown in Table 1. A19 A18 A17 decoding A16 A15 A14 A13 A12 A11 A10 A9 A8 A7 addressing A6 A5 A4 A3 A2 A1 A0 even byte (6) The control-bus of the 8086 is interfaced to the SRAM as follows: Decode the M/IO’, RD’, and WR’ signals to generate 4 signals Memory Read (MEMR’), Memory Write (MEMW’), I/O Read (IOR’) and I/O Write (IOW’) as shown in Figure 2. Connect MEMR’ to OE’ and MEMW’ to WE’ as shown in Figure 6. (7) The data-bus of the 8086 is interfaced to the SRAM (See Figure 6) by connecting: The buffered data lines D7-D0 to input/output lines (I/O7-I/O0) of the even SRAM. The buffered data lines D15-D8 to input/output lines (I/O7-I/O0) of the odd SRAM. Figure 5: Address ranges of the 8086 microprocessor Table 1: Selecting the even and odd bytes in the 8086 microprocessor Figure 6: Memory interface of example 3 Example 4: Assume the decoder in previous slide is a three-input NAND gate and determine the range of addresses occupied by this interface. Example 5: Show how to interface a 64K RAM module to an 8086 processor starting at address C0000H. Interface 8086 Microprocessor 64K RAM 64K RAM Module (1) Because the 8086 has a16-bit data bus, the 64KB RAM module needs to be split into two memory banks each of size 64KB/2 = 32KB). (2) Each memory bank has 32K different memory locations. Hence, it requires 15 address lines (32K =25 x 210 = 215). (3) The address bus of the 8086 (20 address lines A19-A0) will be interfaced to each memory bank as follows: The least significant address lines A15-A1 are used to address memory locations in memory chip as shown in Figure 7. The most significant address lines A19-A16 are used to select the memory module starting at address …… as shown in Figure 7. The address line A0 and BHE’ signal are used to select even byte, odd byte or both as shown in Table 1. A19 A18 A17 A16 A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 1 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 decoding addressing even byte (4) The control-bus of the 8086 is interfaced to the SRAM as follows: Decode the M/IO’, RD’, and WR’ signals to generate 4 signals Memory Read (MEMR’), Memory Write (MEMW’), I/O Read (IOR’) and I/O Write (IOW’) as shown in Figure 2. Connect MEMR’ to OE’ and MEMW’ to WE’ as shown in Figure 7. (5) The data-bus of the 8086 is interfaced to the SRAM (See Figure 7) by connecting: The buffered data lines D7-D0 to input/output lines (I/O7-I/O0) of the even SRAM. The buffered data lines D15-D8 to input/output lines (I/O7-I/O0) of the odd SRAM. 32Kx8 32Kx8 A1-A15 A0-A14 A0-A14 A16-A19 Figure 6: Memory interface of example 5 Example 6: Show how to interface a (64K x 8) SRAM chip(s) to a 386/486 processor. Interface 80386 Microprocessor 64Kx8 SRAM (1) Because the 386/486 has a 32-bit data bus, four SRAM chips are required (four memory banks 4x64KB = 256KB). (2) The memory space of the 386/486 processor is 4GB which consists of 4GB/256 KB = 232/218 = 214 = 16K different address ranges each of size 256K as shown in Figure 7. (3) We can map the each one of the four SRAM chips to one of these address ranges. (4) The SRAM chip has 64K different memory locations. Hence, it requires 16 address lines (64K=26x210 =216). (5) The address bus of the 386/486 (32 address lines) will be interfaced to the SRAM as follows: The least significant address lines A17-A2 are used to address memory locations in the SRAM chip as shown in Figure 7. The most significant address lines A31-A18 are used to select the required address range in the memory space of the 386/486 (i.e. select the four SRAM chips) as shown in Figure 7. The A0 and A1 address lines, are not present, instead, the four byte enable signals BE3-BE0 are used to select memory banks. A31 … decoding A18 A17 … A2 addressing A1 A0 x x (6) The control-bus of the 386/486 is interfaced to the SRAM as follows: Decode the M/IO’, RD’, and WR’ signals to generate 4 signals Memory Read (MEMR’), Memory Write (MEMW’), I/O Read (IOR’) and I/O Write (IOW’) as shown in Figure 2. Connect MEMR’ to OE’ and MEMW’ to WE’ as shown in Figure 7. (7) The data-bus of the 386/486 is interfaced to the SRAM by connecting: The buffered data lines D7-D0 to input/output lines (I/O7-I/O0) of SRAM-A. The buffered data lines D15-D8 to input/output lines (I/O7-I/O0) of SRAM-B. The buffered data lines D23-D16 to input/output lines (I/O7-I/O0) of SRAM-C. The buffered data lines D31-D24 to input/output lines (I/O7-I/O0) of SRAM-D. Figure 7: Memory interface of example 6 Example 7: Describe the decoder required to map the interface in the previous slide to the "bottom" of physical memory (that is, address 00000H). A31 A18A17 A2A1A0 Starting 0000 0000 0000 0000 0000 0000 0000 00XX Address Ending 0000 0000 0000 0011 1111 1111 1111 11XX Address A18 A19 A20 A21 A22 A23 A24 A25 A26 A27 A28 A29 A30 A31 Figure 8: Address decoder of example 7 Example 8: Show how to interface a (64K x 8) SRAM chip(s) to a Pentium/Pentium Pro processor. Interface Pentium Microprocessor 64Kx8 SRAM (1) Because the Pentium processors have 64-bit data buses, 8 memory chips (banks) will be required in the interface, providing a total memory capacity of 512K. (2) Like the 386 and 486, byte enable signals (BE7-BE0) are provided to select the appropriate chips. (3) The 16 low-order address lines A3-A18 are wired in parallel to each memory chip. (4) The decoder is then required to examine the remaining 13 address lines A19-A31. A31 … decoding A19 A18 … A3 addressing A2 A1 x x A0 x Figure 8:Memory interface of example 8 An address decoder is a circuit that examines decoding address lines and enables the memory for a specified range of addresses. This is an important part of any memory design, as one block of memory must not be allowed to overlap another. Address decoding techniques can be classified based on two categories: −(1)Type of Decoder Hardware (a) Logic Gates (b) Block Decoder (c) Programmable Array Logic (PAL) Decoder −(2) Size of Address Decoding Lines (a) Full Address Decoding (b) Partial Address Decoding Logic gates such as AND, OR, NOT, NAND, and NOR can be used to implement the function of an address decoder. For example, a two-input NAND gate recognizes the input pattern 11 and produces an active-low output only when this input combination is applied. A two-input AND provides a similar function but produces an active-high output indication. OR and NOR gates can also be used as decoders when their alternate (active-low input) logic symbols are used. The four possible logic gate decoder combinations are shown in Figure 9. Figure 9: The four possible logic gate decoder combinations Example 9: Design a decoder for the 8086 SRAM memory interface such that the memory is mapped to the address range 00000-1FFFFH. Figure 10: Address decoders of Example 9 When decoding larger sizes of memory with many memory chips, logic gate decoders become unpractical. In such cases, block decoders (such as 74LS138 3to-8 line decoder) are used for memory address decoding. A decoder is a combinational circuit that converts binary information from n input lines to a maximum of 2n unique output lines. The connection diagram, function table, and logic diagram of the 74LS138 decoder are shown in Figures 11, 12 and 13. Figure 11: Connection diagram of the 74LS13 decoder Figure 12: Function table of the 74LS13 decoder Figure 13: Logic diagram of the 74LS13 decoder Example 10: Show how to interface a 386 processor to a memory of size 128MB starting at address 0000000H using a 4MBx8 SRAM chips and a block decoder. −(1) Since the 386 requires 4 memory banks, i.e., 4 SRAM chips are needed (1 Module = 4 x 4MB = 16MB). −(2) For a memory of size 128MB, we need to use 128MB/16MB = 8 modules. −(3) We need 22 address lines (4MB = 22 x 220 = 222) to address memory location within one SRAM chip. −(4) We need 3 address lines (8 = 23) to select one memory module out of 8 modules. −(5) We need 5 address lines (4GB/128MB=22x230/27x220 = 232/227=25) to enable one memory range out of 32 memory ranges. These five lines must be low to enable the required memory range These three lines select one of eight memory modules These 22 lines select one byte within each 4 MB SRAM on each memory module Figure 14: Address partitioning of Example 10 These four lines select byte, word, or doub1eword (via the four SRAM chips) on each memory module Figure 15: Memory interface of Example 10 In this technique, all unused address lines are decoded to generate chip select. Every unused line has a particular value either 0 or 1. Each addressable location within the memory components responds to only a single unique address. All memory system designs seen so far use this type of address decoding. In this technique, only a subset of unused address lines is used to generate chip select. The values of un-decoded address bits are considered as don't care for the memory modules. Thus, each address location may be selected by more than one address combination. The advantage of this type of address decoding is that it results in reduced hardware for the address decoder. Example 11: Consider 4 SRAM modules (M0, M1, M2 and M3) each of size 4KB. −Assume that the four modules start at addresses 34000H, 36000H, 3C000H and 3F000H respectively. −Show how to interface these four memory modules to an 8086 microprocessor using the following address decoding methods: (a) Full decoding using NAND gates. (b) Partial decoding using NAND gates. (c) Full decoding using a decoder. (d) Partial decoding using a decoder. (1) Because the 8086 has a16-bit data bus, each 4KB module needs to be split into 2 memory banks each of size 4KB/2 = 2KB. (2) Each memory bank has 2K different memory locations. Hence, it requires 11 address lines (2K =21 x 210 = 211). (3) The address bus of the 8086 (20 address lines A19-A0) will be interfaced as follows: The least significant address lines A11-A1 are used to address memory locations in each memory chip. The most significant address lines A19-A12 are used to select the memory modules. The address line A0 and BHE’ signal are used to select even byte, odd byte or both. (4) The control-bus of the 8086 is interfaced to the SRAM as follows: Decode the M/IO’, RD’, and WR’ signals to generate 4 signals Memory Read (MEMR’), Memory Write (MEMW’), I/O Read (IOR’) and I/O Write (IOW’) . Connect MEMR’ to OE’ and MEMW’ to WE’ as shown in Figure 16. (5) The data-bus of the 8086 is interfaced to the SRAM (See Figure 16) by connecting: The buffered data lines D7-D0 to input/output lines (I/O7-I/O0) of the even SRAM. The buffered data lines D15-D8 to input/output lines (I/O7-I/O0) of the odd SRAM. All steps described above are common for the four types of address decoding requested in Example 10 (a-d). These decoding technique differ in the design of the address decoder shown as a box labeled “Decoder” in Figure 16. The details of the four address decoding techniques will be shown in the next slides. 2Kx8 A1-A11 A0-A12 2Kx8 A0-A12 A12-A19 Figure 16: Memory interface of example 11 Full Decoding Using NAND Gates: Partial Decoding Using NAND Gates: (1) Ignore common address lines (A19-A16 , A14). (2) Use the minimum number of remaining address lines (A15 , A13 , A12) as inputs to the NAND gates (3) Since A15 and A13 are enough to distinguish the three modules, these two address lines are used with the NAND gates. common bits Full Decoding Using a Decoder: (1) Use common address lines (A19-A16 , A14) to enable the decoder. (2) Use the remaining address lines (A15 , A13 , A12) as input to the decoder (3) Since 3 address lines are used as inputs to the decoder, we need a 3x8 decoder. (4) Connect memory select lines to the proper outputs of the decoder. common bits Partial Decoding Using a Decoder: (1) Ignore common address lines (A19-A16 , A14) . (2) Use the minimum number of remaining address lines (A15 , A13 , A12) as input to the decoder . (3) Since A15 and A13 are enough to distinguish the three modules, these two address lines are used as inputs to the decoder. (4) Since 2 address lines are used as inputs to the decoder, we need a 2x4 decoder. (5) Connect memory select lines to the proper outputs of the decoder. common bits