Week 1 PowerPoint - Michael G. Morrow

advertisement

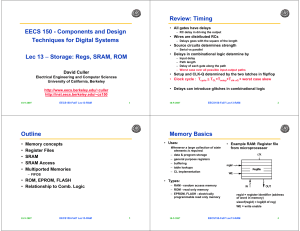

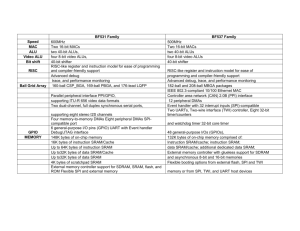

ECE 353 Introduction to Microprocessor Systems Week 9 Michael G. Morrow, P.E. Topics Memory technologies Organization and operation of typical SRAM, EPROM and flash memory devices Memory subsystem design Address decoder implementation SRAM timing characteristics Memory Terminology How could we classify memory devices? Read-Only Memory (ROM) In common usage, ROM is memory that is nonvolatile. Random-Access Memory (RAM) The time required to access any memory location is the same – i.e. it does not need to be accessed in a specific order. In common usage, RAM is memory that can be read or written with equal ease. Memory Technologies ROM (non-volatile) Masked ROM Field programmable EPROM OTP PROM (fuse or EPROM) Electrically erasable EEPROM (or E2PROM) Flash memory RAM (volatile) SRAM DRAM Pseudo-SRAM Emerging memory technologies Memory Organization Logical organization Organization as seen looking at the device from the outside Linear array of registers (memory locations) Width – number of bits in each memory location Depth – number of memory locations Usually written as depth x width (i.e. 32k x 8) Physical organization Different physical organizations can be used to implement the same logical organization Physical organization affects performance and cost SRAM Interfaces RAM with 3 control inputs /CS, /OE, /WE Read Write aka “Intel style” /CS /WE /OE internal w rite signal internal read signal RAM with 2 control inputs E (CS), R/W (or /WE) E R/W aka “Motorola style” internal w rite signal internal read signal SRAM Organization Logical Organization Typically 1, 4 , 8 or 16 bit widths Physical Organization Rectangular bit array Two-level decoding (row and column) Characteristic delays and timing requirements are specified in memory devices datasheet (Example) NV-SRAM Uses an alternate power source to maintain SRAM when system power is off Requires logic to switch power sources and prevent spurious writes during power-up/power-down EPROM Electrically programmable, non-volatile Requires UV light to erase Quartz window in package Floating polysilicon gate avalanche injection MOS transistor (FAMOS) Operation Programmer loads device out-of-circuit OTP EPROMs eliminate quartz window EEPROMs are electrically erasable Byte-erasable / writeable Low-density JEDEC Packages Flash Memory Actually Flash EEPROM, commonly just called flash memory Characteristics Technologies Endurance Blocking, programming and erasing Applications ROM replacement GP NV-RAM Solid-state disk (flash-disk) Example Memory Subsystem Design Memory banks Increasing memory width Increasing memory depth Increasing memory width and depth Address decoding Exhaustive (full) vs. partial (reduced) decoding Boundaries n If address is a 2 boundary, then what is the result of (address AND (2n-1))? We normally decode memory devices to be aligned on boundaries at least as large as they are Memory Architectures Wide (n-byte) buses Addressing effects Byte transfer support Data lanes Control signals Bus resizing Static Configurable Dynamic Memory Subsystems Review What is the purpose of an address decoder circuit, and where does its output usually get connected? What is exhaustive decoding, and what effects does it have? What is partial decoding, and what effects does it have? SRAM Timing Characteristics An SRAM device has key timing parameters specified for the read cycle. tAA – address access time tRDHA – data valid after address changes tACS – chip select access time tRHCS – data valid after chip select tCHZ – time until device floats bus tOE – output enable access time tOHZ – time until device floats bus tRC – read cycle time The write cycle has a complementary set of specifications. 7C1046 SRAM 27C512 EPROM HM624100HC SRAM SRAM Timing Compatibility In order to ensure that we will be able to reliably read and write the memory device, we need to ensure that the processor system bus interface is compatible with the memory device. This is accomplished by analyzing the timing for all relevant parameters of both the processor and memory, and ensuring that the operations can be completed reliably. Wrapping Up Quiz #2 will be held on Thursday 3/29 at 7:15-8:30pm in 2255EH Covers educational objectives for modules 3 and 4 (weeks 5 through 8) Single 3x5 card with original handwritten notes No calculators Instruction set references and any needed datasheets will be provided Reading for next week Supplement #3, review chapter 9 in text JEDEC Standard Packages http://www.jedec.org/download/search/3_07_05R12.pdf Flash Blocks Flash Memory Application: Disk-on-Key Up to 64GB nonvolatile storage And climbing No battery or power supply Specifications: Data retention up to 10 years Erase cycles: 1,000,000 times Shock resistance: 1000 G (maximum) RAM Read – 3 control signals Ax Dx /CS /WE /OE RAM Write – 3 control signals Ax Dx /CS /WE /OE Increasing Memory Depth A15 A0 A14 D7 D7 D0 D0 A0 CE A14 D7 D0 CE A0 CE Extending Depth Increasing Memory Width A15 A0 A15 D3 D7 D0 D0 A0 CE A15 D3 D0 CE A0 CE Extending Width Increasing Memory Depth & Width A14 A15 D3 D0 D7 A0 D0 CE A0 A14 D3 D0 A0 CE A14 D3 D0 A0 CE CE A14 D3 D0 A0 CE Extending Width and Depth