ENGR 2720 Chapter 06

advertisement

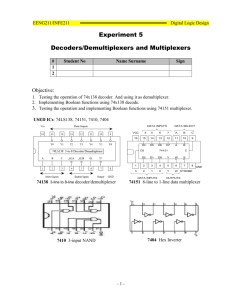

Chapter 6 Combinational Logic Functions 1 Chapter 6 Homework 6.1, 6.5, 6.7a&b, 6.15, 6.19a&b, 6.21, 6.23, 6.29, 6.45 2 Basic Decoder • Decoder: A digital circuit designed to detect the presence of a particular digital state. • Can have one output or multiple outputs. • Example: 2-Input NAND Gate detects the presence of ‘11’ on the inputs to generate a ‘0’ output. 3 Single-Gate Decoders • Uses single gates (AND/NAND) and some Inverters. • Example: 4-Input AND detects ‘1111’ on the inputs to generate a ‘1’ output. • Inputs are labeled D3, D2, D1, and D0, with D3 the MSB (most significant bit) and D0 the LSB (least significant bit). 4 Single-Gate Decoders D3 D2 D1 D0 Y = D3 D2D1D0 D3 D2 D1 D0 Y = (D3 D2D1D0)’ 5 Single-Gate Examples • If the inputs to a 4-Input NAND are given as D1, D2, D3, D4, then the NAND detects the code 0001. The output is a 0 when the code 0001 is detected. • This type of decoder is used in Address Decoding for a PC System Board. 6 Multiple Output Decoders • Decoder circuit with n inputs can activate m = 2n load circuits. • Called a n-line-to-m-line decoder, such as a 2-to-4 or a 3-to-8 decoder. • Usually has an active low enable that enables the decoder outputs. G 7 2-to-4 Decoder 8 3-to-8 Decoder 9 Truth Table for a 3-to-8 Decoder G D2 D1 D0 Y0 Y1 Y2 Y3 Y4 Y 5 Y6 Y7 1 0 0 0 X 0 0 0 X 0 0 1 X 0 1 0 1 0 1 1 1 1 0 1 1 1 1 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 10 74138 3-to-8 Decoder 11 74138 3-to-8 Decoder 12 Simulation • Simulation: The verification of a digital design using a timing diagram before programming the design in a CPLD. • Used to check the Output Response of a design to an Input Stimulus using a timing diagram. 13 Simulation 14 VHDL Binary Decoder • Use select signal assignment statements constructs or conditional signal assignment statements constructs. 15 2-to-4 Decoder VHDL Entity • Using a select signal assignment statement: LIBRARY ieee; USE ieee.std_logic_1164.ALL; ENTITY decode3 IS PORT( d : IN STD_LOGIC_VECTOR (1 downto 0); y : OUT STD_LOGIC_VECTOR (3 downto 0)); END decode3; 16 Selected Signal Entity • In the previous slide, the Entity used a STD LOGIC Array for Inputs and Outputs. • The Y : OUT STD_LOGIC_VECTOR(3 downto 0) is equal to Y3, Y2, Y1, Y0. • The STD_LOGIC Data Type is similar to BIT but has added state values such as Z, X, H, and L instead of just 0 and 1. 17 Selected Signal Assignments • Uses a VHDL Architecture construct called WITH SELECT. • Format is: – WITH (signal input(s)) SELECT. – Signal input states are used to define the output state changes. 18 2-to-4 Decoder VHDL Architecture ARCHITECTURE decoder OF decode3 IS BEGIN WITH d SELECT y <= “0001” WHEN “00”, “0010 WHEN “01”, “0100” WHEN “10”, “1000” WHEN “11”, “0000” WHEN others; END decoder; 19 Decoder Architecture • The decoder Architecture used a SELECT to evaluate d to determine the Output y. • Both d and y are defined as an Array (or bus or vector) Data Type. • The last state for WHEN OTHERS is added for the other logic states (Z, X, H, L, etc.). 20 Seven-Segment Displays • Seven-Segment Display: An array of seven independently controlled LEDs shaped like an 8 that can be used to display decimal digits. 21 Seven-Segment Displays 22 Seven-Segment Displays 23 Common Anode Display • Common Anode Display (CA): A sevensegment display where the anodes of all the LEDs are connected together to VCC and a ‘0’ turns on a segment (a to g). 24 Common Cathode Display • Common Cathode Display (CC): A sevensegment display where all the cathodes are connected and tied to ground, and a ‘1’ turns on a segment. 25 Common Cathode/Anode Display 26 Common Anode Display 27 Seven-Segment Decoder/Driver – 1 • Receives a BCD (Binary Coded Decimal) 4-Bit input, outputs a BCD digit 0000 – 1001 (0 through 9). • Generates Outputs (a–g) for each of the display LEDs. • Requires a current limit series resistor for each segment. 28 Seven-Segment Decoder/Driver – 2 • Decoders for a CC-SS have active high outputs while decoders for a CA-SS have active low outputs (a to g). • The outputs generated for the binary input combinations of 1010 to 1111 are “don’t cares”. • The decoder can be designed with VHDL or MSI Logic (7447, 7448). 29 SS Decoder/Driver Truth Table Digit 0 1 2 3 4 5 6 7 8 9 D3 D2 D1 D0 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 a 0 1 0 0 1 0 1 0 0 0 b 0 0 0 0 0 1 1 0 0 0 c 0 0 1 0 0 0 0 0 0 0 d 0 1 0 0 1 0 0 1 0 1 e 0 1 0 1 1 1 0 1 0 1 f 0 1 1 1 0 0 0 1 0 0 g 1 1 0 0 0 0 0 1 0 0 30 SS Decoder/Driver Truth Table 31 Decoder/Driver Entity (CA) ENTITY bcd_7seg IS PORT( d3, d2, d1, d0 a, b, c, d, e, f, g END bcd_7seg; : IN BIT; : OUT BIT; 32 Decoder/Driver Architecture – 1 ARCHITECTURE seven_segment OF bcd_7seg IS SIGNAL input : BIT_VECTOR (3 downto 0); SIGNAL output : BIT_VECTOR (6 downto 0); BEGIN input <= d3 & d2 & d1 & d0; -- Uses two intermediate signals called input and output (internal no pins) -- Creates an array by using the concatenate operator (&) In this case input(3) <= d3, input(2) <= d2, etc. 33 Decoder/Driver Architecture – 2 WITH input SELECT output <= “0000001” WHEN “0000”, “1001111” WHEN “0001”, “0010010” WHEN “0010”, “0000110“ WHEN “0011”, • • • • • • • • • “1111111” WHEN others; 34 Decoder/Driver Architecture – 3 a <= output(6); b <= output(5); c <= output(4); d <= output(3); e <= output(2); f <= output(1); g <= output(0); END seven_segment 35 SS VHDL File Description • In the preceding example file, a concurrent select signal assignment was used (WITH (signals) SELECT. • The intermediate output signals were mapped to the segments (a to g). • Example: when Input (D3 – D0) is 0001, the decoder sets a=d=e=f=g=1, b=c=0. 36 Ripple Blanking • Ripple Blanking: A technique used in a multiple-digit display that suppresses leading/trailing zeros but allows internal zeros to be displayed. • Uses a RBI (active-LOW) Input and a RBO (active-LOW) output. • When D0 – D3 = 0000 and RBO = 0, the display is blank. 37 Ripple Blanking • When D0 – D3 = 0000 and RBI = 1, the display shows a ‘0’ (zero). • If RBI= 1 or D0 – D3 0000, then RBO= 1. • To suppress leading zeros, connect RBI of MS Digit to Gnd, and RBO to RBI of the next least significant display. 38 Ripple Blanking 39 Sequential Process in VHDL • A VHDL Process is a construct that encloses sequential statements that are executed when a signal in a sensitivity list changes. 40 Sequential Process Basic Format • Basic Format: PROCESS(Sensitivity List) BEGIN Sequential Statements; END PROCESS; 41 Ripple Blanking VHDL ENTITY sevsegrb IS PORT( - - Use separate I/O’s, not bus nRBI, d3, d2, d1, d0: IN BIT; a, b, c, d, e, f, g, nRBO : OUT BIT; END sevsegrb; 42 Ripple Blanking VHDL ARCHITECTURE seven_segment OF sevsegrb IS SIGNAL input : BIT_VECTOR (3 downto 0); SIGNAL output : BIT_VECTOR (6 downto 0); BEGIN input <= d3 & d2 & d1 & d0; 43 Ripple Blanking VHDL -- process statement PROCESS (input, nRBI) BEGIN IF(nRBI = ‘0’ and input = “0000”) THEN output <= “1111111”; - - 0 supressed nRBO <= ‘0’; - - Next 0 suppressed ELSE nRBO <= ‘1’; - - Next 0 displayed 44 Ripple Blanking VHDL CASE input IS WHEN “0000” => output <= “0000001”; - - A zero is displayed. WHEN “0001” => output <= “1001111”; - - A one is displayed. • • • • • • • • • • • • WHEN others => output <= “1111111”; - - Blank. END CASE END IF; END PROCESS assign_out; 45 Encoders • Encoder: A digital circuit that generates a specific code at its outputs in response to one or more active inputs. • It is complementary in function to a decoder. • Output codes are usually Binary or BCD. 46 8 to 3 bit Encoder 47 8-to-3 Encoder Truth Table D7 0 0 0 0 0 1 D6 0 0 0 0 0 0 Active High Inputs D5 D4 D3 D2 D1 0 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 0 1 0 0 0 1 0 0 0 0 0 0 0 0 D0 1 0 0 0 0 Q2 0 0 0 0 1 0 1 Q1 Q0 0 0 0 1 1 0 1 1 0 0 1 1 48 Priority Encoders • Priority Encoder: An encoder that generates a code based on the highestpriority input. • For example, if input D3 = input D5, then the output is 101, not 011. D5 has a higher priority than D3 and the output will respond accordingly. 49 Priority Encoder Equations Q2 D7 D6 D5 D4 Q1 D7 D6 D5 D4 D3 D5 D4 D2 Q0 D7 D6 D5 D6 D4 D3 D6 D4 D2 D1 50 Priority Encoder VHDL Entity -- hi_pri8a.vhd ENTITY hi_pri8a IS PORT( d q END hi_pri8a; : IN BIT_VECTOR (7 downto 0); : OUT BIT_VECTOR (2 downto 0)); 51 Priority Encoder VHDL Architecture ARCHITECTURE a OF hi_pri8a IS BEGIN -- Concurrent Signal Assignments q(2) <= d(7) or d(6) or d(5) or d(4); q(1) <= q(0) END a; <= d(7) or d(6) or ((not d(5)) and (not d(4)) and d(3)) or ((not d(5)) and (not d(4)) and d(2)); -- in a similar fashion 52 Another VHDL Encoder – 1 -- hi_pri8b.vhd ENTITY hi_pri8a IS PORT( d q END hi_pri8b; : IN BIT_VECTOR (7 downto 0); : OUT INTEGER RANGE 0 TO 7); 53 Another VHDL Encoder – 2 ARCHITECTURE a OF hi_pri8b IS BEGIN encoder; q <= 7 WHEN d(7) = ‘1’ ELSE 6 WHEN d(6) = ‘1’ ELSE 5 WHEN d(5) = ‘1’ ELSE 4 WHEN d(4) = ‘1’ ELSE 3 WHEN d(3) = ‘1’ ELSE 2 WHEN d(2) = ‘1’ ELSE 1 WHEN d(1) = ‘1’ ELSE 0; END a; 54 Basic Multiplexers (MUX) • (MUX): A digital circuit that directs one of several inputs to a single output based on the state of several select inputs. • A MUX is called a m-to-1 MUX. • A MUX with n select inputs will require m = 2n data inputs (e.g., a 4-to-1 MUX requires 2 select inputs S1 and S0). 55 Basic Multiplexers (MUX) 56 Basic Multiplexers (MUX) 57 4-to-1 Multiplexers Truth Table S1 0 0 1 1 S0 0 1 0 1 Y D0 D1 D2 D3 58 Multiplexer Logic • Boolean expression for a 4-to-1 MUX is Y D0 S1 S0 D1 S1 S0 D2 S1 S0 D3 S1 S0 • This expression can be expanded to any size MUX so the VHDL architecture could use a very long concurrent Boolean statement. 59 Double Subscript Notation • Naming convention in which variables are bundled in numerically related groups, the elements of which are themselves numbered. • The first subscript identifies the group that a variable belongs to (D01, D00). • The second subscript indicates which element of the group a variable represents. 60 4-bit Bus MUX 61 Truth Table for a 4-to-1 4-bit Bus MUX S1 0 0 1 1 S0 0 1 0 1 Y3 Y2 Y1 Y0 D03 D02 D01 D00 D13 D12 D11 D10 D23 D22 D21 D20 D33 D32 D31 D30 62 VHDL Constructs For MUXs • The following three VHDL constructs can be used to describe the Multiplexer: – Concurrent Signal Assignment Statement – Select Signal Assignment Statement – CASE Statement 63 PROCESS and Sensitivity List • PROCESS: A VHDL construct that contains statements that are executed if a signal in its sensitivity list changes. • Sensitivity list: A list of signals in a PROCESS statement that are monitored to determine whether the Process should be executed. 64 Case Statement • A case statement is a VHDL construct in which there is a choice of statements to be executed, depending on the value of a signal or variable. 65 Case VHDL Template CASE __expression IS WHEN __constant_value => __statement; __statement; WHEN __constant_value => __statement; __statement; WHEN OTHERS => __statement; __statement; END CASE; 66 MUX 4-to-1 VHDL – 1 • Basic Entity declaration for a 4-to-1 MUX: ENTITY mux4case IS PORT( d0, d1, d2, d3 s y END mux4case; : IN BIT; : IN BIT_VECTOR (1 downto 0); : OUT BIT); 67 MUX 4-to-1 VHDL – 2 ARCHITECTURE mux4to1 OF mux4case IS BEGIN -- Monitor select inputs and execute if they change PROCESS(s) BEGIN CASE s IS 68 MUX 4-to-1 VHDL – 3 WHEN "00" WHEN "01" WHEN "10" WHEN "11" WHEN others END CASE; END PROCESS; END mux4to1; => => => => => y y y y y <= <= <= <= <= d0; d1; d2; d3; '0'; 69 Multiplexer Applications • Used in directing multiple data sources to a single processing element such as multiple CD Player Streams to a DSP. • Used in Time Division Multiplexing (TDM) by the Phone Service to multiplex multiple voice channels on a single coax line (or fiber). 70 Multiplexer Applications Used in directing multiple data sources to a single processing element such as multiple CD Player Streams to a DSP. 71 Multiplexer Applications Used in Time Division Multiplexing (TDM) by the Phone Service to multiplex multiple voice channels on a single coax line (or fiber). 72 Time Division Multiplexing (TDM) • Each user has a specific time slot in a TDM data frame. Each frame has 24 users. • TDM requires a time-dependent (counter) source to synchronize the select lines. • Each user’s time slot repeats on the next frame for more data. • The links are called T-Carriers (such as a T1 Line). 73 TDM Data Streams • Two methods in which data is transmitted: – Bit Multiplexing: One bit is sent at a time from the channel during the channel’s assigned time slot – Word Multiplexing: One byte is sent at a time from the channel during the channel’s assigned time slot 74 TDM Data Streams 75 TDM Data Streams 76 Demultiplexer Basics • Demultiplexer: A digital circuit that uses a decoder to direct a single input (from a MUX) to one of several outputs. • A DEMUX performs the reverse operation of a MUX. • The selected output is chosen by the Select Inputs (as in a MUX). 77 Demultiplexer Basics • Designated as a 1-to-n DEMUX that requires m select inputs such that n outputs = 2m select inputs. • 1-to-4 DEMUX Equations: Y( 0 ) D0 S1 S0 ; Y( 1) D0 S1 S0 ; Y( 2 ) D0 S1 S0 ; Y( 3 ) D0 S1 S0. • They are similar to a MUX and can be designed using CASE Statements. 78 Demultiplexer Basics 79 Demultiplexer Basics 80 Demultiplexer Basics 81 Demultiplexer VHDL Entity ENTITY dmux8 IS PORT( s : IN STD_LOGIC_VECTOR (2 downto 0); d : IN STD_LOGIC; y : OUT STD_LOGIC_VECTOR (0 to 7)); END dmux8; 82 Demultiplexer VHDL Architecture ARCHITECTURE a OF dmux8 IS SIGNAL inputs : STD_LOGIC_VECTOR (3 downto 0); BEGIN inputs <= d & s; WITH inputs select Y <= “01111111” WHEN “0000”, “10111111” WHEN “0001”, • • • • • • “11111111” WHEN others; END a; 83 Demultiplexer VHDL Architecture 84 Analog MUX/DEMUX • Uses a CMOS Switch or Transmission Gate that will allow a signal to Pass in two directions for + and – Voltages. • Some commercial types such as a CD4066 or 74HC4066. • Multiplexes 4 CMOS Switches to a single output (Y) for analog multiplexing. 85 Analog MUX/DEMUX 86 Analog MUX/DEMUX 87 Magnitude Comparators • Magnitude Comparator: A digital circuit that compares two n-Bit Binary Numbers and indicates if they are equal or which is greater. • A very simple One-Bit Magnitude Comparator is the Two-Input XNOR Gate: – When both inputs are equal, the output is a 1; if they are not, it is a 0. 88 2-Bit Comparator A1 B1 AEQB A0 B0 89 2-Bit Magnitude Comparator A1 B1 AEQB A0 B0 AGTB ALTB 90 Magnitude Comparators • Multiple Bit Comparisons AEQB ( An-1 B n-1 ) • ( An- 2 B n- 2 ) . • Also adds A > B (AGTB) and A < B (ALTB) Outputs. • For A > B, start with the MSB: – If An–1 > Bn–1, then AGTB = 1 • If not, then try the next most significant bit. 91 4-Bit Magnitude Comparator A3 B3 ALTB A2 B2 A1 B1 A0 B0 AEQB AGTB 92 VHDL 4-Bit Magnitude Comparator ENTITY compare4 IS PORT( a, b RANGE 0 to 15; agtb, aeqb, altb END compare4; : IN INTEGER : OUT STD_LOGIC); 93 VHDL 4-Bit Magnitude Comparator ARCHITECTURE a OF compare4 IS SIGNAL compare :STD_LOGIC_VECTOR (2 downto 0); BEGIN PROCESS (a, b) BEGIN IF a<b THEN compare <= “110”; ELSIF a = b THEN compare <= “101”; 94 VHDL 4-Bit Magnitude Comparator ELSIF a > b THEN compare <= “011”; ELSE compare <= “111”; END IF; agtb <= compare(2); aeqb <= compare(1); altb <= compare(0); END PROCESS END a; 95 Temperature Comparator 96 Parity Basics • Parity: A digital system that checks for errors in a n-Bit Binary Number or Code. • Even Parity: A parity system that requires the binary number and the parity bit to have an even # of 1s. • Odd Parity: A parity system that requires the binary number and the parity bit to have an Odd # of 1s. 97 Parity Basics • Parity Bit: A bit appended on the end of a binary number or code to make the # of 1s odd or even depending on the type of parity in the system. • Parity is used in transmitting and receiving data by devices in a PC called UARTs, that are on the COM Port. • UART = Universal asynchronous Receiver/Transmitter 98 Parity Basics 99 Parity Calculation • N1 = 0110110: – It has four 1s (an even number). – If Parity is ODD, the Parity Bit = 1 to make it an odd number (5). – If Parity is EVEN, the Parity Bit = 0 to keep it an even number (4). • N2 = 1000000: – One 1 in the data. – Podd = 0. – Peven = 1. 100 Parity Generation HW • A basic two-bit parity generator can be constructed from a XOR Gate. • When the two inputs are 01 or 10, the output is a 1 (so this is even parity). • When the two inputs are 00 or 11, the output is a 0. • For a parity generator of n bits, add more gates. 101 Parity Generator HW • Cascading a long chain of XOR gates could cause excessive propagation delays. • To check for a Parity error, the receiver (RX) just generates a new Parity Bit (P1) based on the received parallel data and then compares it to the parity bit transmitted (P2). 102 Parity Generator HW • If there is an error, the two bits (P1 and P2) will not be equal, and we can use a two-bit magnitude comparator to check this (an XOR gate). • This check is called syndrome. – If there are no errors, the syndrome output (Perr) is 0. • Parity is not a foolproof system. – If two bits are in error, the error is not detected. 103 4-Bit Parity Generator 104 VHDL GENERATE Statement __generate_label: FOR __index_variable IN __range GENERATE __statement; __statement; END GENERATE; 105 4-Bit Parity VHDL Code – 1 LIBRARY ieee; USE ieee.std_logic1164.ALL; ENTITY parity4_gen IS PORT( d : IN STD_LOGIC_VECTOR (0 to 3); pe ; OUT STD_LOGIC); END parity4_gen; 106 4-Bit Parity VHDL Code – 2 ARCHITECTURE parity OF parity4_gen IS SIGNAL p : STD_LOGIC_VECTOR (1 to 3); BEGIN p(1) <= d(0) xor d(1); parity_generate: FOR i IN 2 to 3 GENERATE p(i) <= p(i-1) xor d(i); END GENERATE; pe <= p(3); END parity; 107 BCD D9 – D0 = 0100001111 BCD # = ? 108 Problem 6.15a D9 – D0 = 0101001011 Q3 – Q0 = 1000 (810) 109 Problem 6.15b D9 – D0 = 1000000001 Q3 – Q0 = 1001 (910) 110 Problem 6.15c D9 – D0 = 1101001011 Q3 – Q0 = 1001 (910) 111 Put It All Together D C B A =1 =0 =0 =0 1 112