Chapter 6

advertisement

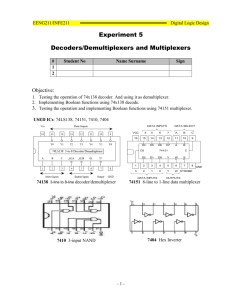

Chapter 6 Combinational Logic Functions Basic Decoder • Decoder: A digital circuit designed to detect the presence of a particular digital state. • Can have one output or multiple outputs. • For example, 74LS138, a 3 to 8 decoder. The connection diagram of 74LS138 is shown in next page. • Example: 2-Input NAND Gate detects the presence of ‘11’ on the inputs to generate a ‘0’ output. 2 The 74LS138 3 The 74LS138 4 Single-Gate Decoders • Uses single gates (AND/NAND) and some Inverters. • Example: 4-Input AND detects ‘1111’ on the inputs to generate a ‘1’ output. • Inputs are labeled D3, D2, D1, and D0, with D3 the MSB (most significant bit) and D0 the LSB (least significant bit). 5 Single-Gate Decoders 6 Single-Gate Examples • If the inputs to a 4-Input NAND are given as D1, D2, D3 , D4, then the NAND detects the code 0001. The output is a 0 when the code 0001 is detected. • This type of decoder is used in Address Decoding for a PC System Board. 7 Multiple Output Decoders • Decoder circuit with n inputs can activate m = 2n load circuits. • Called a n-line-to-m-line decoder, such as a 2-to-4 or a 3-to-8 decoder. • Usually has an active low enable G that enables the decoder outputs. 8 Truth Table for a 3-to-8 Decoder G D2 D1 D0 Y0 Y1 Y2 Y3 Y4 Y 5 Y6 Y7 1 X X X 1 1 1 1 1 1 1 1 0 0 0 0 0 0 1 0 1 1 0 1 1 1 1 1 • • • 0 0 0 1 • 0 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 • • • • • All outputs are high when G is high irrespective of the inputs 9 Truth Table for a 3-to-8 Decoder 10 Simulation • Simulation: The verification of a digital design using a timing diagram before programming the design in a CPLD. • Used to check the Output Response of a design to an Input Stimulus using a timing diagram. 11 Simulation A case with active-Low enable and active-High decoded outputs! 12 VHDL Binary Decoder • Use select signal assignment statements constructs or conditional signal assignment statements constructs. 13 2-to-4 Decoder VHDL Entity • Using a select signal assignment statement: LIBRARY ieee; USE ieee.std_logic_1164.ALL; ENTITY decode3 IS PORT( d : IN STD_LOGIC_VECTOR (1 downto 0); y : OUT STD_LOGIC_VECTOR (3 downto 0)); END decode3; 14 Selected Signal Entity • In the previous slide, the Entity used a STD LOGIC Array for Inputs and Outputs. • The Y : OUT STD_LOGIC_VECTOR(3 downto 0) is equal to Y3, Y2, Y1, Y0. • The STD_LOGIC Data Type is similar to BIT but has added state values such as Z (高阻抗), X(Forcing unknown;浮接), H, and L instead of just 0 and 1. 15 Selected Signal Assignments • Uses a VHDL Architecture construct called WITH SELECT. • Format is: – WITH (signal input(s)) SELECT. – Signal input states are used to define the output state changes. 16 2-to-4 Decoder VHDL Architecture ARCHITECTURE decoder BEGIN WITH d SELECT y <= “0001” WHEN “0010 WHEN “0100” WHEN “1000” WHEN “0000” WHEN END decoder; OF decode3 IS “00”, “01”, “10”, “11”, others; 17 Decoder Architecture • The decoder Architecture used a SELECT to evaluate d to determine the Output y. • Both d and y are defined as an Array (or bus or vector) Data Type. • The last state for WHEN OTHERS is added for the other logic states (Z, X, H, L, etc.; H:weak high, L:weak low). 18 Seven-Segment Displays • Seven-Segment Display: An array of seven independently controlled LEDs shaped like an 8 that can be used to display decimal digits. 19 Seven-Segment Displays 20 Seven-Segment Displays 21 Common Anode Display • Common Anode Display (CA;共陽極): A seven- segment display where the anodes of all the LEDs are connected together to VCC and a ‘0’ turns on a segment (a to g). • 由0點亮每一個segment 22 Common Cathode Display • Common Cathode Display (CC ;共陰極): A seven-segment display where all the cathodes are connected and tied to ground, and a ‘1’ turns on a segment. 23 Common Cathode Display 24 Common Anode Display 原講義誤植為Cathode 25 Seven-Segment Decoder/Driver – 1 • Receives a BCD (Binary Coded Decimal) 4-Bit input, outputs a BCD digit 0000 – 1001 (0 through 9). • Generates Outputs (a–g) for each of the display LEDs. • Requires a current limit series resistor for each segment. 26 Seven-Segment Decoder/Driver – 2 • Decoders for a CC-SS have active high outputs while decoders for a CA-SS have active low outputs (a to g). • The outputs generated for the binary input combinations of 1010 to 1111 are “don’t cares”. • The decoder can be designed with VHDL or MSI Logic (7447, 7448). 27 SS Decoder/Driver Truth Table Digit 0 1 2 3 4 5 6 7 8 9 D3 D2 D1 D0 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 a 0 1 0 0 1 0 1 0 0 0 b 0 0 0 0 0 1 1 0 0 0 c 0 0 1 0 0 0 0 0 0 0 d 0 1 0 0 1 0 0 1 0 1 e 0 1 0 1 1 1 0 1 0 1 f 0 1 1 1 0 0 0 1 0 0 g 1 1 0 0 0 0 0 1 0 0 28 SS Decoder/Driver Truth Table 29 Decoder/Driver Entity (CA) ENTITY bcd_7seg IS PORT( d3, d2, d1, d0 a, b, c, d, e, f, g END bcd_7seg; : IN BIT; : OUT BIT; 30 Decoder/Driver Architecture – 1 ARCHITECTURE seven_segment OF bcd_7seg IS SIGNAL input : BIT_VECTOR (3 downto 0); SIGNAL output : BIT_VECTOR (6 downto 0); BEGIN input <= d3 & d2 & d1 & d0; -- Uses two intermediate signals called input and output (internal no pins) -- Creates an array by using the concatenate operator (&) In this case input(3) <= d3, input(2) <= d2, etc. 31 Decoder/Driver Architecture – 2 WITH input SELECT output <= “0000001” WHEN “0000”, “1001111” WHEN “0001”, “0010010” WHEN “0010”, “0000110“ WHEN “0011”, • • • • • • • • • “1111111” WHEN others; 32 Decoder/Driver Architecture – 3 a <= output(6); b <= output(5); c <= output(4); d <= output(3); e <= output(2); f <= output(1); g <= output(0); END seven_segment 33 SS VHDL File Description • In the preceding example file, a concurrent select signal assignment was used (WITH (signals) SELECT. • The intermediate output signals were mapped to the segments (a to g). • Example: when Input (D3 – D0) is 0001, the decoder sets a=d=e=f=g=1, b=c=0. (點亮b和c;亦即數字1) 34 Ripple Blanking – 1 • Ripple Blanking: A technique used in a multiple-digit display that suppresses leading /trailing zeros but allows internal zeros to be displayed. • Uses a RBI (active-LOW) Input and a RBO (active-LOW) output. 35 Ripple Blanking – 2 • RBI (Ripple Blanking Input): Display inhibited if connected to low. 亦即用以控制此一位數為0 時是否可正常顯示0。此接腳為0時若輸入亦為 0,則此一0無法顯示,反之可正常顯示。 • RBO (Ripple Blanking Onput): 用以知會其他位 數之輸入為0時是否可正常顯示0。此訊號為 High表示通知其他位數為0時仍須正常顯示0; 亦即the case of internal zero 36 Ripple Blanking – 3 • When D0 – D3 = 0000 and RBI = 0, the display is blank. • When D0 – D3 = 0000 and RBI = 1, the display shows a ‘0’ (zero). • If RBI = 1 or D0 – D3 ≠ 0000, then RBO = 1. • RBI = 1,表示這是一個Internal digit 37 Ripple Blanking – 4 • To suppress leading zeros, connect RBI of MS Digit to Gnd, and RBO to RBI of the next least significant display. • 個位數之 RBI 必須接High,否則當整數部份為0時 小數點之前會全部無顯示(十位數之RBO空接即 可) 38 Ripple Blanking – 5 • To suppress trailing zeros, connect RBI of LS Digit to Gnd, and RBO to the RBI of the next most significant display. 39 9 RBI RBO 5 Output 1 RBO RBI RBO RBI 0 RBI RBO 0 RBO 4 RBI RBO RBI RBO RBO RBI RBO RBI Output 1 8 RBI RBO RBI 40 Sequential Process in VHDL • A VHDL Process is a construct that encloses sequential statements that are executed when a signal in a sensitivity list(觸發列)changes. • Process is itself a concurrent statement. 41 Sequential Process Basic Format • Basic Format: PROCESS(Sensitivity List) BEGIN Sequential Statements; END PROCESS; 42 Ripple Blanking VHDL – 1 ENTITY sevsegrb IS PORT( - - Use separate I/O’s, not bus nRBI, d3, d2, d1, d0 : IN BIT; a, b, c, d, e, f, g, nRBO : OUT BIT; END sevsegrb; 43 Ripple Blanking VHDL – 2 ARCHITECTURE seven_segment OF sevsegrb IS SIGNAL input : BIT_VECTOR (3 downto 0); SIGNAL output : BIT_VECTOR (6 downto 0); BEGIN input <= d3 & d2 & d1 & d0; 44 Ripple Blanking VHDL – 3 -- process statement PROCESS (input, nRBI) BEGIN IF(nRBI = ‘0’ and input = “0000”) THEN output <= “1111111”; - - 0 supressed nRBO <= ‘0’; - - Next 0 suppressed ELSE nRBO <= ‘1’; - - Next 0 displayed 45 Ripple Blanking VHDL – 4 CASE input IS WHEN “0000” => output <= “0000001”; - - A zero is displayed. WHEN “0001” => output <= “1001111”; - - A one is displayed. • • • • • • • • • • • • WHEN others => output <= “1111111”; - - Blank. END CASE; END IF; END PROCESS assign_out; 46 CASE Statement • In the RB Design, we replaced the Selected Signal Assignment (With Select) with a Case Statement to generate the outputs for the SS Display. • The Process Steps are evaluated in sequence: – First the IF statements, then the Case, and so on. 47 IF THEN ELSE • The IF THEN ELSE Statements were used for conditional testing of some inputs (the data and RBI). • IF the data is this value THEN do these statements ELSE do this. • This is a very simple statement that is used a great deal in sequential logic. 48 Encoders • Encoder: A digital circuit that generates a specific code at its outputs in response to one or more active inputs. • It is complementary in function to a decoder. • Output codes are usually Binary or BCD. 49 Priority Encoders • Priority Encoder: An encoder that generates a code based on the highestpriority input. • For example, if input D3 = input D5=High, then the output is 101, not 011. D5 has a higher priority than D3 and the output will respond accordingly. 50 8-to-3 Encoder Truth Table D7 0 0 0 0 0 D6 0 0 0 0 0 • Active High Inputs D5 D4 D3 D2 D1 0 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 0 1 0 0 0 1 0 0 0 • 1 0 0 0 0 0 0 D0 1 0 0 0 0 Q2 0 0 0 0 1 Q1 0 0 1 1 0 • Q0 0 1 0 1 0 0 1 1 1 51 8-to-3 Priority Encoder Truth Table D7 D6 D5 D4 D3 D2 D1 D0 Q2 Q1 Q0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 0 1 x 0 0 1 0 0 0 0 0 1 x x 0 1 0 0 0 0 0 1 x x x 0 1 1 0 0 0 1 x x x x 1 0 0 0 0 1 x x x x x 1 0 1 0 1 x x x x x x 1 1 0 1 x x x x x x x 1 1 1 52 Priority Encoder Equations Q2 = D7 + D6 + D5 + D4 Q1 = D7 + D6 + D5 D4 D3 + D5 D4 D2 Q0 = D7 + D6 D5 + D6 D4 D3 + D6 D4 D2 D1 比D6優先權比D5高,因此D6=1時D5就必須被忽略 所以此處必須確認D6不為1,D5才能讓Q0為1 53 Priority Encoder VHDL Entity -- hi_pri8a.vhd ENTITY hi_pri8a IS PORT( d q END hi_pri8a; : IN BIT_VECTOR (7 downto 0); : OUT BIT_VECTOR (2 downto 0)); 54 Priority Encoder VHDL Architecture ARCHITECTURE a OF hi_pri8a IS BEGIN -- Concurrent Signal Assignments q(2) <= d(7) or d(6) or d(5) or d(4); q(1) <= d(7) or d(6) or ((not d(5)) and (not d(4)) and d(3)) or ((not d(5)) and (not d(4)) and d(2)); q(0) END a; <= -- in a similar fashion 55 Another VHDL Encoder – 1 -- hi_pri8b.vhd ENTITY hi_pri8a IS PORT( d q END hi_pri8b; : IN BIT_VECTOR (7 downto 0); : OUT INTEGER RANGE 0 TO 7); 56 Another VHDL Encoder – 2 ARCHITECTURE a OF hi_pri8b IS BEGIN -- Conditional Signal Assigment Encoder: q <= 7 WHEN d(7) = ‘1’ ELSE 6 WHEN d(6) = ‘1’ ELSE 5 WHEN d(5) = ‘1’ ELSE 4 WHEN d(4) = ‘1’ ELSE 3 WHEN d(3) = ‘1’ ELSE 2 WHEN d(2) = ‘1’ ELSE 1 WHEN d(1) = ‘1’ ELSE 0; END a; 57 Basic Multiplexers (MUX;多工器) • (MUX): A digital circuit that directs one of several inputs to a single output based on the state of several select inputs. • A MUX is called a m-to-1 MUX. • A MUX with n select inputs will require m = 2n data inputs (e.g., a 4-to-1 MUX requires 2 select inputs S1 and S0). 58 Basic Multiplexers (MUX) S1 is the MSB of the select inputs 59 Basic Multiplexers (MUX) 60 4-to-1 Multiplexers Truth Table S1 0 0 1 1 S0 0 1 0 1 Y D0 D1 D2 D3 61 Multiplexer Logic • Boolean expression for a 4-to-1 MUX is Y = D0 S1 S0 + D1 S1 S0 + D2 S1 S0 + D3 S1 S0 • This expression can be expanded to any size MUX so the VHDL architecture could use a very long concurrent Boolean statement. 62 Double Subscript Notation • Naming convention in which variables are bundled in numerically related groups, the elements of which are themselves numbered. • The first subscript identifies the group that a variable belongs to (D01, D00). • The second subscript indicates which element of the group a variable represents. 63 Truth Table for a 4-to-1 4-bit Bus MUX S1 0 0 1 1 S0 0 1 0 1 Y3 Y2 Y1 Y0 D03 D02 D01 D00 D13 D12 D11 D10 D23 D22 D21 D20 D33 D32 D31 D30 每一個輸入Mux的訊號都是4bit寬,所以Y也是4bit寬 64 Truth Table for a 4-to-1 4-bit Bus MUX 65 VHDL Constructs For MUXs • The following three VHDL constructs can be used to describe the Multiplexer: – Concurrent Signal Assignment Statement – Select Signal Assignment Statement – CASE Statement 66 PROCESS and Sensitivity List • PROCESS: A VHDL construct that contains statements that are executed if a signal in its sensitivity list changes. • Sensitivity list: A list of signals in a PROCESS statement that are monitored to determine whether the Process should be executed. 67 Case Statement • A case statement is a VHDL construct in which there is a choice of statements to be executed, depending on the value of a signal or variable. 68 Case VHDL Template CASE __expression IS WHEN __constant_value => __statement; __statement; WHEN __constant_value => __statement; __statement; WHEN OTHERS => __statement; __statement; END CASE; 69 MUX 4-to-1 VHDL – 1 • Basic Entity declaration for a 4-to-1 MUX: ENTITY mux4case IS PORT( d0, d1, d2, d3 s y END mux4case; : IN BIT; : IN BIT_VECTOR (1 downto 0); : OUT BIT); 70 MUX 4-to-1 VHDL – 2 ARCHITECTURE mux4to1 OF mux4case IS BEGIN -- Monitor select inputs and execute if they change PROCESS(s) BEGIN CASE s IS 71 MUX 4-to-1 VHDL – 3 WHEN "00" WHEN "01" WHEN "10" WHEN "11" WHEN others END CASE; END PROCESS; END mux4to1; => => => => => y y y y y <= <= <= <= <= d0; d1; d2; d3; '0'; 72 Multiplexer Applications • Used in directing multiple data sources to a single processing element such as multiple CD Player Streams to a DSP. • Used in Time Division Multiplexing (TDM;分時多工) by the Phone Service to multiplex multiple voice channels on a single coax line (or fiber). 73 Time Division Multiplexing (TDM) • Each user has a specific time slot in a TDM data frame. Each frame has 24 users (i.e., time slot). • TDM requires a time-dependent (counter) source to synchronize the select lines. • Each user’s time slot repeats on the next frame for more data. • The links are called T-Carriers (such as a T1 Line). 74 TDM Data Streams • Two methods in which data is transmitted: – Bit Multiplexing: One bit is sent at a time from the channel during the channel’s assigned time slot – Word Multiplexing: One byte is sent at a time from the channel during the channel’s assigned time slot 75 TDM Data Streams 76 TDM Data Streams 77 TDM Data Streams 64kbps/Voice channel 78 Demultiplexer Basics – 1 • Demultiplexer: A digital circuit that uses a decoder to direct a single input (from a MUX) to one of several outputs. • A DEMUX performs the reverse operation of a MUX. • The selected output is chosen by the Select Inputs (as in a MUX). 79 Demultiplexer Basics – 2 • Designated as a 1-to-n DEMUX that requires m select inputs such that n outputs = 2m select inputs. • 1-to-4 DEMUX Equations (D is the input signal): Y( 0 ) = D S1 S 0 ; Y( 1 ) = D S1S 0 ; Y( 2 ) = DS1 S 0 ; Y( 3 ) = DS1S 0 . • They are similar to a MUX and can be designed using CASE Statements. 80 Demultiplexer Basics – 3 81 Demultiplexer Basics – 4 輸入訊號D傳遞至選擇到的輸出端 82 Demultiplexer Basics – 5 83 Demultiplexer VHDL Entity -- Example of a 1 to 8 Demux ENTITY dmux8 IS PORT( s : IN STD_LOGIC_VECTOR (2 downto 0); d : IN STD_LOGIC; -- d is the input signal y : OUT STD_LOGIC_VECTOR (0 to 7)); END dmux8; 84 Demultiplexer VHDL Architecture ARCHITECTURE a OF dmux8 IS SIGNAL inputs : STD_LOGIC_VECTOR (3 downto 0); BEGIN inputs <= d & s; WITH inputs select Y <= “01111111” WHEN “0000”, -- d為0,選到的Channel就是0 “10111111” WHEN “0001”, • • • • • • “11111111” WHEN others; -- d可能為0,也可能為1 END a; 85 Demultiplexer VHDL Architecture 選到哪一個Channel,d就傳送至該Channel 86 Analog MUX/DEMUX • Uses a CMOS Switch or Transmission Gate that will allow a signal to Pass in two directions for + and – Voltages. • Some commercial types such as a CD4066 or 74HC4066(Both are Quad Bilateral Switches). • Multiplexes 4 CMOS Switches to a single output (Y) for analog multiplexing. 87 Analog MUX/DEMUX 88 Analog MUX/DEMUX S1 is the MSB of the select signal 89 Magnitude Comparators – 1 • Magnitude Comparator: A digital circuit that compares two n-Bit Binary Numbers and indicates if they are equal or which is greater. • A very simple One-Bit Magnitude Comparator is the Two-Input XNOR Gate: – When both inputs are equal, the output is a 1; if they are not, it is a 0(相等為1,不相等則為0). 90 Magnitude Comparators – 2 課本P.319頁錯誤; 誤植為 An −1 • Multiple Bit Comparisons AEQB = ( An-1 ⊕ Bn-1 ) ⋅ ( An- 2 ⊕ Bn- 2 ) …. • Also adds A > B (AGTB) and A < B (ALTB) Outputs. • For A > B, start with the MSB: – If An–1 > Bn–1, then AGTB = 1 • If not, then try the next most significant bit. 91 VHDL 4-Bit Magnitude Comparator – 1 ENTITY compare4 IS PORT( a, b agtb, aeqb, altb END compare4; : IN INTEGER RANGE 0 to 15; : OUT STD_LOGIC); 92 VHDL 4-Bit Magnitude Comparator – 2 ARCHITECTURE a OF compare4 IS SIGNAL compare :STD_LOGIC_VECTOR (2 downto 0); BEGIN PROCESS (a, b) BEGIN IF a<b THEN compare <= “110”; --Active Low output ELSIF a = b THEN compare <= “101”; --Active Low output 93 VHDL 4-Bit Magnitude Comparator – 3 ELSIF a > b THEN compare <= “011”; --Active Low output ELSE compare <= “111”; END IF; agtb <= compare(2); aeqb <= compare(1); altb <= compare(0); END PROCESS END a; 94 Parity Basics – 1 • Parity: A digital system that checks for errors in a n-Bit Binary Number or Code. • Even Parity: A parity system that requires the binary number and the parity bit to have an even # of 1s. • Odd Parity: A parity system that requires the binary number and the parity bit to have an Odd # of 1s. 95 Parity Basics – 2 • Parity Bit: A bit appended on the end of a binary number or code to make the # of 1s odd or even depending on the type of parity in the system. • Parity is used in transmitting and receiving data by devices in a PC called UARTs, that are on the COM Port. 96 Parity Basics – 3 97 Parity Calculation • N1 = 0110110: – It has four 1s (an even number). – If Parity is ODD, the Parity Bit = 1 to make it an odd number (5). – If Parity is EVEN, the Parity Bit = 0 to keep it an even number (4). • N2 = 1000000: – One 1 in the data. – Podd = 0. – Peven = 1. 98 Parity Generation HW – 1 • A basic two-bit parity generator can be constructed from a XOR Gate. • When the two inputs are 01 or 10, the output is a 1 (so this is even parity). • When the two inputs are 00 or 11, the output is a 0. • For a parity generator of n bits, add more gates. 99 Parity Generator HW – 2 • Cascading a long chain of XOR gates could cause excessive propagation delays. • To check for a Parity error, the receiver (RX) just generates a new Parity Bit (P1) based on the received parallel data and then compares it to the parity bit transmitted (P2). 100 Parity Generator HW – 3 • If there is an error, the two bits (P1 and P2) will not be equal, and we can use a two-bit magnitude comparator to check this(an XOR gate;P1與P2不相等時會輸出1,表示錯誤). • This check is called syndrome. – If there are no errors, the syndrome output (Perr) is 0. • Parity is not a foolproof system(保證安全的系統). – If two bits are in error, the error is not detected. 101 Parity Generator HW – 4 Even Parity 102 VHDL GENERATE Statement __generate_label: FOR __index_variable IN __range GENERATE __statement; __statement; END GENERATE; 103 4-Bit Parity VHDL Code – 1 LIBRARY ieee; USE ieee.std_logic1164.ALL; -- An example of even parity generator. ENTITY parity4_gen IS PORT( d : IN STD_LOGIC_VECTOR (0 to 3); pe ; OUT STD_LOGIC); END parity4_gen; 104 4-Bit Parity VHDL Code – 2 ARCHITECTURE parity OF parity4_gen IS SIGNAL p : STD_LOGIC_VECTOR (1 to 3); BEGIN p(1) <= d(0) xor d(1); --p(1)必須先定義,否則For迴圈會發生錯誤 parity_generate: FOR i IN 2 to 3 GENERATE p(i) <= p(i-1) xor d(i); END GENERATE; pe <= p(3); END parity; 105