Chapter3

advertisement

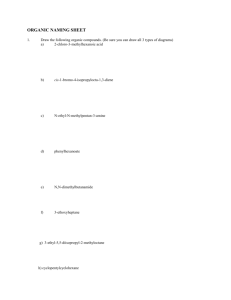

Chapter 3 Combinational Logic By Taweesak Reungpeerakul Contents 242-208 CH3 Basic Combinational Logic Circuits Implement SOP and POS using Basic Logic Gates Universal Property of NAND and NOR Combinational Logic using NAND and NOR Operation with Pulse Waveforms Digital System Application 2 3.1 Basic Combinational Logic Circuit A AB B AC Out C BC 242-208 CH3 AB+AC+BC Inputs A B C AB 0 00 0 001 0 010 0 011 0 100 0 101 0 110 1 111 1 AC 0 0 0 0 0 1 0 1 BC OUT 0 0 0 0 0 0 1 1 0 0 0 1 0 1 1 1 3 AND-OR-INV Logic Invert AND-OR in SOP AND-OR-INV in POS AB+AC+BC =(A+B)(A+C)(B+C) A B A B C 242-208 CH3 Out Out C 4 XOR OUT = AB + AB A Out B 242-208 CH3 5 XNOR OUT = AB + AB = AB + AB A B Out 242-208 CH3 6 3.2 Implementing Combinational Logic Ex#1: OUT = ABC+DE A B C Ex#2: OUT = A(BC+DE) A B Out C Out D E 242-208 CH3 D E 7 From Truth Table Truth A B 0 0 0 0 0 1 0 1 1 0 1 0 1 1 1 1 242-208 CH3 Table C OUT 0 0 1 1 0 1 1 0 0 0 1 1 0 0 1 0 C B A Out 8 Example TableLogic Circuit Karnaugh Map Simplified Circuit Truth Table B C OUT 0 0 1 0 1 1 1 0 0 1 1 0 0 0 0 0 1 1 1 0 0 1 1 1 A 0 0 0 0 1 1 1 1 A BC 00 0 1 242-208 CH3 1 01 11 C B A Out 10 1 1 1 9 2.3 Universal Property of NAND&NOR INV, OR, AND, and NOR created by using NAND gates A B AND INV A A A+B B 242-208 CH3 AB OR A+B B NOR 10 Universal Property of NOR INV, OR, AND, and NAND created by using NOR A gates AB INV B AND A A B A+B OR 242-208 CH3 AB B NAND 11 3.4 Combinational Logic using NAND & NOR NAND; OUT = AB+CD = AB+CD = (AB)(CD) A B OUT C D A B OUT A B OUT C D C D 242-208 CH3 12 Dual Symbols of NAND Always use the gate symbols in such a way that every connection between a gate output and a gate input is either bubble-to-bubble or nonbubble-to-nonbubble. A B A OUT C C ABC 242-208 CH3 B OUT AB+C 13 Example: implemented by NAND Ex1: ABC+DE A B C OUT D E 242-208 CH3 Ex2: ABC+D+E A B C D E OUT 14 Combinational Logic using NOR A B NOR; (A+B)(C+D) = (A+B)(C+D) = (A+B)+(C+D) OUT C D A B OUT A B OUT C D C D 242-208 CH3 15 Dual Symbols A B OUT C (A+B)+C A B OUT C 242-208 CH3 (A+B)C 16 3.5 Operation with Pulse Waveforms Logic circuit Timing diagram A A D B B Out C C D OUT 242-208 CH3 17 Develop logic circuit from waveforms A B C C A Out B OUT 242-208 CH3 18 Functions of Combinational Logic (Session 2) 242-208 CH3 Adders Comparators Decoders Encoders Code Converters Multiplexers Demultiplexers 19 3.6 Basic Adders Half Adder A B SUM 0 0 0 0 1 1 1 0 1 1 1 0 SUM = AB Cout = AB Cout 0 0 0 1 Full Adder A B Cin SUM 0 0 0 0 0 0 1 1 0 1 0 1 0 1 1 0 1 0 0 1 1 0 1 0 1 1 0 0 1 1 1 1 Cout 0 0 0 1 0 1 1 1 SUM = ABCin Cout = AB+(AB)Cin 242-208 CH3 20 Logic Symbol and Diagram Half Adder Full Adder ∑ ∑ A B A B Cin ∑ Cout SUM A B ∑ Cout SUM Cin A B 242-208 CH3 Cout Cout 21 Full Adder by 2 Half Adders Half Adder Full Adder ∑ A B ∑ SUM = ABCin Cout = AB+(AB)Cin Cout SUM ∑ A B A B 242-208 CH3 A B ∑ Cout AB ∑ A B ∑ SUM Cout Cout Cin AB Cout 22 3.7 Parallel Binary Adder A full adder is required for each bit in the numbers. A2A1 + B2B1 S3S2S1 A2 B2 A1 B 1 A2 B2 A1 B1 A B Cin A B Cin A B Cin A B Cout ∑ S3 S2 242-208 CH3 Cout ∑ Cout ∑ S3 S2 Cout ∑ S1 S1 Question: 4-bit numbers 23 4-bit Parallel Adders A4 B4 A3 B 3 A2 B2 A1 B1 A B Cin A B Cin A B Cin A B Cin Cout ∑ Cout ∑ C3 C4 S4 242-208 CH3 Cout ∑ C2 S3 Cout C0 ∑ C1 S2 S1 An 0 0 0 0 1 1 1 1 Bn 0 0 1 1 0 0 1 1 Cn-1 0 1 0 1 0 1 0 1 Sn 0 1 1 0 1 0 0 1 Cn 0 0 0 1 0 1 1 1 24 IC:4-bit Parallel Adder Example: 74LS83A (or 74LS283) 74LS83A 74LS283 Question: Show circuit diagram of 242-208 CH3 A+B by using 74LS83A. A = 00001111 and B = 01011100 25 3.8 Comparators A1 B1 A0 B0 242-208 CH3 Equality Comparing A and B: AB If A=B, output = 0 If A≠B, output = 1 HIGH indicates equality: AB (XNOR) A1A0 ? B1B0 1 if A=B Inequality IC: 74LS85 A0 A1 A2 A3 Cascading inputs B0 B1 B2 B3 0 COMP A 3 A>B A>B A=B A=B A<B A<B 0 B Outputs 3 0 if A¹B Question: Show circuit diagram in order to compare two 8-bit numbers 26 by using 74LS85. Two 74LS85 Cascaded Arrangement LSBs A0 A1 A2 A3 +5.0 V B0 B1 B2 B3 242-208 CH3 MSBs 0 COMP A 3 A>B A>B A=B A=B A<B A<B 0 A 3 A4 A5 A6 A7 B4 B5 B6 B7 0 COMP A 3 A>B A>B A=B A=B A<B A<B 0 A Outputs 3 27 74HC85 Truth Table 242-208 CH3 28 3.9 Decoders A decoder is a logic circuit that detects the presence of a specific combination of bits at its input. A0 A1 A0 OUT A2 A2 A3 A3 Active HIGH decoder for 0011 242-208 CH3 A1 OUT Active LOW decoder for 0011 29 4-to-16 Decoder Bin/Dec 1 4-bit binary input 1 0 1 A0 A1 A2 A3 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 1 1 1 1 1 1 1 1 1 1 1 0 1 1 1 1 Decimal outputs A0 A1 A2 A3 CS1 CS2 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 1 2 4 8 & 15 IC: 74HC154 Question: Use 74HC154 to implement the logic in 242-208 CH3 order to support a 5-bit number. 30 BCD-to-Decimal Decoder BCD-to-decimal decoders accept a binary coded decimal input and activate one of ten possible decimal digit indications. IC: 74HC42 Question: Assume the inputs to the BCD/DEC (15) A0 A1 (14) A2 (13) (12) A3 242-208 CH3 0 1 2 3 4 5 6 7 8 9 1 2 4 8 74HC42 (1) (2) (3) (4) (5) (6) (7) (9) (10) (11) 74HC42 decoder are the sequence 0101, 0110, 0011, and 0010. Describe the output. Answer: All lines are HIGH except for one active output, which is LOW. The active outputs are 5, 6, 3, and 2 in that order. Question: Write truth table of output 0. 31 BCD-to-7-Segment Decoder IC: 74LS47 BCD Inputs (D-A) 7-segment Outputs (a -g) Ripple Blanking Input (RBI) Blanking Input/Ripple Blanking Output (BI/RBO) Lamp Test (LT) Zero Suppression 242-208 CH3 VCC (16) BCD/7-seg BI/RBO BCD inputs LT RBI (7) (1) (2) (6) (3) (5) a b c d e f g 1 2 4 8 LT RBI 74LS47 (4) (13) (12) (11) (10) (9) (15) (14) BI/RBO Outputs to seven segment device (8) GND 32 Illustration of Leading Zero Suppression 0 0 0 0 0 RBI LT 8 4 2 1 74LS47 g f e d c b a BI/RBO 242-208 CH3 0 0 0 0 0 RBI LT 8 4 2 1 74LS47 g f e d c b a BI/RBO 0 0 0 1 1 RBI LT 8 4 2 1 74LS47 g f e d c b a BI/RBO 1 0 0 0 0 RBI LT 8 4 2 1 74LS47 g f e d c b a BI/RBO 33 Illustration of Trailing Zero Suppression 0 1 0 1 RBI LT 8 4 2 1 74LS47 g f e d c b a BI/RBO 242-208 CH3 0 1 1 1 RBI LT 0 0 0 0 8 4 2 1 RBI LT 74LS47 0 0 0 0 8 4 2 1 RBI LT 74LS47 8 4 2 1 74LS47 g f e d c b a BI/RBO g f e d c b a BI/RBO g f e d c b a BI/RBO 1 0 0 34 3.10 Encoders An encoder accepts an active logic level on one of its inputs representing a digit, such as a decimal or octal digits, and converts it to a coded output, such as BCD or binary. IC: 74HC147 16-to-4 encoder (decimal-to-BCD) IC: 74F148 8-to-3 encoder 1 A0 2 3 4 5 6 7 8 A1 A2 A3 9 242-208 CH3 35 Example Show how the decimal-to-BCD encoder converts the decimal number 3 into a BCD 0011. 1 0 1 2 0 1 3 1 4 5 6 7 8 9 242-208 CH3 0 0 0 0 0 0 0 0 A0 A1 A2 A3 36 74HC147 VCC The 74HC147 is an example of an IC encoder. It has ten activeLOW inputs and converts the active input to an active-LOW BCD output. This device offers additional flexibility with a priority encoder. (16) Decimal input (11) (12) (13) (1) (2) (3) (4) (5) (10) HPRI/BCD 1 2 3 4 5 6 7 8 9 1 2 4 8 (9) (7) (6) (14) BCD output (8) GND 74HC147 242-208 CH3 37 A Simplified Keyboard Encoder VCC R7 7 R8 8 R4 4 R5 R1 242-208 CH3 R6 6 R2 2 R0 0 9 5 1 R9 1 2 3 4 5 6 7 8 9 1 2 4 8 BCD complement of key press R3 3 The zero line is not needed by the encoder, but may be used by other circuits to detect a key press. 38 3.11 Code Converters 242-208 CH3 BCD-to-BIN Conversion IC: 74184 BIN-to-BCD Conversion IC: 74185 39 Code Converters (cont.) B0 B1 B2 B3 BIN-to-Gray G0 LSB G0 G1 G1 G2 G2 G3 MSB G3 Gray-to-BIN LSB B0 B1 B2 B3 MSB Question: Show the conversion of binary 0111 to Gray 242-208 CH3 and vice versa. 40 3.12 Multiplexers (MUX) A multiplexer has several datainput lines and a single output line. It also has data-select inputs, which permit digital data on any one of the inputs to be switched to the output line. Another name is a data selector. IC: 74HC157 Quad 2-input MUX IC: 74HC151 8-input MUX MUX S0 Data select S1 D0 D1 Data D inputs D2 3 0 1 0 1 0 1 2 3 Data output Question: Which data line is selected if S1S0 = 10? 242-208 CH3 41 ICs 242-208 CH3 74HC157 Quad 2-input MUX 74HC151 8-input MUX 42 3.13 Demultiplexers (DEMUX) A DEMUX basically reverses the multiplexing function. It takes data from one input line and distributes to one of output lines depending on the select lines. Another name is a data distributor. IC: 74LS138 8-output DEMUX 74LS138 DEMUX Data select lines Enable inputs 0 1 0 A0 A1 A2 G1 G2A G2B Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 Data outputs Question: Which data output is selected if A2A1A0 = 010? 242-208 CH3 43 A0 A1 A2 G1 G2A LOW G2B LOW Example (DEMUX) Determine the outputs, given the inputs shown. DEMUX Data select lines Enable inputs A0 A1 A2 G1 G2A G2B 74LS138 242-208 CH3 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 Data outputs Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 44