Lec15_v1 - UCSD VLSI CAD Laboratory

advertisement

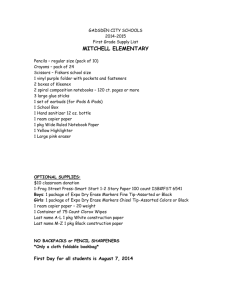

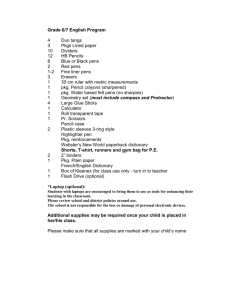

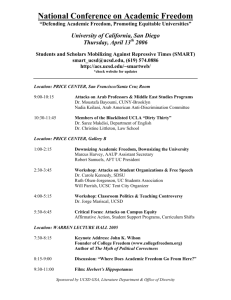

CSE241 VLSI Digital Circuits Winter 2003 Lecture 15: Packaging CSE241 L3 Packaging.1 Kahng & Cichy, UCSD ©2003 Topics Packaging IO Pads Bumps Area vs. peripheral IO CSE241 L3 Packaging.2 Kahng & Cichy, UCSD ©2003 Packaging Styles Popular Flip-chip BGA TSOP Package Materials: Ceramic Plastic CSE241 L3 Packaging.3 Kahng & Cichy, UCSD ©2003 Die Connections Pads Logic devices – Around periphery of die 1 row: 70µ pitch 2 rows: 40-50µ staggered pitch Memory (DRAM) – in a line at center of die 1 row: 100-150µ pitch CSE241 L3 Packaging.4 Kahng & Cichy, UCSD ©2003 Flip-chip Entire surface of die can be covered with bonding sites Placed on 250µ centers Small balls (bumps) added at wafer level Chip flipped over and connected to package Substrate is at top of package CSE241 L3 Packaging.5 Slide courtesy of Stanford Kahng & Cichy, UCSD ©2003 Package Styles Logic BGA - Ball Grid Array QFP - Quad Flat Pack Memory TSOP - Thin Small Outline Package CSP - Chip Scale Package CSE241 L3 Packaging.6 Kahng & Cichy, UCSD ©2003 Other Packages Types CDIP Ceramic Dual In-Line Pkg SB Side-Braze CPGA Ceramic Pin Grid Array CZIP Ceramic Zig-Zag Pkg DFP Dual Flat Pkg HLQFP Thermally Enhanced Low Profile LCC J-Leaded Ceramic or Metal Chip Carrier LCCC Leadless Ceramic Chip Carrier LGA Land Grid Array LPCC Leadless Plastic Chip Carrier LQFP Low Profile Quad Flat Pack MCM Multi-Chip Module MQFP Metal Quad Flat Pkg PDIP Plastic Dual-In-Line Pkg CSE241 L3 Packaging.7 PFM Plastic Flange Mount Pkg PLCC Plastic Leaded Chip Carrier PPGA Plastic Pin Grid Array QFP Quad Flat Pkg. SDIP Shrink Dual-I-Line Pkg SIP Single-In-Line Pkg. SOJ J-Leaded Small-Outline Pkg SOP Small-Outline Pkg Triple Flat PackTO/SOT Cylindrical Pkg TSOP Thin Small-Outline Pkg. TSSOP Thin Shrink Small-Outline Pkg VFLGA Thin Very-Fine Land Grid Array TVSOP Very Thin Small-Outline Pkg VQFP Very Thin Quad Flat Pkg VSOP Very Small Outline Pkg Kahng & Cichy, UCSD ©2003 Ball Grid Array Pin Counts Clock Frequency FC-BGA 450 2116 2.5GHz TAB-BGA 352 800 150MHz EBGA 352 700 800MHz 256 500 250MHz 256 420 150MHz 40 460 500MHz FDH-BGA PBGA FBGA CSE241 L3 Packaging.8 Slide courtesy of Fujitsu Kahng & Cichy, UCSD ©2003 TSOP Thin Small Outline Package (TSOP) Most popular DRAM package Very cheap Wires bond to lead frame Bond pads sometimes at center of die Leaded surface mount CSE241 L3 Packaging.9 Photo courtesy of Stanford Kahng & Cichy, UCSD ©2003 BGA Ball Grid Array Most popular ASIC package Basically a small printed circuit board Multiple planes available in package Possible to route larger numbers of signals Better signal integrity CSE241 L3 Packaging.10 Photo courtesy of Stanford Kahng & Cichy, UCSD ©2003 QFP Wire Bond package Leads are coplanar fanning into die Higher coupling CSE241 L3 Packaging.11 Photo courtesy of Fujitsu Kahng & Cichy, UCSD ©2003 Packaging Trends Memory: Stacked die - Higher density (3-D scaling) - Still uses same inexpensive die Logic CSE241 L3 Packaging.12 Kahng & Cichy, UCSD ©2003 I/Os I/O Drivers I/O driver design is always challenging Backwards compatibility a key problem Core Supply voltages changing Older devices will have larger swings than new ones - Old: TTL level - Modern: 1.5v, 2.0v Bandwidth requirements increasing Need to have more pins or higher bandwidth per pin or both - Memory interface widths - Encryption keys CSE241 L3 Packaging.13 Kahng & Cichy, UCSD ©2003 I/O Pads Traditional Pads at periphery Flip-chip Pads anywhere on die ESD Provide Esd protection to die Human model - Models capacitive discharge from handling CSE241 L3 Packaging.14 Kahng & Cichy, UCSD ©2003 Pads Types Generic: Input/output Bi-directional Tri-state Analog Differential Memory Bi-directional High-speed >1Ghz High-voltage >5v CSE241 L3 Packaging.15 Kahng & Cichy, UCSD ©2003 Bumps Flip-chip Power (Vdd/Vss) Signals Advantages Signals - Are locally fed - Reduces skew - Reduces delay of pushing to chip boundary Power: - Local power - Multiple Vdd sources - Different Vdd CSE241 L3 Packaging.16 Kahng & Cichy, UCSD ©2003