STUDENT RUN IC FACTORY

advertisement

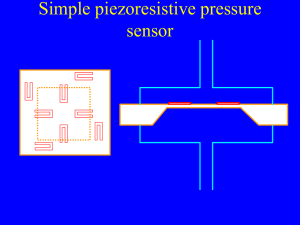

MEMS Fabrication Blog 2015 ROCHESTER INSTITUTE OF TECHNOLOGY MICROELECTRONIC ENGINEERING Surface MEMS Design Project Dr. Lynn Fuller, Adam Wardas Webpage: http://people.rit.edu/lffeee Microelectronic Engineering Rochester Institute of Technology 82 Lomb Memorial Drive Rochester, NY 14623-5604 Tel (585) 475-2035 Email: Lynn.Fuller@rit.edu Department webpage: http://www.microe.rit.edu 10-18-2015 MEMS_Fabrication_Blog_2015.ppt Rochester Institute of Technology Microelectronic Engineering Page 1 MEMS Fabrication Blog 2015 INTRODUCTION This document is a blog addressing the fabrication and testing of the MEMS wafers that were made as part of the MCEE770 MEMS Fabrication class. The students in the class provided individual design layouts that were merged into a single project chip design used to create the reticles for this project. Other documents provide details addressing the design, layout and fabrication for this project. Rochester Institute of Technology Microelectronic Engineering Page 2 MEMS Fabrication Blog 2015 PROCESS DESCRIPTION Mechanical Poly2 Layer Sacrificial Oxide Metal Field Oxide Bottom Poly1 Starting Wafer This is a surface micromachine process with two layers of polysilicon and one layer of metal. Poly2 can be suspended above the wafer allowing for structures that can move. The two poly layers can cross without connection or can be connected through anchor holes. The metal layer can connect to Poly2 through a via or to Poly1 through via and anchor holes. The yellow layers are silicon nitride. Rochester Institute of Technology Microelectronic Engineering Page 3 MEMS Fabrication Blog 2015 LAYOUTS USING MENTOR GRAPHICS SOFTWARE Students did their design and layout using the computers in our VLSI Lab Rochester Institute of Technology Microelectronic Engineering Page 4 MEMS Fabrication Blog 2015 MENTOR GRAPHICS LAYOUT OF CANTILEVER The cantilever shown is anchored on the left and free to move on the right. The design includes resistive and capacitive position sensors and electrostatic actuation. The device can be used as an accelerometer. Rochester Institute of Technology Microelectronic Engineering Page 5 MEMS Fabrication Blog 2015 2015 MEMS MULTICHIP PROJECT DESIGN Rochester Institute of Technology Microelectronic Engineering Page 6 MEMS Fabrication Blog 2015 MASK ORDER FORM mems-2015-final.gds 8 16.5mm x 16.5mm mems-2015-final Dr Fuller RIT x Rochester Institute of Technology Microelectronic Engineering Page 7 MEMS Fabrication Blog 2015 MASK ORDER FORM DETAILS Reticle Reticle Number Name Design Boolean Function Layer #’s Dark/ Comment Clear 1 Poly1 1 None Clear 2 SacOx 2 None Clear 3 Anchor 3 3 Inverted Dark 4 No Implant 15 None Clear 5 Poly2 4,16 4 AND (16 Inverted) Clear 6 Cut 6 6 Inverted Dark 7 Metal 7 None Clear 8 Release 5 Inverted Dark Design Layer 9 Out (outline) is not used. It is only for placement of projects on the multi-project reticle template. Rochester Institute of Technology Microelectronic Engineering cp <filename>.gds /dropbox/masks Page 8 MEMS Fabrication Blog 2015 MASK PROCESS FLOW Data Prep CAD GDSII MEBES File MEBES Job Expose Coat Plate Computer Aided Transcription Software IC Graph by Mentor Graphics Etch Cr CATS Inspect Develop Maskmaking Inspect Clean Ship out This process can take weeks and cost between $1000 and Rochester Institute of Technology $20,000 for each mask depending on the design complexity. Microelectronic Engineering Page 9 MEMS Fabrication Blog 2015 MEBES - Manufacturing Electron Beam Exposure System The masks were made using the MEBES electron beam writer at RIT. This tools is capable of writing on glass or quartz plates or wafers with spot size down to 0.1um. Rochester Institute of Technology Microelectronic Engineering Page 10 MEMS Fabrication Blog 2015 CLEAR FIELD RETICLE FOR ASML Poly One Non-Chrome Side Metal Chrome Side Rochester Institute of Technology Microelectronic Engineering Page 11 MEMS Fabrication Blog 2015 SURFACE MEMS 2015 PROCESS 1. Starting wafer 2. PH03 – level 0, Marks 3. ET29 – Zero Etch 4. ID01-Scribe Wafer ID, D1… 5. ET07 – Resist Strip, Recipe FF 6. CL01 – RCA clean 7. OX04 – 6500Å Oxide Tube 1 8. CV01 – LPCVD Poly 5000Å 9. IM01 – Implant P31, 2E16, 60KeV 10. PH03 – level 1 Poly-1 11. ET08 – Poly Etch 12. ET07 – Resist Strip, Recipe FF 13. CL01- RCA Clean 14. CV03 – OX05 700Å Dry Oxide 15. CV02- LPCVD Nitride 4000Å 16. PH03 – level 2 Anchor 17. ET29 – Etch Nitride 18. ET07 - Resist Strip, Recipe FF 19. CL01 – RCA Clean 20. CV03-TEOS SacOx Dep 1.75um 21. PH03 – level 3 SacOx Define 22. ET06 - wet etch SacOx Define Etch 23. ET07- Resist Strip, Recipe FF 24. CL01 – RCA Clean 25. CV01-LPCVD Poly 2um, 140 min 26. PH03 - level 4 No Implant 27. IM01-P31 2E16 100KeV 28. ET07 Resist Strip, Recipe FF 29. OX04-Anneal Recipe 119 30. DE01 Four Point Probe 31. PH03 - level 5 Poly2 32. ET68 - STS Etch 33. ET07 - Resist Strip, Recipe FF 34. CV02 – LPCVD Nitride 4000Å 35. PH03 – level 6 Contact Cut 36. ET29 – Etch Contact Cut 37. ET06 – Etch Oxide 38. ET07 – Resist Strip, Recipe FF 39. CL01 – RCA Clean 40. ME01 – Metal Deposition - Al Rochester Institute of Technology Microelectronic Engineering 41. PH03 – level 7 Metal 42. ET55 – Metal Etch - wet 43. ET07 – Resist Strip 44. PH03 – level 8 – Final SacOx 45. ET66 – Final SacOx Etch 46. ET07 - Resist Strip, Recipe FF 47. SEM1 – Pictures 48. TE01 - Testing 9-1-15 Etch rates LPCVD Si3N4 in 5:1 BHF 120Å/min N+Poly in BHF 50Å/min PECVD SiO2 in 5:1 BHF 2000Å/min Page 12 MEMS Fabrication Blog 2015 ZERO ETCH AND PHOTORESIST STRIP Today’s Goal: Coat the wafers with photoresist, expose with ASML stepper, develop and plasma etch ASML alignment marks on six wafers. Etch Silicon using Drytek Quad 482 Etcher – Cleaning of chamber for 5 min. in 02 plasma Etching the device wafer for 2 min. in CF4, CHF3 and O2 plasma Inspection of alignment marks on wafer Removal of Photoresist using GaSonics - (recipe FF) Microscope images of alignment marks before and after P.R. removal Before P.R. removal After P.R. removal Rochester Institute of Technology Drytek Quad Microelectronic Engineering GaSonics PR Asher Authors: Abhinav, Nikhil, Ranjana, Shruthi, Yamini October 19, 2015 Page 13 MEMS Fabrication Blog 2015 RCA CLEAN AND OXIDE GROWTH Today’s Goal: Remove organic and metallic contaminants from wafers with RCA clean, steam oxide growth of 6500Å of oxide in Bruce Tube 1. • Performed step 6: CL01 (RCA clean) Cleaned four wafers from lot Processed through SRD afterwards • Adam developed and etched the other two wafers in the lot • Performed step 7: OX04 (oxide growth) Procedure used to grow 6500A of oxide • Measured Oxide Thickness: Mean : 6597.7 Å Std Dev. = 0.38% CL01 – RCA Clean OX04 – oxide growth Rochester Institute of Technology Microelectronic Engineering Authors: Mattias Herrfurth, Corey Shay October 20, 2015 Page 14 MEMS Fabrication Blog 2015 TITLE Today’s Goal: Coat the wafers with photoresist, expose with ASML stepper, develop and plasma etch alignment marks on six wafers. This is a template for submitting pages to this blog Duplicate or copy this page Change the title above… use all capital letters Change Today’s Goal Change the date Change the names in the Authors box Move these text boxes around as needed Change size of text boxes Etc. Picture caption More information Data and Measurements Pictures, especially of students in the lab Pictures of wafer seen through microscope Pictures of tools used Movies if really short and interesting Rochester Institute of Technology Microelectronic Engineering Authors: Dr. Fuller, Adam Wardas October 18, 2015 Page 15