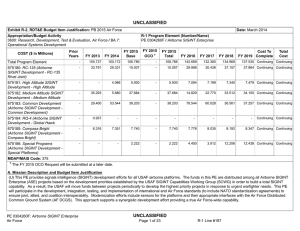

FINAL COTS01 Curtiss Wright_original

advertisement

{FINAL COTS01 Curtiss Wright.docx 3 page article from Icon Labs for Tech Recon: Signal

Chain: Signal Capture for Radar and SIGINT section for January COTS Journal.}

Editor’s Notes:

1.

Figures 3 is a diagram that can probably be used as is, but leave enough room to make it

big enough to read.

Ensuring High SIGINT Signal Fidelity Requires a Coherent Approach

Challenges to SIGINT system design increase every year. Addressing them requires all of the

available signal processing tools using a scalable architecture.

Marc Couture, Senior Product Manager, ISR Solutions Group

Curtiss-Wright Defense Solutions

SIGINT systems have the daunting challenge of ensuring that the fidelity of the signals they

capture off the air remain as true to the analog original as possible, from the RF and microwave

front end through digitization by an ADC and processing by one or more types of devices. This

task is in addition to maintaining coherence of signals from multiple sensors, and processing of

GPS, timing, time difference of arrival (TDOA), signal identification, and possibly other

functions. The increasingly dense electromagnetic environments they must process and the wider

amounts of spectrum they must “ingest”, make their design extraordinarily difficult. These issues

can be effectively addressed with a scalable approach that makes best use of the ADCs, FPGAs,

DSPs, and other processing elements in the system.

Next-generation SIGINT systems must capture more signals with wider bandwidths, as signals

of interest today can be found over a much wider range of frequencies, which affects every

element of system design (Figure 1). Fortunately, the latest commercially-available ADCs have a

wide range of sampling rates and resolutions, ranging from 250 MS/s 16-bit to 12 GS/s 8-bit.

CPUs, FPGAs, DSPs, and increasingly GPGPUs provide the fixed-and floating-point processing

capabilities required to handle the broad data streams resulting from signal capture bandwidths

of 12 GHz or more.

Digital Design Issues

However, from a design perspective, the key determinant in how well the digital portion of the

system will perform lies just before it—between the antenna and the input to the ADC. The

receiver must be extremely sensitive and capable of error-free signal capture because regardless

of the resolution, spurious-free dynamic range, and sample rate of the ADC, the device can only

deliver its optimum performance when it is presented with a clean signal environment.

For example, as analog signals have a wide dynamic range, ADC voltage thresholds must be

respected, which requires well-designed automatic gain control (AGC) circuits, a lack of which

can (among other things) increase aperture jitter. This malady is created within the device’s

sample-and-hold circuit and caused by a noisy clock reference, temperature drift, and other

factors. While it is not created by the input signals themselves, it is worsened by those with

significant changes in amplitude. As AGC circuits reduce these changes they can significantly

minimize aperture jitter. In short, the entire bandwidth ingested by the ADC must be optimized

to ensure all or at least most of its potential performance is realized.

FPGA Takes Over

Once the ADC digitizes the signals, they are typically sent to an FPGA that acts on them in

various ways depending on the mission of the overall system. The first problem encountered at

this stage is a result of the wide instantaneous bandwidths afforded by current ADCs, which is

increasing every year. The result is a truly enormous amount of data, which if not reduced in size

becomes extremely difficult if not impossible to analyze within the confines of a reasonable

system footprint.

A simplistic “brute force” approach would be to send the entire captured bandwidth to a

wideband digitizer after which massive blocks of digital signal processing hardware would act

on it. Such a system is practical only when the system is located in a platform or other location

where its large size (and cost) can be accommodated. Techniques have been implemented in the

RF and microwave portion of SIGINT systems to reduce signal content as well as identify

potential signals of interest before it reaches the ADC. These techniques reduce the burden not

just on the converter but on all stages following it. However, they alone cannot entirely address

the issue.

This is where the capabilities of FPGAs in combination with multi-core processors such as the

Intel Core i7, along with the ability to implement them together are very appealing. FPGAs can

sort through this data and reduce it through decimation, extracting only those portions containing

signals of interest based on known waveforms or other “interesting” characteristics. The

resulting data stream is dramatically reduced and its data rate lowered, making easier the job of

latter processing stages.

Dealing with all of these variables is difficult enough in a single data stream, but SIGINT

systems rely on multiple sensors, and they require information not just about the signals

themselves but from where they are being emitted as well through interferometry—directionfinding. Adding “DF” into the mix requires precise clock timing and synchronization, as the

system’s multiple channel must be coherent. These sensors can be on the wing tips, nose, and tail

of and aircraft, or far away in a stand-off system. Consequently, their outputs must be extremely

coherent with all ADC clocks precisely aligned and the captured data calibrated and timestamped.

Scalable SIGINT Solutions

One of the great advantages of OpenVPX is its ability to enable multi-functionality in a common

architecture from the ADC through FPGAs, DSPs, general-purpose processors, timing and

control capability, and other functions. This provides the flexibility to accommodate signals that

have either already been converted from analog to digital form or analog signals directly from a

broadband RF front end. With all of these device types available, the strengths of each one can

be fully exploited. For example, FPGAs repeatedly perform fixed-point or possibly singleprecision floating point processing very quickly and have vast parallel (connectivity), but

generally cannot perform double-precision floating-point processing or handle Doppler

processing. A CPU such as the Core i7 can perform multiple functions including Doppler

processing, aided as it is by on-chip floating-point processing cores. A CPU is also better at nonrepetitive processing or decision making processes. Consequently, it is essential that a SIGINT

system employ both types of devices, as they need one another.

In a 16-channel system using Curtiss-Wright’s CHAMP-FX4, FMC-518, XCLK1 and CHAMPAV8 for example (Figure 1), the ADC, FPGA, and Core i7 processor provide a full range of

functions. The FMC-518 FMC converts 4 analog channels of 250 MHz to digital data and passes

this data to the Virtex-7 FPGAs on the CHAMP-FX4. After decimating and processing the

received data, the FPGAs pass the data to the CHAMP-AV8 via SRIO for final processing. The

processor can make adjustments to processing coefficients stored in the FPGAs as necessary

based on its analysis of the data being received. To insure that all 16 inputs are sampled with

aligned clocks, the XCLK1 XMC installed on the CHAMP-AV8 provides aligned clocks to the 4

FMCs, and insures they all start sampling at the same time. Figure 2 shows what the system

looks like with all components interconnected.

Each FX4 platform accommodates two FMCs that can handle multiple channels and provides

almost unlimited scalability by adding more FX4s working from a single clock reference to

provide the required level of signal coherence. The common, shared characteristics afforded by

this solution, and the inherent scalability of the FX4, make it possible to create a SIGINT

solution meeting stringent SWaP-C requirements.

Endless Performance Appetite

To achieve their progressively more difficult tasks, SIGINT systems must achieve performance

greater than their predecessors, over much wider bandwidths, in footprints including small

airborne platforms, in a more congested electromagnetic environment rife with new and existing

threats. This is best accomplished at the subsystem level by taking advantage of the latest ADCs

and all types of signal processing devices employing a scalable architecture. This approach

ensures that the precise timing and synchronization requirements of SIGINT systems can be

maintained regardless of the number of its sensors.

Curtiss-Wright Defense Solutions

Ashburn, VA

(703) 779-7800

www.cwcdefense.com.

CAPTIONS:

Figure 1.

Advanced SIGINT systems—like this Senior Scout ISR system—must capture more signals with

wider bandwidths, as signals of interest today can be found over a much wider range of

frequencies, which affects every element of system design.

Figure 2.

Using a CHAMP-FX4, FMC-518, XCLK1 and CHAMP-AV8, the ADC, FPGA, and Core i7

processor provide a full range of functions. The FMC-518 FMC converts 4 analog channels of

250 MHz to digital data and passes this data to the Virtex-7 FPGAs on the CHAMP-FX4.

Figure 3.

To insure that all 16 inputs are sampled with aligned clocks, the XCLK1 XMC installed on the

CHAMP-AV8 provides aligned clocks to the 4 FMCs, and insures they all start sampling at the

same time.