MOSFETS-updated

advertisement

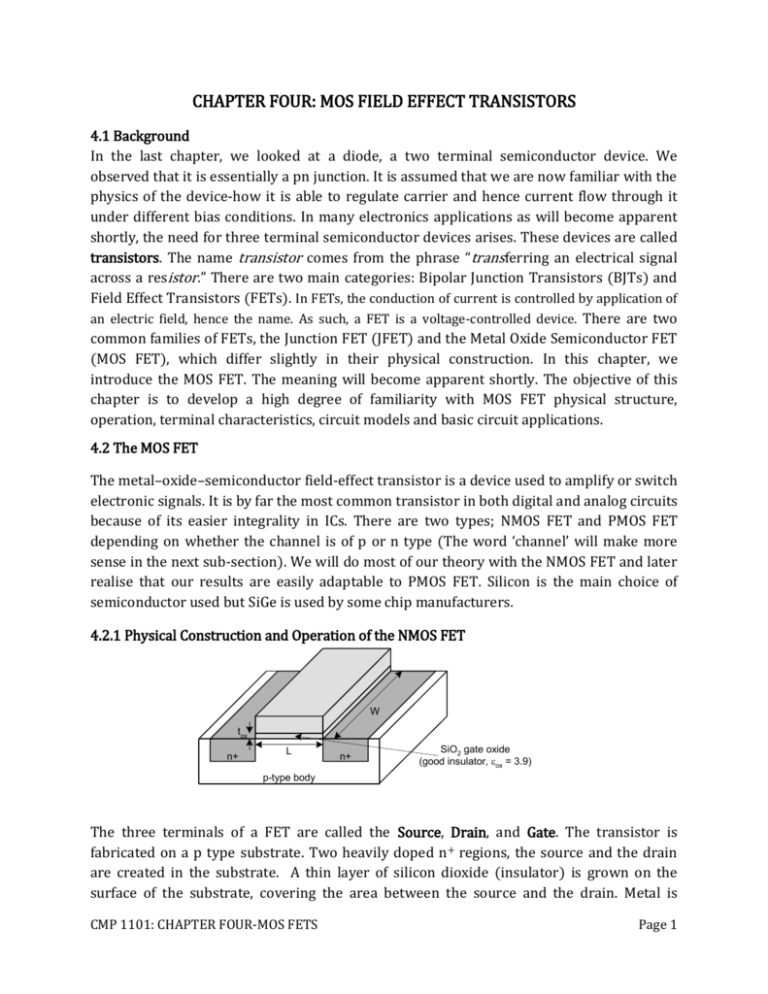

CHAPTER FOUR: MOS FIELD EFFECT TRANSISTORS 4.1 Background In the last chapter, we looked at a diode, a two terminal semiconductor device. We observed that it is essentially a pn junction. It is assumed that we are now familiar with the physics of the device-how it is able to regulate carrier and hence current flow through it under different bias conditions. In many electronics applications as will become apparent shortly, the need for three terminal semiconductor devices arises. These devices are called transistors. The name transistor comes from the phrase “transferring an electrical signal across a resistor.” There are two main categories: Bipolar Junction Transistors (BJTs) and Field Effect Transistors (FETs). In FETs, the conduction of current is controlled by application of an electric field, hence the name. As such, a FET is a voltage-controlled device. There are two common families of FETs, the Junction FET (JFET) and the Metal Oxide Semiconductor FET (MOS FET), which differ slightly in their physical construction. In this chapter, we introduce the MOS FET. The meaning will become apparent shortly. The objective of this chapter is to develop a high degree of familiarity with MOS FET physical structure, operation, terminal characteristics, circuit models and basic circuit applications. 4.2 The MOS FET The metal–oxide–semiconductor field-effect transistor is a device used to amplify or switch electronic signals. It is by far the most common transistor in both digital and analog circuits because of its easier integrality in ICs. There are two types; NMOS FET and PMOS FET depending on whether the channel is of p or n type (The word ‘channel’ will make more sense in the next sub-section). We will do most of our theory with the NMOS FET and later realise that our results are easily adaptable to PMOS FET. Silicon is the main choice of semiconductor used but SiGe is used by some chip manufacturers. 4.2.1 Physical Construction and Operation of the NMOS FET polysilicon gate W tox n+ L n+ SiO2 gate oxide (good insulator, ox = 3.9) p-type body The three terminals of a FET are called the Source, Drain, and Gate. The transistor is fabricated on a p type substrate. Two heavily doped n+ regions, the source and the drain are created in the substrate. A thin layer of silicon dioxide (insulator) is grown on the surface of the substrate, covering the area between the source and the drain. Metal is CMP 1101: CHAPTER FOUR-MOS FETS Page 1 deposited on top of the oxide to from the Gate (G) electrode to the device, and to the Source (S), the Drain (D) and the substrate, the Body (B). The generic name of the device should make sense now! We note that the substrate forms pn junctions with the source and drain regions. In normal operation, the source and the substrate are kept at the same potential (normally ground), so we effectively have three terminals: G, S, and D. Voltage applied to the gate controls current flow between the source and the drain, through a region called the channel of length L and width W. 4.2.2 Operation with no Bias Voltage Since two back to back diodes exist in series between the source and the drain; one between the source and the substrate and the other between the substrate and the drain, there is no current flow when no bias is applied to the gate. 4.2.3 Creation of a Channel When a potential VGS is applied between the source and gate, free holes are repelled from the region of the substrate just below the gate, leaving a depletion region-the channel. Reflection: What type of bound charge is in this region? The positive voltage at the gate attracts free electrons from the source and drain into the channel created. If a sufficient number of electrons accumulate in this region, we in effect have an n region below the gate connecting the source and the drain. If a sufficiently positive voltage is now applied between the source and the drain, current flows between the two by way of electrons in the above induced n region. Now you know why it is called a channel, because it connects the source and drain and enables current flow between them. The MOSFET we are considering now is aptly called an n-channel MOSFET or simply NMOS FET. The value of VGS at which a sufficient number of electrons accumulate in the channel region to form a conducting channel is known as the threshold voltage, Vt. It lies between CMP 1101: CHAPTER FOUR-MOS FETS Page 2 0.5 and 1 V. The thickness of the channel is proportional to VGS-Vt. The gate and the channel form a parallel plate capacitor with the oxide as the dielectric. This vertical electric field controls the amount of charge and hence the conductivity of the channel. 4.2.4 Applying a Small VDS When a small VDS is applied (say 50mV), electrons travel from the source to the drain (names ring a bell?) hence current iD flows from the drain to the source (opposite direction to electron flow). The magnitude of the current depends on the density of electrons in the channel, which in turn depends on VGS. If VGS=Vt, negligible current flows. Above Vt, the channel behaves like a resistor, hence the iD-VDS relationship is linear, with the slope of the graph being the conductance. The conductance of the channel and hence the current depends on 𝑉𝐺𝑆 − 𝑉𝑡 , also known as the effective voltage. Since an increase in VGS above Vt enhances channel conductance, you will sometimes find our MOSFET called an enhancement type NMOS FET. Note that iD=iS so iG=0. Draw and explain the shape of the iD against VDS curves at various values of 𝑽𝑮𝑺 − 𝑽𝒕 . 4.2.5 Increasing VDS at Constant VGS The above current-voltage variation is valid for small values of VDS such that VGD=VGS-VDS≈ 𝑉𝐺𝑆 and the induced channel is uniform. For a given VGS >Vt, if VDS is increased, VGD=VGSVDS becomes smaller than VGS. As such, the size of the channel near the source becomes smaller compared to that near the source as shown above. The effect is more prominent as VDS is increased and the channel resistance increases. The iD against VDS curve bends. When VDS is increased to such an extent that VGS-VDS= Vt at the drain end, the channel depth is negligible at the drain end, and the channel is said to be pinched off. Increasing VDS beyond this value has no effect on iD and the current is said to have saturated. iD now depends on only VGS. The MOSFET is said to have entered the saturation region at a value of VDS given CMP 1101: CHAPTER FOUR-MOS FETS Page 3 by VDSat = VGS-Vt. The characteristic region defined by VDS< VDSat is known as the ohmic/ triode region. Example 1 Explain the operational characteristics of the MOSFET shown below. Solution The MOSFET can be categorized into three separate modes when in operation. ➢ The cut-off mode: VGS < Vt, where Vt is the threshold voltage. For the above characteristic curves, Vt = 1V. In this mode the device is essentially off, and in the ideal case there is no current flowing through the device. ➢ The ohmic/triode region when VGS > Vt and VDS < VGS − Vt such that a channel is formed and it is not pinched off. The MOSFET operates as a voltage controlled resistor in this mode. ➢ The Active or Saturation mode which occurs when VGS > Vt and VDS > VGS − Vt and part of the channel is cut off. iD is independent of VDS. This mode corresponds to the region to the right of the dotted line, which is called the pinch-off voltage. Pinchoff occurs when the MOSFET stops operating in the linear region and saturation occurs. Note: In digital circuits MOSFETS are only operated in the linear mode, while the saturation region is reserved for analogue circuits. CMP 1101: CHAPTER FOUR-MOS FETS Page 4 4.2.6 The iD-VDS Relationship From the physical operation of the device above, we can derive the expression relating i D to VDS and VGS. Some parameters will be useful: W Channel Width L Channel Length Cox capacitance per unit gate area of the dielectric (silicon dioxide), 𝐶𝑜𝑥 = 𝜀𝑜𝑥 𝑡𝑜𝑥 where 𝜀𝑜𝑥 is the permittivity of silicon dioxide (3.9𝜀𝑜 ) and 𝑡𝑜𝑥 is the thickness of the gate oxide. 𝜇𝑛 Mobility of electrons in the channel 𝜇𝑛 𝐶𝑜𝑥 = 𝑘𝑛 Process transconductance parameter In the triode region, 𝒊𝑫 = 𝒌𝒏 𝑾 𝑳 𝟏 [(𝑽𝑮𝑺 − 𝑽𝒕 )𝑽𝑫𝑺 − 𝑽𝟐𝑫𝑺 ]. Note that if VDS << VGS, the MOSFET acts as a linear 𝟐 resistor where the resistor, rDS ≈ 1 2𝑘𝑛 (𝑉𝐺𝑆 −𝑉𝑡 ) . In the saturation region, we substitute VDS with VGS-Vt in the expression above yielding 𝟏 𝒊𝑫 = 𝟐 𝒌𝒏 The ratio 𝑾 𝑳 𝑊 𝐿 (𝑽𝑮𝑺 − 𝑽𝒕 )2 is known as the aspect ratio of the MOSFET. How would you write the above equations if K was defined as 𝒌𝒏 𝑾 𝟐𝑳 ? As can be seen from the physical structure of the device, the MOSFET is a symmetric device, thus the source and the gate can be interchanged without any change in device properties. For most applications though, the source is connected to the body, yielding a three terminal element and the terminals are then no longer interchangeable. The circuit symbol for NMOS is shown below, first with the body and then without. By convention, i D flows into the gate. CMP 1101: CHAPTER FOUR-MOS FETS Page 5 Rather than indicating the direction of current flow, the arrow actually shows the direction of the underlying pn junction, inwards for p and outwards for n type. Example 2 For a MOSFET with 𝐿 = 0.4𝜇𝑚, 𝑡𝑜𝑥 = 8𝑛𝑚, 𝜇𝑛 =450𝑐𝑚2 /𝑉𝑠 and Vt= 0.7 V, a) Find 𝐶𝑜𝑥 and 𝐾𝑛 (4.32 x 10-3 F/m2, 194𝝁A/V2) b) For a MOSFET with 𝑊 𝐿 = 1, find the values of VGS and VDS needed to operate the transistor in saturation with iD = 100 𝜇𝐴. (1.02V, 0.32 V) 4.3 Solving NMOS Circuits To solve the circuits, we assume that NMOS is in a particular state, use NMOS model for that state to solve the circuit and check the validity of our assumption by checking the inequalities in the model for that state. A formal procedure is: i. Write down a KVL including GS terminals (call it GS-KVL). ii. Write down a KVL including DS terminals (call it DS-KVL). iii. From GS-KVL, compute VGS (using iG = 0) a) If VGS < Vt, NMOS is in cut-off. Let iD = 0, solve for VDS from DS-KVL. We are done. b) If VGS > Vt, NMOS is not in cut-off. Go to step 4. 1 𝑊 iv. Assume NMOS is in active region. Compute iD from 𝑖𝐷 = 2 𝑘𝑛 𝐿 (𝑉𝐺𝑆 − 𝑉𝑡 )2, then, use DS-KVL to compute VDS. If VDS > VGS -Vt, we are done. Otherwise go to step 5. v. NMOS has to be in ohmic region. Substitute for iD from 𝑖𝐷 = 𝑘𝑛 1 𝑊 𝐿 [(𝑉𝐺𝑆 − 𝑉𝑡 )𝑉𝐷𝑆 − 𝑉2 ] 2 𝐷𝑆 in DS-KVL. You will get a quadratic equation in VDS. Find VDS (one of the two roots of the equation will be unphysical). Check to make sure that VDS < VGS - Vt. Substitute VDS in DS-KVL to find iD. CMP 1101: CHAPTER FOUR-MOS FETS Page 6 Example 3 12V RD 1kΩ ID Vo D Vi G 2N6659 S For the NMOS circuit shown, with K= 0.25 mA/V2 and Vt =2V, find Vo when Vi=0, 6, and VDD = 12V. Solution GS KVL: VGS=Vi DS KVL: 𝑉𝐷𝐷 = 𝑅𝐷 𝐼𝐷 + 𝑉𝐷𝑆 Case 1 When Vi=0, GS KVL: VGS=0, Hence GS KVL: VGs< Vt, NMOS are in cut-off. ID=0. DS KVL, 𝑉𝑜 = 𝑉𝐷𝐷 − 𝐼𝐷 𝑅𝐷 =12V Case 2 When Vi=6 V, GS KVL: VGS=6V which is greater than Vt. The NMOS is not in cut-off. Let us assume the transistor to be in the active region: 𝑖𝐷 = 𝐾(𝑉𝐺𝑆 − 𝑉𝑡 )2 𝑖𝐷 = 0.25(6 − 2)2 = 4mA. DS KVL: 𝑉𝐷𝑆 = 𝑉𝐷𝐷 − 𝑅𝐷 𝐼𝐷 = 12 = 1(4) = 8𝑉 Since VDS > VGS -Vt , the transistor is indeed in the active region and ID = 4mA and Vo =VDS = 8 V. CMP 1101: CHAPTER FOUR-MOS FETS Page 7 Case 3 When Vi=12 V, GS KVL: VGS=12V which is greater than Vt. The NMOS is not in cut-off. Let us assume the transistor to be in the active region: 𝑖𝐷 = 𝐾(𝑉𝐺𝑆 − 𝑉𝑡 )2 𝐼𝐷 = 0.25(12 − 2)2 = 25mA. DS KVL: 𝑉𝐷𝑆 = 𝑉𝐷𝐷 − 𝑅𝐷 𝐼𝐷 = 12 = 25(1) = −13𝑉 Since VDS < VGS -Vt , the transistor is not in the active region. Assume the transistor is in the linear region. 2 2 𝐼𝐷 = 𝐾[2(𝑉𝐺𝑆 − 𝑉𝑡 )𝑉𝐷𝑆 − 𝑉𝐷𝑆 ]= 0.25 X 10-3 [2(12 − 2)𝑉𝐷𝑆 − 𝑉𝐷𝑆 ] 2 Substituting ID in DS-KVL, we get 12= 103 X 0.25 X 10-3 [2(10)𝑉𝐷𝑆 − 𝑉𝐷𝑆 ] +𝑉𝐷𝑆 2 𝑉𝐷𝑆 − 24𝑉𝐷𝑆 +48 =0. Solving these two equations yields 𝑉𝐷𝑆 = 2.2 𝑉 and 𝑉𝐷𝑆 = 21.8 𝑉. The second root is unphysical so 𝑉𝐷𝑆 = 2.2 𝑉 = 𝑉𝑜 . Since 2.2 < 𝑉𝐺𝑆 − 𝑉𝑡 =10V, the transistor is truly in the linear region. From DS-KVL, 𝐼𝐷 = 𝑉𝐷𝐷−𝑉𝐷𝑆 𝑅𝐷 12−2.2 = 1000 = 9.8𝑚𝐴. Note that what we have discussed above yields the large signal MOS FET model. In saturation, observe that the MOSFET provides a drain current whose value is independent of the drain voltage. Thus, the MOSFET behaves as an ideal current source represented by the model below: CMP 1101: CHAPTER FOUR-MOS FETS Page 8 4.4 Finite Output Resistance in Saturation We assumed above that in saturation, iD is independent of VDS. However, it is realised that as VDS is increased further, the pinch off point moves slightly away from the drain, towards the source. The channel length is in effect reduced, a phenomenon known as channel length modulation. It can be shown that our equation for saturation current changes to 1 𝑖𝐷 = 2 𝑘𝑛 𝑊 𝐿 (𝑉𝐺𝑆 − 𝑉𝑡 )2 (1 + ℷ 𝑉𝐷𝑆 ), ℷ is a parameter for a given MOSFET design. The characteristic curves now change shape: From the equation, what is VDS when iDS =0? When the curves are extrapolated, they cut the VDS axis at a common voltage, -VA, known as Early Voltage. We get the finite output resistance in saturation by getting the inverse of the derivative if iD wrt VDS. We end up with 𝑟𝑜 = [ℷ 1 ℷ𝐼𝐷 or simply 𝑉𝐴 𝐼𝐷 𝑘𝑊 2𝐿 −1 (𝑉𝐺𝑆 − 𝑉𝑡 )2 ] which can be written as where ID is the drain current without channel length modulation. The output resistance is hence inversely proportional to the drain current ands the large signal equivalent model is modified to become: CMP 1101: CHAPTER FOUR-MOS FETS Page 9 4.4 The P Channel Enhancement Type MOSFET The physical structure is similar to that of NMOS except that the semiconductor type for the substrate, the source and the channel are interchanged. (The body is now n type while the source and the drain are of p type). A p type channel results. All the voltages are now reversed. By convention, drain current flows out of the drain and into the source. Below are the circuit symbols, first with the body and then the simplified version when the source is connected to the body. What are the advantages of NMOS over PMOS? The following operation characteristics apply: Cut off: VGS > Vt for any VDS. Ohmic/Linear region: VGS < Vt and VDS > VGS -Vt, 𝑖𝐷 = 𝑘𝑛 𝑊 𝐿 1 2 [(𝑉𝐺𝑆 − 𝑉𝑡 )𝑉𝐷𝑆 − 𝑉𝐷𝑆 2 𝑊 Active/Saturation: VGS < Vt and VDS < VGS -Vt, 𝑖𝐷 = 𝑘𝑛 2𝐿 (𝑉𝐺𝑆 − 𝑉𝑡 )2 Note that the above equations are obtained by multiplying the corresponding NMOS expressions by a negative sign. Vt is also negative. CMP 1101: CHAPTER FOUR-MOS FETS Page 10