review for elec 105 midterm exam #1 (fall 2001)

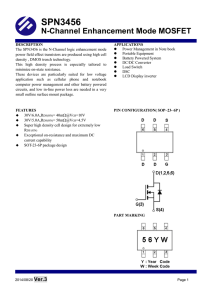

advertisement

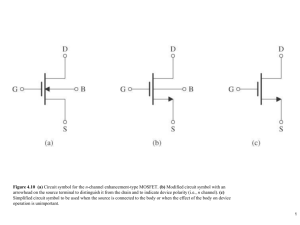

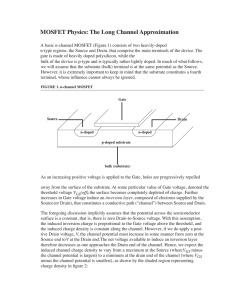

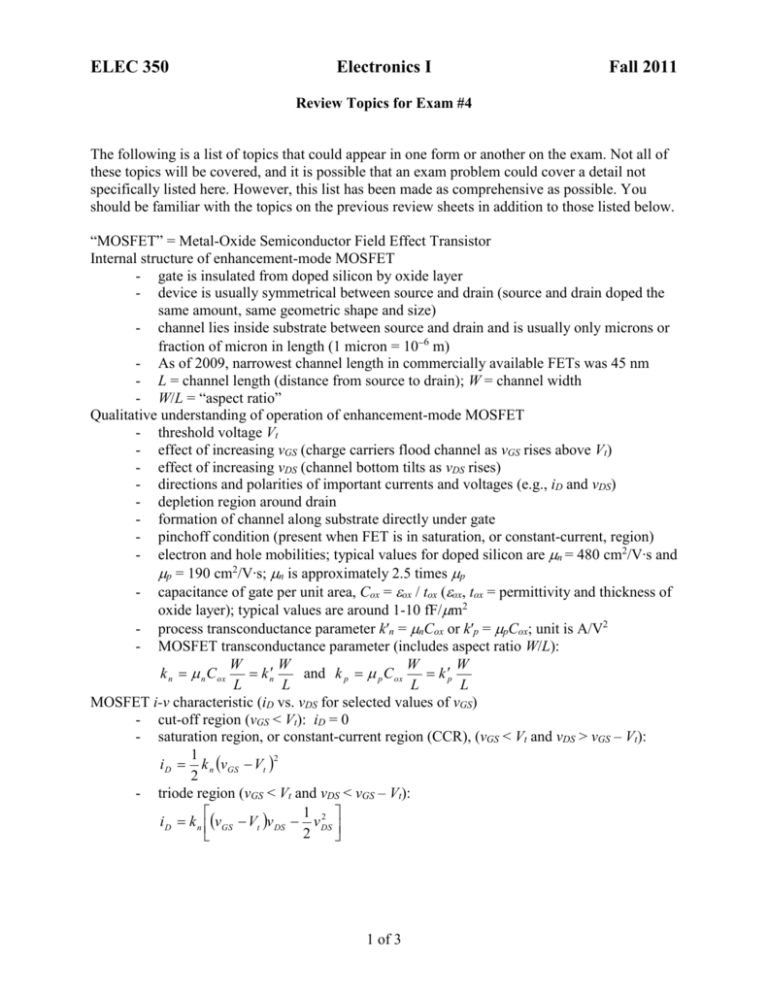

ELEC 350 Electronics I Fall 2011 Review Topics for Exam #4 The following is a list of topics that could appear in one form or another on the exam. Not all of these topics will be covered, and it is possible that an exam problem could cover a detail not specifically listed here. However, this list has been made as comprehensive as possible. You should be familiar with the topics on the previous review sheets in addition to those listed below. “MOSFET” = Metal-Oxide Semiconductor Field Effect Transistor Internal structure of enhancement-mode MOSFET - gate is insulated from doped silicon by oxide layer - device is usually symmetrical between source and drain (source and drain doped the same amount, same geometric shape and size) - channel lies inside substrate between source and drain and is usually only microns or fraction of micron in length (1 micron = 106 m) - As of 2009, narrowest channel length in commercially available FETs was 45 nm - L = channel length (distance from source to drain); W = channel width - W/L = “aspect ratio” Qualitative understanding of operation of enhancement-mode MOSFET - threshold voltage Vt - effect of increasing vGS (charge carriers flood channel as vGS rises above Vt) - effect of increasing vDS (channel bottom tilts as vDS rises) - directions and polarities of important currents and voltages (e.g., iD and vDS) - depletion region around drain - formation of channel along substrate directly under gate - pinchoff condition (present when FET is in saturation, or constant-current, region) - electron and hole mobilities; typical values for doped silicon are n = 480 cm2/V∙s and p = 190 cm2/V∙s; n is approximately 2.5 times p - capacitance of gate per unit area, Cox = ox / tox (ox, tox = permittivity and thickness of oxide layer); typical values are around 1-10 fF/m2 - process transconductance parameter k′n = nCox or k′p = pCox; unit is A/V2 - MOSFET transconductance parameter (includes aspect ratio W/L): W W W W k n n C ox k n k p and k p p C ox L L L L MOSFET i-v characteristic (iD vs. vDS for selected values of vGS) - cut-off region (vGS < Vt): iD = 0 - saturation region, or constant-current region (CCR), (vGS < Vt and vDS > vGS – Vt): 1 2 i D k n vGS Vt 2 - triode region (vGS < Vt and vDS < vGS – Vt): 1 2 i D k n vGS Vt v DS v DS 2 1 of 3 n-channel vs. p-channel MOSFETs (NMOS and PMOS) - comparison of electron mobility n vs. hole mobility p (hole mobility is approximately 0.4 times electron mobility for doped Si) - vGS, vDS, and Vt are all negative for enhancement-mode PMOS - iD is positive for both types (Sedra and Smith’s convention) - i-v characteristics of NMOS and PMOS have voltages of opposite sign MOSFET circuit symbols - n-channel vs. p-channel - simpler symbol when substrate is tied to source internally - pay attention to directions of arrows MOSFET substrates - NMOS substrate (which is made of p-type material) must be connected to most negative voltage in circuit - PMOS substrate (which is made of n-type material) must be connected to most positive voltage in circuit CMOS digital logic gates - use no resistors - negligible drain current once equilibrium is established after logical state change - MOSFETs are either in cutoff (“off”) or triode region (vDS ≈ 0) in all logical states General analysis techniques for MOSFET circuits - determination of region of operation (cutoff, saturation, or triode) - vDS for n-channel MOSFETs will always be zero or positive (negative for PMOS) - graphical analysis techniques (load lines) can be applied - resolution of sign ambiguities when quadratic formula is required due to square-law dependence of iD on vGS Distinction between bias, signal, and total voltages and currents - signals are usually time-varying, but don’t have to be - signals contain information (audio, video, data, sensor outputs, etc.) - bias conditions (DC levels) define the “Q-point” (quiescent point) - total voltage or current is sum of bias and signal components (superposition) - conventions: o lower-case variable w/upper-case subscript: total (DC + signal) quantity o upper-case variable w/upper-case subscript: quiescent DC quantity o lower-case variable w/lower-case subscript: signal (AC) quantity Concept of biasing and why it is necessary Use of MOSFET with low vDS as a variable resistor - acts as a voltage controlled resistor; sometimes used in attenuator circuits - channel under gate has almost constant depth along length 1 - rDS , where v is the voltage across the MOSFET (v = vGS = vDS) k n v Vt MOSFETs in “diode connected transistor” configuration - useful for biasing on IC chips without using resistors - gate tied to drain, so vGS = vDS - FET is almost always in saturation region, never in triode region 1 2 - i D k n v Vt , where v is the voltage across the MOSFET (v = vGS = vDS) 2 - PMOS devices can also be configured this way; i-v characteristic is 1 2 i D k p v Vt 2 2 of 3 Biasing MOSFET circuits - design for quiescent output voltage, drain current, and/or voltage drop across source resistor - usually bias MOSFET for operation in the saturation region - must pay attention to swing range of vD to avoid cutoff and triode regions o in cutoff region, iD = 0; this is also true at the boundary between the cutoff and saturation regions o saturation-triode boundary defined by (for NMOS devices): VD sat.triode VG Vt or VDS sat.triode VGS Vt - the parameters kn and Vt have strong temperature dependence and device variation - parameter-independent biasing (source degeneration), or “4-resistor” biasing 2 o must satisfy I D 0.5k n VGS Vt and VGS VG I D RS simultaneously o square-law relationship sometimes leads to solution of quadratic equations o must determine which solution to quadratic equation is the physical solution V Vt 1 1 o exact solution: I D G 1 k n RS VG Vt 2 RS k n RS k n RS2 1 o rule of thumb: I D RD I D RS VDD and VG I D RS Vt 2 I D k n 3 RB - establishment of gate bias voltage simplified because IG = 0: VG VDD R A RB - gate biasing resistors should be in the M range (at least 100s of k) DC blocking capacitors - act as open circuits at DC - act as short circuits (or have sufficiently low reactance) at signal frequencies - isolate DC biasing from effects of source and/or load Relevant course material: HW: Labs: Textbook: Lecture notes: Web Links: Mathcad: Matlab: #6 #7 #9 #11 Sections 5.1 through 5.4; 5.7 (none) (none) (none) (none) 3 of 3