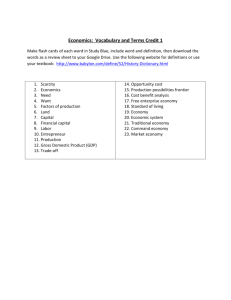

Standard cells – in IC design

advertisement

Budapest University of Technology and Economics Department of Electron Devices Integrated circuits, IC design IC design: CAD tools, a design flow, design rules pre-fabrication, pre-design, standard cell design http://www.eet.bme.hu/~poppe/miel/en/17-ICdesign2.ppt http://www.eet.bme.hu Budapest University of Technology and Economics Department of Electron Devices Manufacturing and design ► Manufacturing plants (fabs) are more and more expensive Order of magnitude of billion US $ (huge CapEx costs) Less and less advanced fabs world-wide ► Using the processes is getting also more expensive Due to costs of masks, NRE (non-recurring engineering cost) of the advanced IC-s is increasing ► Few fabs – many designers waferless fab – e.g. Silicon Labs, Duolog Design and manufcaturing are strictly separated, but for proper design one has to be aware of the basics of the manufacturing processes and the physical operation of the devices. 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 2 Budapest University of Technology and Economics Department of Electron Devices Ways of reducing costs ► Pre-design Example: standard cell design (see details later) Essentially: ► Pre-fabrication We work with pre-design circuit elements (both in terms of schematics and layout). (see also pre-fab buildings) Extreme example of the pre-fab principle for digital circuits: FPGA (Altera, Xilinx) FPGA = field programmable gate array It’s a matrix of logic gates with user programmable interconnections Includes everything which is needed for a digital circuit. The NRE of manufacturing is distributed over among a huge number of manufactured IC-s. Costs of individual circuit design are only the cost of preparing a HDL description of the circuit. Most popular realization technique today. 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 3 Budapest University of Technology and Economics Department of Electron Devices Ways of reducing costs ► MPW – multi-project wafer One wafer – joint manufacturing of multiple designs: typically 10-20 designs on the same wafer Individual design Individual fabrication costs (NRE-s): 10-20 fold reduction per design prototyping / small volume production See details later 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 4 Budapest University of Technology and Economics Department of Electron Devices CAD tools in VLSI design Simulator: Representation: Behavioral description System simulator Abstraction level System level design Specification in VHDL or in Verilog Synthesis Logic level design Logic simulation Structural description Layout generation Timing parameters Circuit simulator Layout description Device parameters Schematic editor Transistor level design Layout editor Design rules Physical device simulation Process and device design: TCAD tools used in Process siliconsimulation foundries. Ordinary designers do not use such tools. 1-12-2009 Optimization IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 5 Budapest University of Technology and Economics Department of Electron Devices CAD tools in VLSI design ► Circuit entry Textual: using hardware description languages or HDLs (e.g.: Verilog, VHDL) • behavioral description (Verilog, VHDL, SystemC) • structural description (Verilog, VHDL) Graphical: schematic entry (structural description) ► Simulation (on all abstraction levels) system level, gate level logic, transistor/circuit results visualization tools tools for conceptual design, physical design verification tools ► ► High level synthesis: behavioral → RTL → structural Layout synthesis On all abstraction levels a given representations of the design – data bases 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 6 Budapest University of Technology and Economics Department of Electron Devices Technology independence The elements of CAD frameworks listed do not show any dependence on the realization technology! How is it possible? ► IC process design – application (circuit) design: strictly separated. ► Link between them: design rules, device parameters. What are the consequences of this? ► Open design frameworks (the same software for various processes, realization mode, e.g. Mentor Graphics for ICs and FPGAs). ► Digital IC design does not need deep knowledge of microelectronics. (But analog design does!) 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 7 Budapest University of Technology and Economics Department of Electron Devices Design rules ► Simple geometrical rules regarding the realization of the layout ► Depend on the minimal feature size (MFS) ► Typical examples: Minimal sizes of shapes on different masks Minimal distances between two shapes on the same mask or on two different masks Minimal overlaps of shapes on two masks etc 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 8 Budapest University of Technology and Economics Department of Electron Devices based design rules ► based rules: = 2(resolution of the process, MFS) The rules – as geometrical data – are defined in terms of The layout shapes are also aligned to a grid with a size of ► Advantage: easier porting of a layout to another process with a different MFS easier scaling down of a layout (in case of advanced process one has to be careful with scaling) since only the value of has to be redefined. 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 9 Budapest University of Technology and Economics Department of Electron Devices Typical based rules ► width of the active zone (doped region): 2 ► spacing between shapes on active layer: 3 (due to the depletion layer) 2 3 ► poly-Si: line width, spacing: 2 ► metallization lines’ width, spacing: 3 (due to oxide steps / step coverage) 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 10 Budapest University of Technology and Economics Department of Electron Devices Typical based rules ► size of contact windows: 2 ► Contact window – metal spacing: 2 ► gate overlap over active, etc. 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 11 Budapest University of Technology and Economics Department of Electron Devices The process flow of the IC design ► ► ► ► ► 1-12-2009 Specs Pre-fabrication, pre-design The design flow – through the example of standard cell design Hierarchical design (top-down, bottom-up) Global layout: floorplan IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 12 Budapest University of Technology and Economics Department of Electron Devices Specification – first design step ► Technical specification (global) What is the very function that we want to realize in electronics? (E.g. digital control of a model railway layout) • Create a system model e.g. in UML ► Financial aspects What is the final product where the IC will be used? What is cost proportion from the cost budget of the final product? Are there any cost limits? • E.g. pocket calculator – most of the costs is related to the enclosure, keyboard, display ► Other aspects E.g. copy safe solution is needed (military/aerospace or other high added value electronics) 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 13 Budapest University of Technology and Economics Department of Electron Devices Specification – first design step ► Other aspects (cont.) Small space (see model railway - decoder should fit even into an N or Z scale loc) Minimal power consumption: battery operated devices, hand-held devices – see laptop, mobil (low power design) Low supply voltage – e.g. 1.5V (low voltage design) competitiveness • time-to-market • technological advantage Vulnerability to other vendors • E.g. FPGA based design – is the given FPGA still available? • Question of 2nd sourcing ► Standards E.g. in some aerospace applications no volatile devices 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 14 Budapest University of Technology and Economics Department of Electron Devices Final specification, phase 1 ► Decide what will be analog, what will be digital E.g. control of a model railway layout: • digital IC – multiple analog circuitry around different functions – Loc decoder, – Switching point decoder, – Signal decoder ► In case of digital components: HW-SW co-design and partitioning (considering yet other cost factors and cost functions) ► Optimize major parameters of digital HW such as Width of data and address buses, Sizing memories, etc. 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 15 Budapest University of Technology and Economics Department of Electron Devices Final specification, phase 2 ► Specs of major HW components fixed in an universal way: describe in HDL Behavioral description – completely independent of the realization mode • This is the exact specification of the component • Suitable for formal verification: – Does it really do what we imagined? This is turned into a structural description (manually or through synthesis) kézzel vagy szintézissel) – this still can be independent of the final realization mode And finally we describe how the designed module has to be tested (prepare a so called test bench – description of stimuli used in logic simulation) E.g. US DoD also requires these, all given in VHDL ► IP is described in a technology independent way 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 16 Budapest University of Technology and Economics Department of Electron Devices Choice of realization mode ► What is it influenced by? Expertise of the designers available Available design tools Non-technical aspects: • Financial and time constraints, need for copy safe solution, control of production through the ownership of a key component, competitiveness, etc. E.g. : • Prototype urgently needed – FPGA • Large volume (100k pcs) is planned – dedicated (custom) IC 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 17 Budapest University of Technology and Economics Department of Electron Devices Example: signal processing S&H ► ► A/D A() A() purely analog realization or digital filtering: from A() we create its Z-transform storage/delay units multipliers adders ► D/A Realization mode: The design process can be fully automated DSP + software • flexibile, easy to realize other transfer characteristics • not copy-safe, volatile, possibly complex environment Dedicated hardware: • Storage/delay – shift register, adder/multiplier – combinational logic – FPGA – is also reprogrammable – Dedicated IC – frozen architecture 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 18 Budapest University of Technology and Economics Department of Electron Devices Example: signal processing ► ► ► A() Z(n) – automatic Z(n) modules – automatic or digital filtering: from A() we create its Z-transform storage/delay units multipliers adders ► Realization mode: DSP + software • flexibile, easy to realize other transfer characteristics • not copy-safe, volatile, possibly complex environment Dedicated hardware: • Storage/delay – shift register, adder/multiplier – combinational logic – FPGA – is also reprogrammable – Dedicated IC – frozen architecture – there are furthere choices here as well: » element matrix design » standard cell design 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 19 Budapest University of Technology and Economics Department of Electron Devices Pre-fabrication – smaller costs ► ► ► General principle in the industry (see also the construction/building industry – pre-fab houses), Reduction of the NRE per single unit In Microelectronics: Pre fabricate as many things as possible • Pre fabrication on Si wafer: – except the last metallization pattern wafer completely processed (1 mask is needed only) – pre-fabricated elements (transistors or even complete logic gates) in a matrix arrangement: array type (element matrix) circuits » MOS transistors – ULA (uncommitted logic array), assuming nMOS process » gate array – GA, in CMOS » final circuit: realization of interconnection between matrix elements by means of the mask of the last metallization pattern » problem: element utilization, costs, turnaround time – nowadays not popular • completely pre-fabricated, packaged IC – programmable devices: » CTRL, DSP, PLA, EPROM, FPGA (field programmable GA) » cost effective and flexible solutions Nowadays FPGAs tend to dominate towards custom ICs, since NRE-s of custom ICs are bery high, therefore large manufacturing volumes are economical only. "Empty" FPGAs can be produced in large volume. 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 20 Budapest University of Technology and Economics Department of Electron Devices Programming gate arrays Programming mask Density cost low metallization mask only metallization + contact window mask metalliaztion + contact + doping mask ... full custom 1-12-2009 high IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 21 Budapest University of Technology and Economics Department of Electron Devices Pre-design – reduced costs ► It is not worthwhile to design logic gates, latches, registers, MUX-s etc. for every new IC they are always the same (same stick diagram layouts) they are used frequently – re-use ► Let us pre-design such elements and let us standardize them standard cells ► "Standard cells" in a general sense exist in case of all kinds of IC design styles ► Design costs can be radically reduced 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 22 Budapest University of Technology and Economics Department of Electron Devices "Standard cells" – generally ► In hardware design PCB: off-the-self IC-s (such as SN series, others) FPGA: pre-designed codes gate array: interconnected circuit elements on metallization mask standard cellás IC: the cells themselves – detailed layouts of logic gates full custom IC: parts of the full layout are ready blocks: standard cells, larger blocks like RAMs, ROMs, IP blocks provided by their layouts, etc. 1-12-2009 ► In software library routines (e.g. C libraries – math.h, etc) C++ classes (class libraries) IP blocks: A circuit block given as a synthetizable high level description by means of an HDL "code". (Synthetizable down to the ultimate detailed layout.) IP == intellectual property Even complete processor cores are available in HDL at so called IP brokers. These can be mapped to an FPGA or to an IC process. IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 23 Budapest University of Technology and Economics Department of Electron Devices Standard cells – in IC design ► Basic building blocks being used in case of design of monolithic IC-sMonolitikus IC-k tervezésénél logic gates some more complex functions ► Pre-designed, error free layout, fully tested functionality some constraints in their layout • fixed height (but variable width) • signal pins – at given raster positions • VDD and GND access: at fixed position these constraints help simplify the operation of automatic CAD tools performing the physical design of the IC 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 24 Budapest University of Technology and Economics Department of Electron Devices Comparison 1. full cust. std. cell. above 106 OK 1 year Realization costly, slow costly above around always 4 3 10 OK 10 OK OK 4 months 4 months immediately cheap, cheap, function quick quick only costly medium cheap below 103 OK 1 week.. 1 year cheap, quick cheap Complexity high high medium high - Possibility to copy hard hard medium hard easy Cost turnaround Design 1-12-2009 gate arr. IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 FPGA PCB 25 Budapest University of Technology and Economics Department of Electron Devices Comparison 2. Price Gate array Std. cell Full custom PCB 103 1-12-2009 104 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 106 Volume [pcs] 26 Budapest University of Technology and Economics Department of Electron Devices Standard cell design ► cell library ► in the library geometrical constraints for every element identical height (any width), supply and ground lines at identical position signal pints on a given grid either on the top or bottom of the cells ► regular chip layout: cell rows, routing channels for interconnects 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 27 Budapest University of Technology and Economics Department of Electron Devices Standard cells of gates ► The CMOS inverter layout shown before has also been created according to conventions of standard cell design Supply pins out out G G D signal pins GND nMOS S D pMOS G G S VDD in in Cell layout macro outline 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 28 Budapest University of Technology and Economics Department of Electron Devices Standard cells ► In layout view on can refer to the inverter through its layout macro (cell outline and pins) !GND !VDD out out INV in in !VDD !GND 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 29 Budapest University of Technology and Economics Department of Electron Devices Standard cells 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 30 Budapest University of Technology and Economics Department of Electron Devices Standard cella in a row: VDD GND 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 31 Budapest University of Technology and Economics Department of Electron Devices Standard cell IC: routing channel Cell row routing channel supply tree (comb) Cell row routing channel supply tree (comb) Cell row routing channel 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 32 Budapest University of Technology and Economics Department of Electron Devices Detail of a standard cell IC: 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 33 Budapest University of Technology and Economics Department of Electron Devices Contents of the standard cell library ► pre-designed block performing a given logic function, ► fully tested and verified function graphics symbol (for schematic capture) simulation model, timing data (for logic simulation), detailed cell layout or cell outline (macro) prototype of the cell in the HDL used in the design framework ► typical elements: logic gates, latches, ff-s, MUX, DMX, SNxxx, counters, etc. 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 34 Budapest University of Technology and Economics Department of Electron Devices The design flow ► In a given design framework (CAD system), ► for a given design style (such as standard cell design) esetén ► the sequence of usage of tools: which programs, in what order are to be used. ► Prescribed sequence of program usage ► Required files (representation or views of the design) ► Consistency of the required files 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 35 Budapest University of Technology and Economics Department of Electron Devices Standard cell design flow 1 Circuit entry: •schematic capture •HDL •macrocells/ generated element (eg. RAM, ROM blocks) correct stimulus file Functional testing with logic simulation (pre-layout) no yes Description of stimuli Ok? no Are the simulation results Ok? yes no Are the simulation results Ok? yes 1-12-2009 Physical design: •floorplan •detailed layout •package - bonding Functional testing with logic simulation (post-layout): •interconnect delay, •min/nom/max (scatter), •skew IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 36 Budapest University of Technology and Economics Department of Electron Devices Standard cell design flow 2 Ellenőrzések. Pl.: •Pad ring Ok? •Fan-in / fan-out realation Ok? •Are there timing violations at FF-s? •Do min/nom/max simulation results eseentially match? •Skew sensitivity? •Layout DRC Ok? Step back to the required prior design phase mo Collect and submit all required files Is everything Ok? yes Foundry interface: •logic simulation for IC testing •adm issues (eg. design IDs) yes no Is everything Ok? 1-12-2009 Consistency check: •All required steps performed? •Right sequence? Success? •Do required files exist? •Are they consistent? IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 37 Budapest University of Technology and Economics Department of Electron Devices Files to be submitted to the foundry ► circuit description (netlist, HDL) ► complete layout in detail ► description of the test (test vectors and corresponding responses) ► Packaging and bonding information (bonding diagram) ► Admin 1-12-2009 IDs IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 38 Budapest University of Technology and Economics Department of Electron Devices Design methodologies ► Top-down design: From the more complex system design towards simpler building blocks: designs are always partioned into simpler ones until the resulting simpler functionality is not available as an existing block (standard cell, other pre-designed building block etc). HDL-s (Verilog, VHDL, SystemC) mostly support this. 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 39 Budapest University of Technology and Economics Department of Electron Devices Design methodologies ► Top-down design: behavioral description Partitioning: define sub-circuits through their behavioral description Testing these behavioral descriptions by means of simulation Structural description using the behaviroal models of sub-circuits Matching? Simulation Simulation In case of successful partitioning of the circuit continue with the partitioning of the sub-circuits ... 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 40 Budapest University of Technology and Economics Department of Electron Devices Design methodologies ► Bottom-up design: Using basic building blocks (standard cell library elements) sub-circuits are composed. From these sub-circuits, further, more complex subcircuits are composed, etc. until the ultimate specified circuit function is not realized. ► Always a hierarchical circuit description is produced (in both cases) 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 41 Budapest University of Technology and Economics Department of Electron Devices Hierarchical circuit design Top level design: core pads Core: Function_A + Function_B Function_A: Function_AA+ Function_AB Function_BB: Function_BA+ Function_BB Function_AA library element 1-12-2009 library element IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 library element 42 Budapest University of Technology and Economics Department of Electron Devices Hierarchical circuit design 4 to 16 decoder: top level design Input cells Circuit core Supply pads Output cells 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 43 Budapest University of Technology and Economics Department of Electron Devices Hierarchical circuit design 4 to 16 decoder: top level design Circuit core 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 44 Budapest University of Technology and Economics Department of Electron Devices Hierarchical circuit design 2 to 4 decoder with bus 4 to 16 decoder core 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 45 Budapest University of Technology and Economics Department of Electron Devices Hierarchical circuit design dec2to4 2 to 4 decoder, with bus 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 46 Budapest University of Technology and Economics Department of Electron Devices Hierarchical circuit design Library elements: inv, nand Bottom of heierarchy 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 47 Budapest University of Technology and Economics Department of Electron Devices Design flattening ► Breaking down the design hierarchy is called design flattening: Starting with top level design the reference to sub-circuits is replaced by the sub-circuit descriptions This substitutions is continued until the design contains direct references to cells in the library. ► Design 1-12-2009 without hierarchy is called flat design IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 48 Budapest University of Technology and Economics Department of Electron Devices Design flattening Top level design Hierarchical design Sub-circuits Sub-circuits Cell level functions Design flattener program Flat design Cells 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 49 Budapest University of Technology and Economics Department of Electron Devices Produce layout ► Flat design ► Floorplan produce core create pad ring (pad limited, core limited) place cells ► Global routing create routing channels create supply tree a clock tree might also be created ► Detailed routing ► DRC – design rule check 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 50 Budapest University of Technology and Economics Department of Electron Devices The floorplan pad ring with I/O cells This is the global plan of the layout. Locations of major blocks are assigned here. core and corner cells Might require manual work 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 51 Budapest University of Technology and Economics Department of Electron Devices The floorplan Intel Pentium processor – optical microscopic image: layout details are not visible but the floorplan is clearly visible. 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 52 Budapest University of Technology and Economics Department of Electron Devices The floorplan design ► Example: Cadence Opus Floorplan with unplaced pads and standard cells, separated 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 53 Budapest University of Technology and Economics Department of Electron Devices The floorplan design ► Design of the pad ring: manual editing of the so called floorplan file ► Adding corner cells 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 54 Budapest University of Technology and Economics Department of Electron Devices The floorplan design ► The ready floorplan after the alignment of the ring: 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 55 Budapest University of Technology and Economics Department of Electron Devices Next step: place & route ► create routing channels ► global routing ► detailed routing ► errors possible ERC: electric rule checking DRC: design rule checking 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 56 Budapest University of Technology and Economics Department of Electron Devices DRC: design rule check ► The "syntax" check of the layout In case of manual layout design (full custom IC): required In case of machine generated layout: recommended ► Some typical operations of DRC: WIDTH(A) < 0.5 Results in all shapes of layer A which are thinner than 0.5 SPACING(A,B) < 0.5 Results in all shape pairs of layers A and B the distance between which is smaller than 0.5 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 57 Budapest University of Technology and Economics Department of Electron Devices Layout macros – resolved: The layout description is also a hierachical one, but this has nothing to do with the design hierarchy, but the hierarchy of the layout macros Level 1: two macro references (core, pad ring) 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 58 Budapest University of Technology and Economics Department of Electron Devices Layout macros – resolved: Level 2: pad ring sub-divided 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 59 Budapest University of Technology and Economics Department of Electron Devices Layout macros – resolved: Level 3: pad ring further resolved, routing channels, cell rows 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 60 Budapest University of Technology and Economics Department of Electron Devices Layout macros – resolved: Level 4: macro references of pad cells and standard cells 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 61 Budapest University of Technology and Economics Department of Electron Devices Layout macros – resolved: Level 5 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 62 Budapest University of Technology and Economics Department of Electron Devices Layout macros – resolved: Level 6 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 63 Budapest University of Technology and Economics Department of Electron Devices Layout macros – resolved: Level 7: all macros along the hierarchy are completely resolved 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 64 Budapest University of Technology and Economics Department of Electron Devices Layout macros – resolved: Level 4: transistors and contacts/vias still with macro references 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 65 Budapest University of Technology and Economics Department of Electron Devices Layout macros – resolved: Level 6: standard cells, contacts/vias fully resolved 1-12-2009 IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 66 Budapest University of Technology and Economics Department of Electron Devices Flow of automated design: Simulator: Representation: System simulation System level description Specs in SystemC for HWSW co-design Functional testing Behavioral description Specs in VHDL or in Verilog Abstraction level: System level design Design work is concentrated here High level sythesis Logic simulation timing parameters Structural description either in VHDL or Verilog Logic level design Mapping and layout generation Transistor level design Extraction of delays 1-12-2009 Physical design (layout) IC design 2: Design rules, design frameworks © Poppe András, BME-EET 2009 67