Process

advertisement

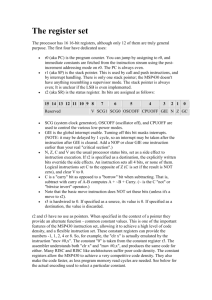

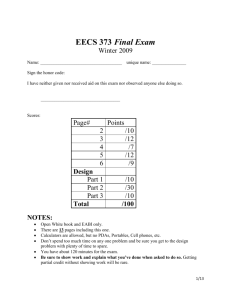

ECNG3006 MICROPROCESSOR APPLICATIONS Course Instructor: Mr. Kevon Andrews Office: Rm. 239 Phone: 1-868-662-2002 ext.3156 Email address: keandrews@eng.uwi.tt Office Hours: Mon: 2-3pm, Tue: 2-3pm, Fri:10- 12pm COURSE OUTLINE • • • • • • • • • Differences between PIC18F452 and PIC16F877 Processes RTOS design FreeRTOS Overview FreeRTOS ISR Example RTOS application & design issues Real-time system Scheduling Theory Scheduling Approaches and Performance Issues Unit Objectives Recall differences between PIC18F452 and PIC16F877. Apply knowledge of states of processes in applications examples. Design real-time system application using the FreeRTOS implementation. Outline the design of an RTOS. Analyse design issues of real-time systems using FreeRTOS.. Unit Objectives (cont’d) Reconstruct real-time systems using knowledge of design issues. Define and classify different classifications of realtime systems according to their timing attributes. Give examples of real-time systems as related to classification of real-time systems. Explain concepts within scheduling theory. Describe scheduling algorithms. Analyse some issues and performance of schedules. ASSESSMENT • • End of semester examination [50%] 50% Coursework [50%] – Laboratory exercises [30% ] • Laboratory exercise 1 – Introduction to MPLAB and C18 • • compiler [10%] Laboratory exercise 2 – C18 compiler and LCD [10%] Laboratory exercise 3 – FreeRTOS and LCD [10%] – Mini-project [20% ] Differences between PIC18F452 and PIC16F877 • Show general differences. • Architectural differences. • Changes in registers used for direct addressing and indirect addressing. • Interrupt priority levels. General Differences 16F877 • 8192 prg instructions • 368 bytes RAM • 3 timers • 5 A/D channels • 14 interrupt sources • 35 instructions • private stack • 1-level interrupt priority 18F452 • 16384 prg instructions • 1536 bytes RAM • 4 timers • 8 A/D channels • 18 interrupt sources • 75 instructions • user addressable stack • 2-level interrupt Program Memory Map and Stack 16F877 18F542 Architectural Differences • The PC contains 21 bits, which means that it is capable of addressing 2MB memory. • Only 32K of memory is actually on-chip, so a read outside of the physical memory will return 0's (NOP). • There is now a separate Bank Select Register (BSR) instead of two bits in the Status register, but only the lower 4 bits are used. Direct Addressing • The BSR is used to switch the banks and can be loaded directly via the MOVLB instruction. • We need 12 bits to address all the possible data memory locations, i.e. there are 4096 possible memory locations. Direct Addressing Indirect Addressing • The indirect addressing mode using the FSR and INDF registers of the 16Fxxx has been retained except that there are now three sets, – INDF0, INDF1, INDF2 – FSR0 (FSR0H, FSR0L) – FSR1 (FSR1H, FSR1L) – FSR2 (FSR2H, FSR2L) • Why are there H and L versions of the FSR? Indirect Addressing Indirect Addressing • There is a special instruction LFSR to load the FSR registers. • As usual access to the INDFn registers actually references the memory location referred to by the FSRn register. • In addition to the INDFn registers, there are an additional four registers associated with each of INDF0..INDF2. Indirect Addressing • All the indirect registers are – INDFn – no change after indirect access – POSTDECn – auto-decrement after indirect access – POSTINCn – auto-increment after indirect access – PREINCn – auto-increment before indirect access – PLUSWn – use value in W as offset to FSR, don't change either W or FSR Interrupt Priority • Each interrupt source, except INT0, has three bits to control its operation. The functions of these bits are: – Flag bit to indicate that an interrupt event has occurred – Enable bit that allows program execution to branch to the interrupt vector address when the flag bit is set – Priority bit to select high priority or low priority Interrupt Priority • The interrupt priority feature is enabled by setting the IPEN bit (RCON<7>). • When interrupt priority is enabled, there are two bits which enable interrupts globally. – Setting the GIEH bit (INTCON<7>) enables all interrupts that have the priority bit set. – Setting the GIEL bit (INTCON<6>) enables all interrupts that have the priority bit cleared. Interrupt Priority • When the interrupt flag, enable bit and appropriate global interrupt enable bit are set, the interrupt will vector immediately to address 000008h or 000018h, depending on the priority level. • Individual interrupts can be disabled through their corresponding enable bits. C differences Pentium • char – 8 bits • int – 32 bits • short – 16 bits • long – 32 bits • float – 32 bits • double – 64 bits 18 series • char – 8 bits • int – 16 bits • short – 16 bits • long – 32 bits • float - 32 bits • double – 64 bits Summary • Differences between PIC18F452 and 18F877. • Differences in PC(21 bits vs. 13bits) and selection of banks(BSR<3:0> vs 2 bits in Status Register). • Registers used in direct(BSR<3:0> & 8-bit opcode) and indirect addressing(FSRn & INDFn / POSTDECn / POSTINCn / PREINCn / PLUSWn. • Introduction of different priority levels. Processes • Define a process • Describe the states of a process • Define a context and context switch Process • Suppose instead of doing only one thing we have the computer do several jobs at the same time. These jobs are kept in memory and the CPU time is shared between them. • Each job is called a process. • Each process behaves as if the CPU belonged to it alone. Processes States of Process Processes • When a process moves from the running to either the waiting or ready state, it does not have access to the CPU as it has given it to another process. • If it is to gain access to the CPU again, we must store all what it was doing so that we can restore it as if it never stopped! • That information that we must store is called the context of the process. Context • A context is literally everything about the process, some things are – Program Counter – State of the stack – CPU registers – I/O state – Process state – ... etc Context Switch • When the CPU switches to another process, the old context must be saved and the new context loaded for the new process. • This save/load is called a context switch. SUMMARY • Process is a job, which the CPU seems to execute at the same time. • 5 states which can describe the status of a process: new; ready; waiting; running and terminated. • Context includes everything about a process. • Context switch is the saving of the old context and loading of the new context.