IE120 - SharePoint - Erie Community College

ERIE COMMUNITY COLLEGE – NORTH

ELECTRICAL ENGINEERING TECHNOLOGY

COURSE OUTLINE

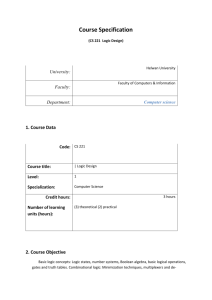

COURSE NUMBER & TITLE:

IE120 Digital Electronics

CURRICULUM:

Industrial Technology

CATALOG DESCRIPTION: IE120 (2-2-3)

Logic concepts using switches; binary and hex numbers; logic gates, drivers and interfaces; encoders and decoders; flip-flops, registers and counters; a simple adder; RAM and ROM memory and mass storage. Experiments include: simple logic circuits using switches and LEDs; integrated-circuit logic gates, encoders and decoders; registers and counters and a simple adder.

Concurrent Registration: Concurrent registration in IE 130.

(N)

DURATION OF INSTRUCTIONAL PERIOD:

Two 50 minute lectures per week for fifteen (15) weeks. One (1) lab class of 100 minutes per week.

ACADEMIC CREDIT HOURS:

CONTACT HOURS:

LECTURE, LAB, CREDIT HOURS:

Three (3.0) Credit Hours

Four

(2-2-3)

SUGGESTED TEXT/ COURSE MATERIAL:

Digital Electronics by Tokheim

COURSE OUTCOMES:

At the completion of the course the student shall be able to:

1. Perform calculations and base conversions in the binary, decimal and hexadecimal number systems.

2. Relate logic diagrams to Boolean expressions, truth tables and state tables.

3. Breadboard and troubleshoot digital logic circuits.

4. Analyze combinational and sequential logic circuits.

5. Relate IEEE and MIL-STD logic symbols to their logic function.

6. Identify and explain the behavior of combinational circuits including encoders, decoders, tri-state buffers, arithmetic circuits, multiplexers and demultiplexers.

7. Identify and explain the behavior of sequential circuits including latches, flipflops, registers, and counters

8. Prepare a laboratory report based on data collected from tests on digital systems.

PROGRAM COMPETENCIES: N/A

SUNY GENERAL EDUCATION TEN KNOWLEDGE AREAS: N/A

ECC GRADUATE LEARNING OUTCOMES:

1. Communicate effectively.

2. Read and think critically.

Course Objectives

6-8

1-8

3. Apply appropriate mathematical procedures and quantitative

methods.

8. Exhibit the research skills for lifelong learning.

10. Demonstrate competence with computers and technology

ASSESSMENT OF STUDENT LEARNING:

1. Two one hour tests )

2. Two or three short quizzes )

3. A two hour comprehensive final ) 60%

4. minimum of 10 laboratory reports 40%

100%

RELATED LIBRARY PROJECTS:

Research – Component specifications using the Internet or the library

LECTURE TOPICAL OUTLINE:

I. Introduction

1. Binary numbers

2. AND, OR, EOR using switches and lamps

II.

LOGIC GATES AND BOOLEAN ALGEBRA

1.

AND, OR, NOT operation

2.

Truth table and logic circuit

3.

Boolean theorems and DeMorgan’s Theorem

4.

NAND, NOR gates and operations

III.

Combinational logic circuits

1. Designing logic circuits

2. Use of the Karnaugh map

3. Exclusive OR and NOR circuits

HOURLY I

IV. Flip-flops

1. NAN/NOR gate SC latch

2. Clocked SC flip-flop

3. JK and D flip-flops

V. Registers and counter

1. Register operation

2. Series or parallel transfer

3. Asynchronous counters

4. Synchronous counters

5. Johnson and ring counters

6. Glitches, propagation delay, BCD counters

1-8

8

3,8

WEEKS

2/2

3/2

4/2

1/3

2/2

4/2

QUIZ I (20 minutes)

VI.

Logic circuits

1. Decoders

2. Encoders

3. Multiplexers

4. Demultiplexers

5. Data Busing

3/2

HOURLY II

VII.

Digital arithmetic

1. Binary addition

2. Signed numbers

3. 1’s and 2’s complements

4. Addition, subtraction, of binary numbers

5. Half adder and full adder circuits

IX.

QUIZ 2 (20 minutes)

VIII. Memory Devices

1. Read-only memories ROM

2. Random access memories RAM

3. Semiconductor RAM

4. Static/dynamic RAM

Interfacing with the analog world

1. D/A conversion

2. D/A circuits

3. Ramp and successive approximation A/D

LABS

COMPREHENSIVE FINAL

I. INTRODUCTION

1. Orientation, syllabus

2. Logic trainer familiarities

3. 7404 IC mounting, testing

II.

III.

IV.

Basic Logic Gate Functions

Verification of Demorgan's Theorem

A. Combinational Logic Circuit 1

B. Combinational Logic Circuit 2

V. 7400 Family Electrical Characteristics

(in-class lecture)

VI. Latches & Flip-Flops

VII. Registers

VIII. Counters

IX. Encoders, Decoders and MUX

X. Serial Adder

XI. RAM

1/2

4/2

2/2

3/2

1

1

1

2

1

1

1-1/2

1-1/2

1

1

1

XII. (Optional Labs)

PREPARED BY:

Al Ashman, May, 2000

APPROVED BY:

EET Curriculum Committee, June, 2009

1