JK Flip-Flop Lab: Debouncer & Operation Analysis

advertisement

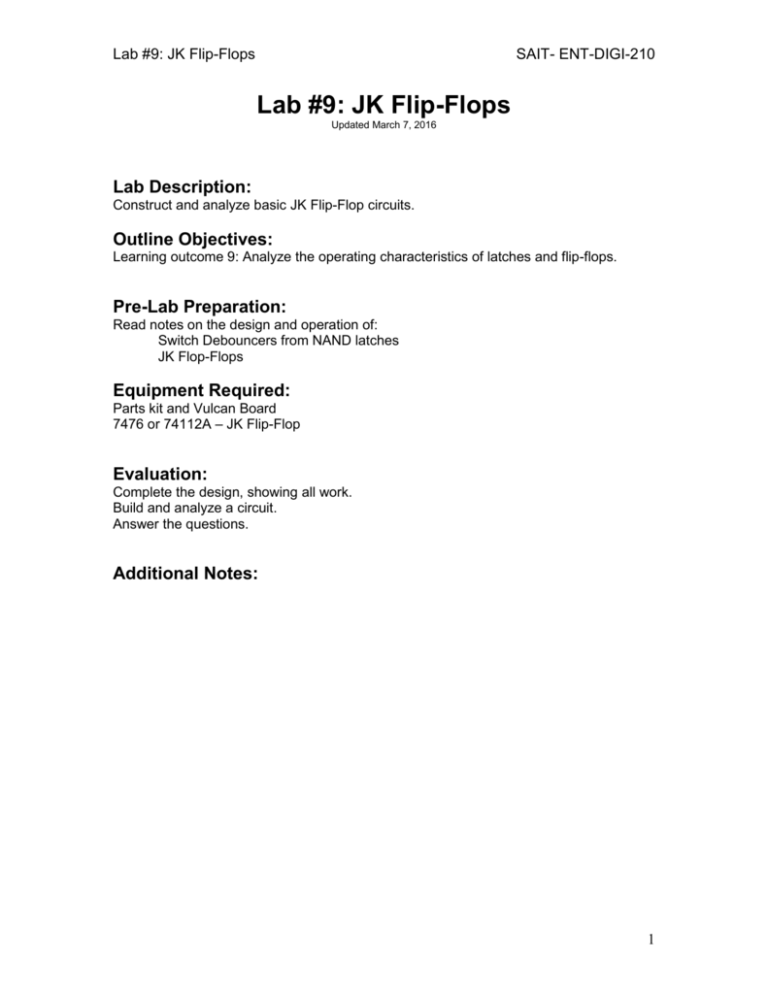

Lab #9: JK Flip-Flops SAIT- ENT-DIGI-210 Lab #9: JK Flip-Flops Updated March 7, 2016 Lab Description: Construct and analyze basic JK Flip-Flop circuits. Outline Objectives: Learning outcome 9: Analyze the operating characteristics of latches and flip-flops. Pre-Lab Preparation: Read notes on the design and operation of: Switch Debouncers from NAND latches JK Flop-Flops Equipment Required: Parts kit and Vulcan Board 7476 or 74112A – JK Flip-Flop Evaluation: Complete the design, showing all work. Build and analyze a circuit. Answer the questions. Additional Notes: 1 Lab #9: JK Flip-Flops SAIT- ENT-DIGI-210 Procedure 1: Create a Debounce switch using NAND gates 1. Use circuit simulation software to design a basic debounce circuit from NAND gates. Hint: you must use the SPDT (Single Pole Double Throw) switch. 2. Wire the circuit on your breadboard. Use the LEDs on the Vulcan board to demonstrate the Q and the Q’ outputs. 3. Verify its operation by first setting the latch and removing the switch from the circuit (the output should remain unchanged), then replace the switch, reset the latch and remove the switch again (the output should remain unchanged). 4. Demonstrate its operation to the instructor and answer the question in procedure 4. Signature Procedure 1: ___________ Procedure 2: Verify the operation of a JK Flip-Flop 1. Use circuit simulation software to demonstrate the function of a JK FlipFlop, including its asynchronous inputs. 2. Wire the circuit on your breadboard. Use the LEDs on the Vulcan board to demonstrate the five inputs and the two outputs. Use the debounced switch for the clock input. 3. Verify its operation by completing the function table below. Select appropriate inputs and outputs to demonstrate its full range of function (you may add or remove rows from the table as appropriate). 4. Demonstrate its operation to the instructor and answer the question in procedure 4. 2 Lab #9: JK Flip-Flops CLK SAIT- ENT-DIGI-210 Inputs J K PRE CLR Outputs Q Q’ Mode TABLE: JK Flip-Flop Signature Procedure 2: ___________ Procedure 3: Observe the effects of switch (contact) bounce 1. Using the JK flip-flop from procedure 2, set-up the JK Flip Flop in toggle mode. 2. Connect the clock input directly to the SPDT DIP switch (without the debouncer circuit). Observe its operation. 3. Answer the question in part 4. Procedure 4: Answer the following questions: 1. Explain why the debouncer circuit is able to retain the last latched state with the switch removed. Be specific. 3 Lab #9: JK Flip-Flops SAIT- ENT-DIGI-210 2. If the J, K and CLK inputs of the JK Flip-Flop are set to low and only the Clear and Preset inputs are used, what does the operation of this device resemble? Draw a table to help explain your answer. 3. What did you observe in procedure 3? Explain what happened and why. 4. Do all digital inputs require a debouncer? Explain. Signature Procedure 4: ___________ Student Name: ____________________________ Date: _______________ 4