CHP6-MICROWAVE AMPLIFIERS1_withExamples_part1

advertisement

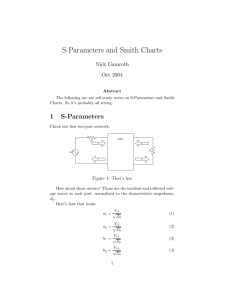

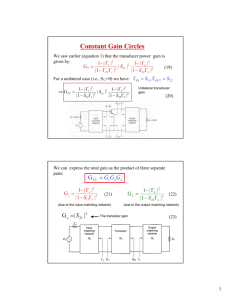

EKT 441 MICROWAVE COMMUNICATIONS CHAPTER 6: MICROWAVE AMPLIFIERS 1 INTRODUCTION Most RF and microwave amplifiers today used transistor devices such as Si or SiGe BJTs, GaAs HBTs, GaAs or InP FETs, or GaAs HEMTs. Microwave transistor amplifiers are rugged, low cost, reliable and can be easily integrated in both hybrid an monolithic integrated circuitry. 2 General Amplifier Block Diagram DC supply vs(t) vi(t) ii(t) Zs Input Matching Network Amplifier vo(t) Output Matching Network Pin Vcc Vs io(t) PL ZL The active component Input and output voltage relation of the amplifier can be modeled simply as: vo t a1vi t a2vi 2 t a3vi 3 t H .O.T . 3 Amplifier Classification Amplifier can be categorized in 2 manners. According to signal level: Small-signal Amplifier. Our approach in this chapter Power/Large-signal Amplifier. According to D.C. biasing scheme of the active component: Class A. Class B. Class AB. Class C. There are also other classes, such as Class D (D stands for digital), Class E and Class F. These all uses the transistor/FET as a switch. 4 Small-Signal Versus Large-Signal Operation Usually non-sinusoidal waveform Large-signal: vo t a1vi t a2vi 2 t a3vi 2 t H .O.T . Nonlinear Small-signal: vo t a1vi t Linear Sinusoidal waveform Zs vi(t) Vs ZL vo(t) 5 Small-Signal Amplifier (SSA) All amplifiers are inherently nonlinear. However when the input signal is small, the input and output relationship of the amplifier is approximately linear. vo t a1vi t a2vi 2 t a3vi 3 t H .O.T . a1vi t When vi(t)0 (< 2.6mV) vo t a1vi t Linear relation (1.1) This linear relationship applies also to current and power. An amplifier that fulfills these conditions: (1) small-signal operation (2) linear, is called Small-Signal Amplifier (SSA). SSA will be our focus. If a SSA amplifier contains BJT and FET, these components can be replaced by their respective small-signal model, for instance the hybrid-Pi model for BJT. 6 Example 1.1 - An RF Amplifier Schematic (1) DC supply Zs Input Matching Network Amplifier Output Matching Network Vs ZL RF power flow 7 Typical RF Amplifier Characteristics To determine the performance of an amplifier, the following characteristics are typically observed. 1. Power Gain. 2. Bandwidth (operating frequency range). Important to small-signal 3. Noise Figure. amplifier 4. Phase response. 5. Gain compression. 6. Dynamic range. Important parameters of large-signal amplifier 7. Harmonic distortion. (Related to Linearity) 8. Intermodulation distortion. 9. Third order intercept point (TOI). 8 Power Gain For amplifiers functioning at RF and microwave frequencies, usually of interest is the input and output power relation. The ratio of output power over input power is called the Power Gain (G), usually expressed in dB. Power Gain Output Power G 10 log 10 dB Input Power (1.2) There are a number of definition for power gain as we will see shortly. Furthermore G is a function of frequency and the input signal level. 9 Why Power Gain for RF and Microwave Circuits? (1) Power gain is preferred for high frequency amplifiers as the impedance encountered is usually low (due to presence of parasitic capacitance). Power = Voltage x Current For instance if the amplifier is required to drive 50Ω load the voltage across the load may be small, although the corresponding current may be large (there is current gain). For amplifiers functioning at lower frequency (such as IF frequency), it is the voltage gain that is of interest, since impedance encountered is usually higher (less parasitic). For instance if the output of IF amplifier drives the demodulator circuits, which are usually digital systems, the impedance looking into the digital system is high and large voltage can developed across it. Thus working with voltage gain is more convenient. 10 Why Power Gain for RF and Microwave Circuits? (2) Instead on focusing on voltage or current gain, RF engineers focus on power gain. By working with power gain, the RF designer is free from the constraint of system impedance. For instance in the simple receiver block diagram below, each block contribute some power gain. A large voltage signal can be obtained from the output of the final block by attaching a high impedance load to it’s output. RF signal power 1 W 15 W 75 W BPF v(t) IF signal power 4.90 V 7.5 mW BPF LNA t IF Amp. 400Ω RF Portion (900 MHz) LO IF Portion (45 MHz) 2 V Paverage 2R 11 Harmonic Distortion (1) When the input driving signal is small, the amplifier is linear. Harmonic components are almost non-existent. Zs Vs ZL Pout Small-signal operation region Pin 12 Harmonic Distortion (2) When the input driving signal is too large, the amplifier becomes nonlinear. Harmonics are introduced at the output. Zs Vs ZL f1 0 f1 2f1 f 3f1 4f1 f Harmonics generation reduces the gain of the amplifier, as some of the output power at the fundamental frequency is shifted to higher harmonics. This result in gain compression seen earlier! Pout harmonics Pin 13 Power Gain, Dynamic Range and Gain Compression Pout (dBm) Input and output at same frequency Pin Pout Ideal amplifier Gain compression occurs here 30 Device Burn out 1dB 20 10 Saturation Linear Region 0 -10 -20 Nonlinear Region Dynamic range (DR) -30 Power gain Gp = Pout(dBm) - Pin(dBm) = -30-(-43) = 13dB -40 1dB compression Point (Pin_1dB) -50 Noise Floor -60 -70 -60 -50 -40 -30 -20 -10 0 10 Pin 20 (dBm) 14 Bandwidth Power gain G versus frequency for small-signal amplifier. Po dBm Pi dBm G/dB Po dBm 3 dB Pi dBm Bandwidth 0 f / Hz 15 Noise Figure (F) • The amplifier also introduces noise into the output in addition to the noise from the environment. • Assuming small-signal operation. Smaller SNRin Zs Vs SNR: Signal to Noise Ratio Noise Figure (F)= SNRin/SNRout • Since SNRin is always larger than SNRout, F > 1 for an amplifier which contribute noise. ZL Larger SNRout 16 Power Gain Definition From the power components, 3 types of power gain can be defined. Power Gain G p Power delivered to load PL Input power to Amp. Pin Available Power Gain G A Available load Power PAo Available Input power PAs PL Power delivered to load Transducer Gain GT Available Input power PAs (2.1a) (2.1b) (2.1c) The effective power gain GP, GA and GT can be expressed as the S-parameters of the amplifier and the reflection coefficients of the source and load networks. Refer to Appendix 1 for the derivation. 17 Naming Convention Zs Amplifier Vs ZL s 2 - port Network Source Network s11 s 21 in In the spirit of highfrequency circuit design, where frequency response of amplifier is characterized by S-parameters and reflection coefficient is used extensively instead of impedance, power gain can be expressed in terms of these parameters. L Load Network s12 s22 out 18 TWO-PORT POWER GAIN Figure 7.1: A two port network with general source and load impedance. 19 TWO-PORT POWER GAIN Power Gain = G = PL / Pin is the ratio of power dissipated in the load ZL to the power delivered to the input of the two-port network. This gain is independent of Zs although some active circuits are strongly dependent on ZS. Available Gain = GA = Pavn / Pavs is the ratio of the power available from the two-port network to the power available from the source. This assumes conjugate matching in both the source and the load, and depends on ZS but not ZL. Transducer Power Gain = GT = PL / Pavs is the ratio of the power delivered to the load to the power available from the source. This depends on both ZS and ZL. If the input and output are both conjugately matched to the two-port, then the gain is maximized and G = GA = GT 20 TWO-PORT POWER GAIN From the definition of S parameters: V1 S11V1 S12V2 S11V1 S12LV2 [7.1a] V2 S 21V1 S 22V2 S 21V1 S 22LV2 [7.1b] Eliminating V2- from [7.1a]: Z Z0 V1 S S in S11 12 21 L in V1 1 S 22L Z in Z 0 out S S Z Z0 V2 S 22 12 21 S out V2 1 S11S Z out Z 0 [7.2] [7.3] 21 TWO-PORT POWER GAIN By voltage division: Z in V1 VS V1 V1 V1 1 in Z S Z in Using: Solving for V1+: 1 in Z in Z 0 1 in VS 1 S V 2 1 S in 1 [7.4] [7.5] [7.6] 22 TWO-PORT POWER GAIN The average power delivered to the network: 1 Pin V 2Z 0 2 1 1 8Z VS 2 1 S 2 in 0 2 1 S in 1 2 2 in [7.7] The power delivered to the load is: PL PL 2 1 V 2Z 0 VS 2 2 2 V 2Z 0 1 1 S 21 2 L 2 2 1 S 22L S 21 2 [7.8] L 2 1 1 2 L 2 [7.9] 2 S 8Z 0 1 S 22L 1 S in 2 23 TWO-PORT POWER GAIN The power gain can be expressed as: 2 GP G 1 1 S 2 S 21 PL Pin 1 in 2 L [7.10] 2 22 L The available power from the source: Pavs Pin in S 1 S 2 8Z 0 1 S 2 Vs 2 The available power from the network: Pavn PL L out Vs 2 S 21 1 out 1 S 2 2 2 8Z 0 1 S 1 22 out S in [7.11] 2 [7.12] 2 L out 24 TWO-PORT POWER GAIN The power available from the network: Pavn Vs S 21 1 S 2 2 2 8Z 0 1 S11S 1 out 2 The available power gain: S 21 1 S 2 2 The transducer power gain: [7.13] P GA avn Pavs 1 out 2 1 S11S 2 [7.14] 2 S 21 1 S 1 L PL GT 2 2 Pavs 1 S 22L 1 S in 2 2 2 [7.15] 25 Summary of Important Power Gain Expressions and the Gain Dependency Diagram Z Z0 V1 S S in S11 12 21 L in V1 1 S 22L Z in Z 0 out 2 2 (2.2a) 2 GA 2 GP 2 2 2 (2.2d) 21 2 out 1 s 1 (2.2e) 2 GT G 1 s22L 1 in s 2 2 11 s S S Z Z0 V S 22 12 21 S out V 1 S11S Z out Z 0 (2.2b) s21 1 L 1 s 1 s 1 L 2 21 2 2 s 1 s22L 1 ins 2 (2.2c) T GA s L in out s11 s 21 s12 s22 Note: All GT, GP, GA, 1 and 2 depends on the Sparameters. The Gain Dependency Diagram GP 26 TWO-PORT POWER GAIN A special case of the transducer power gain occurs when both input and output are matched for zero reflection (in contrast to conjugate matching). GT S 21 2 [7.16] Another special case is the unilateral transducer power gain, GTU where S12=0 (or is negligibly small). This nonreciprocal characteristic is common to many practical amplifier circuits. Γin = S11 when S12 = 0, so the unilateral transducer gain is: GTU S 21 1 S 2 2 1 2 L 1 S11S 1 S 22L 2 [7.17] 2 27 TWO-PORT POWER GAIN Figure 7.2: The general transistor amplifier circuit. 28 TWO-PORT POWER GAIN The separate effective gain factors: GS 1 S 1 inS G0 S 21 GL 2 2 [7.18a] 2 1 L [7.18b] 2 1 S 22L 2 [7.18c] 29 TWO-PORT POWER GAIN If the transistor is unilateral, the unilateral transducer gain reduces to GTU = GSG0GL , where: GS 1 S 1 S11S G0 S 21 GL 2 2 [7.19a] 2 1 L [7.19b] 2 1 S 22L 2 [7.19c] 30 Example 1 – Familiarization with the Gain Expressions An RF amplifier has the following S-parameters at fo: s11=0.3<-70o, s21=3.5<85o, s12=0.2<-10o, s22=0.4<-45o. The system is shown below. Assuming reference impedance (used for measuring the Sparameters) Zo=50, find: (a) GT, GA, GP. (b) PL, PA, Pinc. 40 Amplifier 5<0o s11 s12 s 21 s22 ZL=73 31 Example 1 Cont... Z s Zo Z s Zo Z Z L Z L Zo 0.187 L o 0.111 s Step 1 - Find s and L . s11 L s s s11 12 21 L 0.146 j 0.151 Step 2 - Find 1 and 2 . in 1 s22L 1 s22L Step 3 - Find GT, GA, GP. s s s s out 22 s22 21 12 s 0.265 j 0.358 Step 4 - Find PL, PA. 1 s11s 1 s11s 2 G GP PA Try to derive These 2 relations 2 Vs 0.078W 8ReZ s Pin PA 1 Z1 Z s Zo Z1 Z s 2 0.0714W PL GP Pin 0.9814W 2 1 s22L 1 in 2 2 13.742 1 s G 14.739 1 s 1 1 s 1 12.562 G 2 s 2 A 2 21 2 11 s out 2 L T Again note that this is an analysis problem. s21 1 L 2 21 2 2 s 1 s22L 1 ins 2 32 STABILITY In the circuit of Figure 7.2, oscillation is possible if either the input or output port impedance has the negative real part; this would imply that |Γin|>1 or |Γout|>1. Γin and Γout depends on the source and load matching networks, the stability of the amplifier depends on ΓS and ΓL as presented by matching networks. Unconditionally stable: The network is unconditionally stable if |Γin| < 1 and |Γout| < 1 for all passive source and load impedance (ex; |ΓS| < 1 and |Γ| < 1). Conditionally stable: The network is conditionally stable if |Γin| < 1 and |Γout| < 1 only for a certain range of passive source and load impedance. This case also referred as potentially unstable. The stability condition of an amplifier circuit is usually frequency dependent. 33 STABILITY CIRCLES The condition that must be satisfied by ΓS and ΓL if the amplifier is to be unconditionally stable: S12 S 21L in S11 1 1 S 22L [7.20a] S S S 1 1 S [7.20b] 12 out 21 S 22 11 S The determinant of the scattering matrix: S11S22 S12S21 [7.21] 34 STABILITY CIRCLES The output stability circles: CL S CS S S 22 RL The input stability circles: 22 11 2 2 S12 S 21 S 22 2 S RS 11 S 22 2 S12 S 21 S11 2 [7.22b] 2 S11 2 2 [7.22a] [7.23a] [7.23b] 35 STABILITY CIRCLES Figure 7.3: Output stability circles for conditionally stable device. (a) |S11| < 1 (b) |S11| > 1 36 STABILITY CIRCLES If the device is unconditionally stable, the stability circles must be completely outside (or totally enclose) the Smith chart. CL RL 1 S11 1 [7.24a] CS RS 1 S 22 1 [7.24b] 37 STABILITY TEST Rollet’s condition: 1 S11 S 22 2 K the auxiliary condition: the μ test: 2 2 1 [7.25] S11S22 S12S21 1 [7.26] 2 S12 S 21 1 S11 2 S 22 S11 S12 S 21 1 [7.27] 38 Example 2 The S parameters for the HP HFET-102 GaAs FET at 2 GHz with a bias voltage of Vgs = 0 are given as follow (Z0 = 50 Ohm): S11 = 0.894 < -60.6 S21 = 3.122 < 123.6 S12 = 0.020 < 62.4 S22 = 0.781 < -27.6 Determine the stability of this transistor using the K- test and the μ test, and plot the stability circles on the Smith Chart 39 Example 2 Remember, criteria for unconditional stability is: For the K- test: S S S S 1 11 22 12 1 S11 S 22 2 K 21 2 2 S12 S 21 2 1 For the μ test: 1 S11 11 2 S 22 S S12 S 21 1 40 Example 2 Calculation results: For the K- test: S S S S 0.696 1 11 K 22 12 1 S 11 2 21 S 22 2S S 12 For the μ test: 2 1 S 0.607 1 21 2 0.86 1 11 S S S S 22 2 11 12 21 Which indicates potential instability 41 Example 2 Calculation for the input and output stability circles: Output stability circle center and radius: C L S S 1.361 47 S 22 11 2 2 22 S S R 0.50 S 12 21 2 L 2 22 Input stability circle and radius C S S S 1.132 68 S 11 22 2 2 11 S S R 0.199 S 12 2 S 11 21 2 42 STABILITY Figure 7.4: Example of stability circles 43 SINGLE STAGE TRANSISTOR AMPLIFIER DESIGN Maximum power transfer from the input matching network to the transistor and the maximum power transfer from the transistor to the output matching network will occur when: S in [7.28a] L out [7.28b] Then, assuming lossless matching sections, these conditions will maximize the overall transducer gain: GTmax 1 1 S 2 S 21 2 1 L 2 1 S 22L [7.29] 2 44 SINGLE STAGE TRANSISTOR AMPLIFIER DESIGN In the general case with a bilateral transistor, Γin is affected by Γout, and vice versa, so that the input and output sections must be matched simultaneously. S12 S 21L S11 1 S 22L S S12 S 21S S 22 1 S11S L [7.30a] [7.30b] 45 SINGLE STAGE TRANSISTOR AMPLIFIER DESIGN The solution is: B B 4C 2 2 1 S 1 1 [7.31a] 2C 1 B B 4C 2 2 L 2 2 2C 2 [7.31b] 2 46 SINGLE STAGE TRANSISTOR AMPLIFIER DESIGN The variables are defined as: B1 1 S11 S 22 2 B2 1 S 22 S11 2 2 2 2 C1 S11 S 2 22 11 C2 S 22 S [7.32a] [7.32b] [7.32c] [7.32d] 47 SINGLE STAGE TRANSISTOR AMPLIFIER DESIGN When S12 = 0, it shows that ΓS = S11* and ΓL = S22*, and the maximum transducer gain for unilateral case: GTU max 1 1 S11 2 S 21 [7.33] 1 2 1 S 22 2 When the transistor is unconditionally stable, K > 1, and the max transducer power gain can be simply re-written as: GTmax S 21 S12 K The maximum stable gain with K = 1: Gmsg K 2 1 [7.34] [7.35] S 21 S12 48 Example 3 Design an amplifier for a maximum gain at 4.0 GHz. Calculate the overall transducer gain, GT, and the maximum overall transducer gain GTmax. The S parameters for the GaAs FET at 4 GHz given as follow (Z0 = 50 Ohm): S11 = 0.72 < -116o S21 = 2.60 < 76o S12 = 0.03 < 57o S22 = 0.73 < -68o 49 Example 3 (Cont) Determine the stability of this transistor using the K- test S S S S 0.488 162 11 K 22 1 S 11 12 2 S 21 2 22 2S S 12 2 1.195 21 Since || < 1 and K > 1, the transistor is unconditionally stable at 4.0 GHz. 50 Example 3 (cont) For the maximum gain, we should design the matching sections for a conjugate match to the transistor. Thus, ΓS = Γin* and ΓL = Γout*, ΓS and ΓL can be determined from; B B 4C 2 2 1 S 2 0.872 123 1 2C 1 B B 4C 2 2 L 2 1 2C 2 0.876 61 2 51 Example 3 The effective gain factors can calculated as: 1 G 1 S G S 0 G L 2 21 4.17 6.20dB 2 S 11 6.76 8.30dB 1 2 L 1 S 22 2 1.67 2.22dB L So the overall maximum transducer gain will be; GTmax 6.20 8.30 2.22 16.72dB 52 UNILATERAL FOM • In many practical cases |S12| is small enough to be ignored, the device then can be assumed to be unilateral, which greatly simplifies design procedure • Error in the transducer gain caused by approximating |S12| as zero is given by the ratio GT/GTU, and be bounded by: 1 G 1 (1 U ) G (1 U ) T 2 2 TU Where U is defined as the unilateral figure of merit U S S S S 12 21 11 22 (1 S )(1 S ) 2 11 2 22 53 Example 4 An FET is biased for minimum noise figure, and has the following S parameters at 4 GHz: S11 = 0.60 < -60o S21 = 1.90 < 81o S12 = 0.05 < 26o S22 = 0.50 < -60o For design purposes, assume the device is unilateral and calculate the max error in GT resulting from this assumption. 54 Example 4 (cont) To compute the unilateral figure of merit; U S S S S 12 21 11 22 (1 S )(1 S ) 2 2 11 0.059 22 Then the ratio of GT/GTU is bounded as; 1 G 1 (1 U ) G (1 U ) T 2 2 TU G 0.891 1.130 G T TU 55 Example 4 (cont) In dB, this is; 0.50 G G 0.53dB T TU Where GT and GTU are now in dB. Thus we should expect less than about ± 0.5 dB error in gain. 56 CONSTANT GAIN CIRCLES • In many cases it is desirable to design for less than the max obtainable gain, to improve bandwidth or to obtain a specific value for an amplifier gain. • Mismatches are purposely introduced to reduce the overall gain • Procedure is facilitated by plotting constant gain circles on the Smith Chart • Represents loci of ΓS and ΓL, that give fixed values of GS and GL. • To simplify the discussion, we will only treat the case of a unilateral device 57 CONSTANT GAIN CIRCLES The expression for the GS and GL for the unilateral case is given by: G S 1 2 G S 1 S 11 2 L S 1 2 L 1 S 22 2 L These gains are maximized when ΓS = S11* and ΓL = S22* : G max S 1 1 S 2 11 G max L 1 1 S 2 22 58 CONSTANT GAIN CIRCLES Now we define normalized gain factors gS and gL as; 1 G g (1 S ) G max 1 S 2 2 S S 2 S S 11 11 S 1 G g (1 S ) G max 1 S 2 2 L L 2 L L 22 22 L Thus we have that: 0 ≤ gS ≤ 1, and 0 ≤ gL ≤ 1. A fixed value of gS and gL represents circles in the ΓS and ΓL planes. 59 CONSTANT GAIN CIRCLES Input constant gain circles: CS RS g S S11 1 1 g S S11 [7.37a] 2 1 g S 1 S11 2 1 1 g S S11 2 [7.37b] Output constant gain circles: CL RL g L S 22 1 1 g L S 22 [7.38a] 2 1 g L 1 S 22 1 1 g L S 22 2 [7.38b] 2 60 Example 5 Design an amplifier to have a gain of 11 dB at 4 GHz. Plot constant gain circles for GS = 2 dB and 3 dB; and GL = 0 dB and 1 dB. The FET has the following S parameters (Z0 = 50 Ω): S11 = 0.75 < -120o S21 = 2.50 < 80o S12 = 0.00 < 0o S22 = 0.60 < -85o 61 Example 5 (cont) Since S12 = 0 and |S11| < 1 and |S22| < 1, the transistor is unilateral and unconditionally stable. We calculate the max matching section gains as; G max S 1 1 S 2 2.29 3.6dB 11 G max L 1 1 S 2 1.56 1.9dB 22 The gain of the mismatched transistor is; G S 0 2 21 6.25 8.0dB 62 Example 5 (cont) So the max unilateral transducer gain is G U max 3.6 1.9 8.0 13.5dB T Thus we have 2.5 dB more available gain than required by specs, since the design only requires 11 dB gain. However, the question also asked us to analyze the effect of having: Condition 1: GS = 3 dB and GL = 0 dB Condition 2: GS = 2 dB and GL = 1 dB (Note that these conditions must happens at the same time in order to keep the gain at 11 dB.) 63 Example 5 (cont) For condition 1 (input side), when GS = 3 dB: G g 0.875 G max S S S gS C 1 1 g S S 2 S R S S 11 1 g 1 S S 0.706 120 11 1 1 g S S 2 11 2 0.166 11 64 Example 5 (cont) For condition 1 (output side), when GL = 0 dB: G g 0.640 G max L L L gS C 1 1 g S L 2 L R L L 22 1 g 1 S L 0.440 70 22 1 1 g S L 2 22 2 0.440 22 65 Example 5 (cont) 66 LOW NOISE AMPLIFIER DESIGN In receiver applications especially, it is often required to have a preamplifier with as low a noise figure as possible since, the first stage of a receiver front end has the dominant effect on the noise performance of the overall system. Generally it is not possible to obtain both minimum noise figure and maximum gain for an amplifier, so some sort of compromise must be made. This can be done by using constant gain circles and circles of constant noise figure to select a usable trade of between noise figure and gain. F Fmin 2 RN YS Yopt GS [7.39] 67 LOW NOISE AMPLIFIER DESIGN For a fixed noise figure, F, the noise figure parameter, N, is given as: 2 F Fmin N 1 opt 4 RN Z 0 [7.40] The circles of constant noise figure: CF RF opt [7.41a] N 1 N N 1 opt 2 [7.41b] N 1 68 Example 6 An GaAs FET amplifier is biased for minimum noise figure and has the following S-parameters (Z0 = 50 Ω): S11 = 0.75 < -120 S21 = 2.50 < 80 S12 = 0.00 < 0 S22 = 0.60 < -85 Γopt = 0.62 < 100 Fmin = 1.6 dB RN = 20 Ω For design purposes, assume the unilateral. Then design an amplifier having 2.0 dB noise figure with the max gain that is compatible with this noise figure. 69 Example 6 (cont) Next use the formulas to compute the center and radius of the 2 dB noise figure circle: F F N 1 4R Z 2 min opt N 0.0986 0 C 0.56 100 N 1 opt F R F N N 1 opt N 1 2 0.24 The gain of the mismatched transistor is 70 Example 6 (cont) The noise figure circle is plotted in the figure. Min noise figure (Fmin = 1.6 dB) occurs for ΓS = Γopt = 0.62<100o GS (dB) gS CS RS 1.0 0.805 0.52<60o 0.300 1.5 0.904 0.56<60o 0.205 1.7 0.946 0.58<60o 0.150 It can be seen that GS = 1.7 dB gain circle just intersects the F = 2.0 dB noise figure circle, and any higher gain will result in a worse noise figure. 71 Example 6 (cont) For the output section we choose ΓL = S22* = 0.5<60o for a max GL of: 1 G 1 S 2 L G S 0 1.33 1.25dB 22 3.61 5.58dB 2 21 G U max G G G 8.53dB T S 0 L 72 Example 6 (cont) 73