NAND Flash failure behavior

advertisement

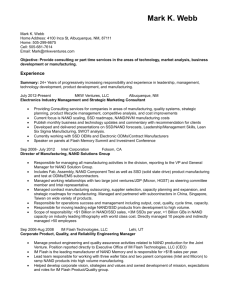

NAND Flash Failure Behavior Sponsored By Micron Technology Inc Group Members and Topics Rob Wells Jeremy Hamblin Firmware Design Roger White Project Introduction System Integration NAND DUT Interface NAND Controller & Timing David Chu Host GUI Interface & Application Conclusions Robert Wells Project Introduction System Integration Introduction to NAND Flash What NAND Flash Memory Is NAND Flash Memory Applications What NAND Flash Memory Is Not Project Concept An Affordable Platform Customizable Usage/Programming Patterns Characterization/Analysis of NAND Behavior System Integration High Level View FPGA System Block Diagram Interface SOPC Builder Overview Component Generation Quartus II Overview Integration of the FPGA system Controller Development NIOS II Overview HAL (Hardware Abstraction Layer) – NIOS II HDL (Hardware Description Language) – Quartus II Device Drivers Firmware Firmware to Controller Integration Host PC to Firmware Integration High Level View Components: • NIOS II Processor • SDRAM • USB HAL Firmware (Hardware Abstraction Layer) • On-Chip Memory • Custom C Code C Code • LCD Display • API (Application Programming Interface) (Jeremy) .c Quartus II .c .v .v NAND HDL (Hardware Flash Controller Description Language) • Custom Verilog Code Verilog Code (Roger) SOPC NIOS II Application GUI Interface SOPC Builder • Program the NAND Flash (System On a Programmable •Chip) Analyze/Display Results (David) High Level View • Analyze Configure Performance Memory Usage • Memory Will NANDRange Flash Work • Datathe Over Pattern Lifespan of a • Number Given Device? of Cycles Application GUI Interface • Program the NAND Flash • Analyze/Display Results (David) System Integration High Level View FPGA System Block Diagram Interface SOPC Builder Overview Component Generation Quartus II Overview Integration of the FPGA system Controller Development NIOS II Overview HAL (Hardware Abstraction Layer) – NIOS II HDL (Hardware Description Language) – Quartus II Device Drivers Firmware Firmware to Controller Integration Host PC to Firmware Integration Clock FPGA development system SOPC Built Generation System (Jeremy) Reset Delay NAND Flash Controller (Roger) System Integration High Level View FPGA System Block Diagram Interface SOPC Builder Overview Component Generation Quartus II Overview Integration of the FPGA system Controller Development NIOS II Overview HAL (Hardware Abstraction Layer) – NIOS II HDL (Hardware Description Language) – Quartus II Device Drivers Firmware Firmware to Controller Integration Host PC to Firmware Integration Example FPGA System With SOPC System Integration High Level View FPGA System Block Diagram Interface SOPC Builder Overview Component Generation Quartus II Overview Integration of the FPGA system Controller Development NIOS II Overview HAL (Hardware Abstraction Layer) – NIOS II HDL (Hardware Description Language) – Quartus II Device Drivers Firmware Firmware to Controller Integration Host PC to Firmware Integration System Integration High Level View FPGA System Block Diagram Interface SOPC Builder Overview Component Generation Quartus II Overview Integration of the FPGA system Controller Development NIOS II Overview HAL (Hardware Abstraction Layer) – NIOS II HDL (Hardware Description Language) – Quartus II Device Drivers Firmware Firmware to Controller Integration Host PC to Firmware Integration System Integration High Level View FPGA System Block Diagram Interface SOPC Builder Overview Component Generation Quartus II Overview Integration of the FPGA system Controller Development NIOS II Overview HAL (Hardware Abstraction Layer) – NIOS II HDL (Hardware Description Language) – Quartus II Device Drivers Firmware Firmware to Controller Integration Host PC to Firmware Integration Firmware to Controller Integration Controller Firmware Buffer Verilog C Code SOPC Builder Quartus II NIOS II System Integration High Level View FPGA System Block Diagram Interface SOPC Builder Overview Component Generation Quartus II Overview Integration of the FPGA system Controller Development NIOS II Overview HAL (Hardware Abstraction Layer) – NIOS II HDL (Hardware Description Language) – Quartus II Device Drivers Firmware Firmware to Controller Integration Host PC to Firmware Integration Host PC to Firmware Integration Phillips ISP1362 WinDriver (Device Driver) (USB) SOPC Builder (HAL) NIOS II (Device Driver) Conclusions System Components Custom Hardware Design (Verilog) Custom Firmware Design (C) Powerful Design Tools Custom Built Application GUI Interface Inexpensive Platform for Testing Analysis of NAND Wear-Out From a Customizable Memory Usage Model Allows Developers to Determine if NAND Flash is a Viable Solution for a Given Application Evaluate Other Aspects of NAND Flash Questions Jeremy Hamblin Firmware Design Firmware Design SOPC Builder System Components Firmware Design (NIOS II) Reset NAND Operation USB Interface Op-Code/Algorithm NAND Flash Addressing Example Algorithm Layout Command Transferring SOPC Builder (System On a Programmable Chip) NIOS II Processor SDRAM Displays Global Reset USB Buffer Read Enable •Instruction & Data •Block Mapping & Status Firmware Design SOPC Builder System Components Firmware Design (NIOS II) Reset NAND Operation USB Interface Op-Code/Algorithm NAND Flash Addressing Example Algorithm Layout Command Transferring Firmware Design Reset NAND Operation First Operation After NAND Power Up Occurs During System Initialization Places NAND DUT (Device Under Test) in a Known State Firmware Design SOPC Builder System Components Firmware Design (NIOS II) Reset NAND Operation USB Interface Op-Code/Algorithm NAND Flash Addressing Example Algorithm Layout Command Transferring Firmware Design USB Interface Generates IRQ (Interrupt ReQuest) ISR (Interrupt Service Routine) Receives Data Sent From Host PC and Parses Data 00 00 00 00 | 00 00 00 00 | 00 00 00 00 | 00 00 00 00 - 16 Bytes 00 00 00 00 - Byte0 Start Address – 3 Bytes Padding End Address – 3 Bytes Algorithm Padding – 1 Byte OP Code # Cycles – 3 Bytes Padding – 5 Bytes Firmware Design Op-Code Types Read ID Write Read Algorithm Types Continuous Checker Board Random Firmware Design NAND Flash Addressing Blocks Pages Bytes Firmware Design NAND Flash Addressing Algorithm Example Page N … Page 1 Page 0 Page N-1 Erased Programmed Block-0 Block-1 … Block N-1 Block N Continuous Cycle I Cycle II Checker Board Firmware Design SOPC Builder System Components Firmware Design (NIOS II) Reset NAND Operation USB Interface Op-Code/Algorithm NAND Flash Addressing Example Algorithm Layout Command Transferring Firmware Design Command Transferring Commands & Data Transferred Through Buffer Different Write- 2119 Bytes Transferred to NAND, 0 Returned Read- 7 Bytes Transferred to NAND, 2112 Returned Erase- 5 Bytes Transferred to NAND, 0 Returned Read Status- 1 Byte Transferred, 1 Returned Each Data and Command Requirements NAND Command Type Has its Own Buffer Function Removes All NAND Device Timing Constraints From the Firmware Firmware Too Slow Firmware Design Conclusion Command Received Over USB Parsed in USB ISR Execution of Op-Code Command and Data are Passed to NAND Controller Through the Buffer Command is Executed From Start Address to End Address Repeated for # of Cycles Given in Command From Host Block Status Returned Over USB Questions Roger White NAND DUT Interface NAND Controller & Timing NAND DUT Interface Daughter Card Our Own?? Boise State’s NAND DUT Interface NAND Controller & Timing Pins to NAND Chip Operations NAND Controller & Timing Pins to NAND chip CLE (Command Line Enable) CE# (Chip Enable) WE# (Write Enable) ALE (Address Line Enable) R/B (Ready/Busy) RE# (Read Enable) WP# (Write Protect) I/Ox (Input/Output) NAND Controller & Timing Pins to NAND Chip Operations NAND Controller & Timing Operations Read Program Erase Read Status Reset Read ID NAND Controller & timing Program Operation NAND Controller & Timing Erase Operation NAND Controller & Timing Reset Operation Conclusions NAND DUT Interface Daughter Card NAND Controller & Timing Pins Operations Questions? User Interface, USB, and Conclusions By: David Chu Overview User Interface Command Interface Results Interface Functionality USB Functionality, Database Information, and XML File Description Charts Interface Functionality and Scripting Information Functionality and Bit Organization Conclusions Methods, Results, and Future Improvements Three Parts to the UI Command Interface - Allows the user to specify the method and method parameters that are sent to the controller. Results Interface - Allows the user to view, store, load, and search through the results stored in a database Charts Interface - Allows the viewer to visually see the results in graphical form Command Interface Command Interface Functionality Allows the user to easily construct commands and send them to the controller Allows the user to load in scripts to automate the controller Allows the user to link to the Results Interface Script Files Allow the user to automate the NAND Flash test application through a comma delimited file. Script files are written in the following manner: Read,000000000101111001000000,000000000110000111000000,Full,200 Results Interface Results Interface Functionality Allows the user to easily visualize data that is stored in the database. Allows the user to sort items in the table by columns Allows the user to search the data for specific results or a range of results Allows the user to load or save database information into or from an XML file Allows the user to link to the Charts Interface Database Information Uses SQL and runs on Microsoft SQL Server 2005 Contains one table with the following elements: ID, Cycle, MemoryAddress, FunctionName, Status, and Algorithm Contains the following stored procedures: FindID, RemoveID, RemoveAll, InsertID, and UpdateID XML Files Generated from database when the user selects the save button Allows the user to manipulate the results to their specific needs Allows the user to import data into other applications that support XML <?xml version="1.0" standalone="yes" ?> - <NewDataSet> - <FlashStatusTable> <ID>1</ID> <Cycle>1</Cycle> <MemoryAddress>6</MemoryAddress> <FunctionName>Write</FunctionName> <Status>Bad</Status> <Algorithm>Checker</Algorithm> </FlashStatusTable> - <FlashStatusTable> <ID>2</ID> <Cycle>15</Cycle> <MemoryAddress>4</MemoryAddress> <FunctionName>Write</FunctionName> <Status>Bad</Status> <Algorithm>Checker</Algorithm> </FlashStatusTable> - <FlashStatusTable> Charts Interface Chart Interface Functionality Allows the user to visually represent the total number of failures over cycles Allows the user to turn on and off horizontal and vertical grids Overview User Interface Command Interface Results Interface Functionality USB Functionality, Database Information, and XML File Description Charts Interface Functionality and Scripting Information Functionality and Bit Organization Conclusions Methods, Results, and Future Improvements USB Information Connection: USB 2.0 connection Transfer Rate: USB Full-Speed Transfer Rate (12 Mbps) Transfer Method: USB Interrupt Transfers PnP Compatible Bit Organization USB Interface Sends 16-Bytes Bytes are Transferred Using Big Endian 00 00 00 00 | 00 00 00 00 | 00 00 00 00 | 00 00 00 00 - 16 Bytes 00 00 00 00 - Byte0 Start Address – 3 Bytes Padding End Address – 3 Bytes Algorithm Padding – 1 Byte OP Code # Cycles – 3 Bytes Padding – 5 Bytes Overview User Interface Command Interface Results Interface Functionality USB Functionality, Database Information, and XML File Description Charts Interface Functionality and Scripting Information Functionality and Bit Organization Conclusions Methods, Results, and Future Improvements Project Synopsis Method – used the Altera DE2 development board to create a system consisting of a memory module, a processor, and an FPGA controller in order to enable communication between a host PC test application and NAND Flash. Host PC Simple GUI USB ver 2.0 FPGA/Processor Dev System DUT Project Synopsis Cont. Results – created an affordable and easy to use application that allows developers to run multiple tests on NAND Flash and easily visualize the results through tabular and graphical methods Future Improvements Redesign the GUI to work with multiple operating systems Configure the NAND Flash controller to operate with NAND Flash from other manufacturers Use caching methods to improve the performance of the NAND Flash test application Questions Thank You: Ken Stevens Dennis Zattiero Dean Klein Ken Koenig