Concept Notes - Online Guru Jee

advertisement

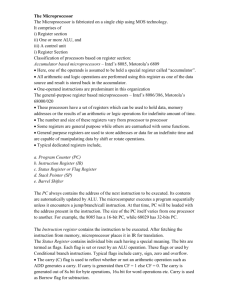

Computer System Architecture BCA-403 Computer Architecture: Computer architecture is the conceptual design and fundamental operational structure of a computer system. It may also be defined as the science and art of selecting and interconnecting hardware components to create computers that meet functional, performance and cost goals. Instruction Code: The collection of bits that instruct the computer to perform a specific operation is called an instruction code. It is divided into two parts operation (op code) and address part. Op code part tells which operation is to be performed while address part tell on which it is to be performed. Common Bus System: Buses are the set of wires which is used to carry signals from one place to other place. Three types of buses can exist in a computer system Data Bus, Address and Control Bus. Registers: Registers are the temporary storage elements during the execution of instructions. When operands are brought into the processor, they are stored in the following registers. Register Symbols DR AR AC IR PC TR INPR OUTR No of Bits 16 12 16 16 12 16 8 8 Register Name Data Register Address Register Accumulator Instruction Register Program Counter Temporary Register Input Register Output Register Function Holds Memory Operand Holds address for Memory Processor Register Holds Instruction Code Holds Address of Instruction. Holds Temporary Data Holds Input Character Holds output Character Computer Instruction: It is a information which is given to a computer to perform a specific task. The basic computer uses three instruction code formats. Memory Reference Instruction, Register Reference instruction and input/output instruction. Instruction cycle: Any program is executed by going through a cycle for each instruction. In the basic computer each instruction cycle has the following parts: 1. Fetch an instruction from memory. 2. Decode the instruction. 3. Read the effective address from memory if the instruction has an indirect address. 4. Execute the instruction. Memory word: The natural unit of organization of memory is word. The size of word is different for different machine such as 16 bits, 32 bits, etc. Memory Reference Instructions: In memory reference instruction at first memory reference is given to read data from memory and transfer it to a register where they can be operated on with logic circuits. Following Memory Reference Instructions can exist in a computer. Instruction AND ADD LDA STA BUN BSA ISZ Work This instruction performs the AND logic operation on pairs of bits in AC and the memory word This instruction performs the ADD operation on pairs of bits in AC and the memory word This instruction is used to transfers the memory word to accumulator. This Instruction is used to store the content of accumulator into the memory word This instruction is used to transfer the program to the instruction located at the effective address. This is a useful instruction for branching to a portion of the program called a subroutine. At that time to skip the next instruction PC is incremented by one in order. Microinstruction format: A micro-instruction is a simple command that makes the hardware operate properly. The format is unique to each computer. Below is the example of microinstruction format which consist of 20 bits. 3 3 3 2 2 7 F1 F2 F3 CD BR AD here CD is condition for branching, BR branch field, AD is address field. The three fields F1, F2, and F3 specify micro operations for the computer. The CD field selects status bit conditions. The BR field specifies the type of branch to be used. The AD field contains a branch address. Micro-operation, Micro-program, Symbolic microinstruction: A micro-operation is an elementary operation which is performed on the data stored in registers. The micro-program consists of micro-instructions that specify various internal control signals for execution of register micro-operations. Each line of the assembly language micro-program defines a symbolic microinstruction. Each symbolic microinstruction is divided into five fields - label, microoperations, CD, BR, and AD. Micro program sequencer: The basic components of a micro-programmed control unit are the control memory and the circuits that select the next address. The address selection part is called a micro-program sequencer. Processor clock: No of basic operation that processor can perform per unit time are controlled by a regular stream of pulses called bears or ticks issued by system or processor clock. The speed of clock is called its frequency measured in million per second. Hardwired control VS Micro programmed control: When the control signals are generated by h/w using conventional logic design techniques such as gates, flip-flops, decoders and other digital circuit called hardwired control. Hardwired control comes under RISC. In micro-programmed, control information is stored in a control memory, and the control memory is programmed to initiate the required sequence of micro-operations Timing and Control: A master clock generator controls the timing for all registers in the basic computer. The clock pulses are applied to all flip-flops and registers in the system and in the control unit. The clock transition does not change the state of a register unless the register is enabled by a control signal. CPU organization: Most computers fall into one of three types of CPU organizations: 1. Single accumulator organization. 2. General register organization. 3. Stack organization. Single accumulator organization: In accumulator-type organization all operations are performed with an implied accumulator register. The instruction format in this type of computer uses one address field. General register organization: General register organization uses only two or three address fields . Each address field may specify a processor register or a memory word. Stack organization: A stack is organised in cpu in the form of registers as well as in memory. Computers with stack organization would have PUSH and POP instructions which require an address field. Register stack and Memory stack : Stack is a temporary storage during the execution for the processing of instructions. Its follow LIFO rule. Two types of stack exist register and memory stack. If stack is constituted in memory(RAM) attached to cpu called memory stack. If stack is organised as a collection of a finite No of memory words register stack. Control word: The microinstruction contains a control word that specifies one or more micro-operations for the data processor. Instruction format: An instruction format defines the layout of the bits of an instruction. Zero address: It does not use an address field. One address: One-address instructions use an implied accumulator (AC) register for all data manipulation. Two address: In two address instruction format each address field can specify either a processor register or memory word. Three address instructions: Three-address instruction formats can use each address field to specify either a processor register or a memory operand. Instruction Fields: OP-code field: This field specifies the operation that is to be performed. Address field: It designates memory address(es) or a processor register(s). Mode field : Determines how the address field is to be interpreted (to get effective address or the operand). Instruction sets: Instruction set tells which type of operation to be performed. Addressing modes: Specifies a rule for interpreting or modifying the address field of the instruction (before the operand is actually referenced). TYPES OF ADDRESSING MODES: • Register Mode: Address specified in the instruction is the register address. • Register Indirect Mode: Instruction specifies a register which contains the memory address of the operand. • Auto-increment or Auto-decrement Mode: When the address in the register is used to access memory, the value in the register is incremented or decremented by 1 automatically. • Direct Address Mode: Instruction specifies the memory address which can be used directly to access the memory. • Indirect Addressing Mode: The address field of an instruction specifies the address of a memory location that contains the address of the operand. • Relative Addressing Modes: The Address fields of an instruction specifies the part of the address(abbreviated address) which can be used along with a designated register to calculate the address of the operand. RISC vs. CISC: Complex Instruction Set Computer: A computer with a large number of instructions is classified as a complex instruction set computer, are implemented with micro-programmed controllers.. Reduced Instruction Set Computer: A computer with a less number of instructions is classified as a reduced instruction set computer, are implemented with hardwired controllers. Parallel processing: A Parallel processing is a term used to denote a large class of techniques that are used to provide simultaneous data-processing tasks for the purpose of increasing the computational speed of a computer system. Pipeline processing, vector processing and array processing is the example of parallel processing. Flynn’s Classification: Parallel processing may occur in instruction stream, data stream or in both. Flynn’s Classification divides computers into four groups: Single instruction stream, single data stream (SISD): SISD represents the organization of a single computer that contains a control unit, a processor unit, and a memory unit. Single instruction stream, multiple data stream (SIMD): SIMD represents an organization that is inclusive of any processing units under the supervision of a common control unit. Multiple instruction stream, single data stream (MISD): MISD structure is only of theoretical interest since no practical system has been constructed using this organization. Multiple instruction stream, multiple data stream (MIMD): MIMD organization refers to a computer system capable of processing several programs at the same time. Space time diagram: This is a diagram that shows the segment utilization as a function of time. Usually the behaviour of a pipeline can be illustrated with a space time diagram. Pipelining: Pipelining is a technique of decomposing a sequential process into sub-process operations, with each sub-process being executed in a special dedicated segment that operates concurrently with all other segment. Type of Pipelining: Software Pipelining: Can Handle Complex Instructions and allows programs to be reused. Hardware Pipelining: Help designer manage complexity , a complex task can be divided into smaller, more manageable pieces. Instruction pipeline: Instruction Pipeline - An instruction pipeline reads consecutive instructions from memory, While previous instructions are processed in other segments, This causes overlapping of fetch and execute face and performance of simultaneous operations. Arithmetic pipeline: They are employed to implement floating point operations, multiplication of fixed point numbers and similar computations encountered in scientific problems. Speedup ratio: The speedup ratio of pipeline processing over an equivalent non pipeline processing is define by the ratio given below: S = ntn/(k+n-1)tp where k is the no of segements, tn is the total time required to complete n task, tp is the clock cycle time. Pipeline conflicts: pipeline conflicts are the difficulties that can cause the instruction pipeline to deviate from its normal operation can be divided into three types. Resource Conflict: Caused by access to memory by two segments at the same time. Data Dependency Conflict: Can be arisen when an instruction depends on the result of a previous instruction. Branch Difficulties: Arise from branch and other instructions that change the value of PC. Input output interface: Input-output interface gives a method or communication link for transferring information between internal memory and I/O devices. It consist of data registers called ports, a control register, a status register, bus buffers, and timing and control circuits. Asynchronous and Synchronous Data Transfer: If the registers in the interface share a common clock with the cpu registers, the transfer between two units is said to be synchronous. If internal timing of each unit is independent from each other and uses its own private clock for internal registers then two units are said to be asynchronous to each other. Strobe control and handshaking are the method of asynchronous data transfer. Strobe Control: Strobe control is the method of asynchronous data transfer. The strobe is a single control line that informs the destination unit when a valid data word is available in the bus, it is activated either by source unit or destination unit. Handshaking: In handshaking method, One control line is in the same direction as the data flow in the bus from the source to the destination. It is used by the source unit to inform the destination unit whether there are valid data in the bus. The other control line is in the other direction from the destination to the source. It is used by the destination unit to inform the source whether it can accept data. Baud Rate: The baud rate is defined as the rate at which serial information is transmitted and is equivalent to the data transfer in bits per second. Interrupt: Interrupt are the signals generated by any device to alert or inform other devices. Modes of Transfer: Data transfer between the central computer and I/O devices may be handled in either of three possible modes. 1. Programmed I/O : In program initiated I/0 each data item transfer is initiated by an instruction in the program. 2. Interrupt-initiated I/O: In interrupt-initiated I/0 special commands are given to inform the interface to issues an interrupt request signal when the data is available from the device. 3. Direct memory access (DMA): In DMA, the interface transfers data into and out of memory unit through the memory bus. Priority Interrupt: A priority interrupt establishes a priority to decide which condition is to be serviced first when two or more requests arrive simultaneously. Establishing the priority of simultaneous interrupts can be done by s/w or h/w. Polling: A polling procedure is used to identify the highest priority source by s/w means. In polling there is one common branch address for all interrupts. The program that takes care of interrupts begins at the branch address and polls the interrupt sources in sequence. Daisy chain Priority: It is a h/w method consists of a serial connection of all the devices that request an interrupt. In daisy chain the device with highest priority is placed in the first position, followed by lower priority devices up to the device with the lowest priority. Priority encoder: The priority encoder is a circuit that implements the priority function such as if two or more inputs arrive at the same time, the input having the highest priority should be taken precedence. DMA: DMA is a technique that remove the CPU from the path and letting the peripheral device manage the memory buses directly for increasing the speed of data transfer among storage devices/memory. DMA Controller: A DMA Controller takes over the buses to manage the transfer directly between the i/o device and memory due to idle CPU. Memory hierarchy: Memory hierarchy decides which memory is to be accessed to increase the speed of computation. It works only if the frequency of access to the slower memories is significantly less than the faster memories. In hierarchy first place is given to registers, then cache, then main, then disk, then magnetic disk and finally magnetic tape/optical disk. Common terms used in memory: Access Modes: the access mode in which the information is accessed from the memory. The information from memory devices can be accessed in the following ways: Random Access; Sequential Access; Direct Access. Access Time: The access time is the time required between the request made for a read or write operation till the time the data is made available or written at the requested location. Cycle Time: It is defined as the minimum time elapsed between two consecutive read requests. Data Transfer Rate: The amount of information that can be transferred in or on of the memory in a second is termed as data transfer rate or bandwidth. Usually it is measured in bits per second. Memory Management: A memory management system is a collection of hardware and software procedures for managing the various program residing in memory. The basic components of memory management unit are: 1. A facility for dynamic storage relocation that maps logical memory references into physical memory addresses. 2. A provision for sharing common programs stored in memory. 3. Protection of information against unauthorised access among users and preventing users from changing operating system function. RAM: Main memory is a random access memory. It is normally organised (logically) as words of fixed length. The length of a word is called word length. Each of these memory words has an independent address and each have same number of bits. Read Only Memories A ROM is basically a hardwired combinational circuit, can be used for storing Micro programs, Systems Programs, and subroutines. It can be categorised into Programmable ROM (PROM), EPROMs (Erasable PROMs) and EEPROMS (Electrically Erasable ROMs). Magnetic disk: It is also a storage device have high speed rotational surfaces coated with magnetic material and accessed through read write mechanism. Magnetic tapes: Magnetic tape is a storage device with sequential access through read write mechanism. CACHE MEMORY These are small fast memories placed between the processor and the main memory to increase the overall speed of memory references using mapping processes. Mapping can be done by three ways. Associative mapping. Direct Mapping. Set associative mapping. Associative Memories In associative memories any stored item can be accessed directly by assigning the contents of the item in question, such as name of a person, account number, number etc., as an address. associative memories are also known as content addressable memories (CAMS). The entity chosen to address the memory is known as the key. Virtual Memory: Virtual memory increases the available memory of computer has by enlarging the "address space," or places in memory where data can be stored by using hard disk space for additional memory allocation. It must be mapped back to real memory in order to be used.