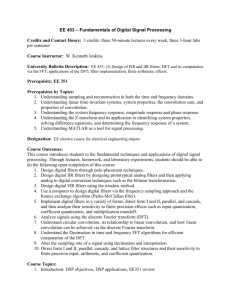

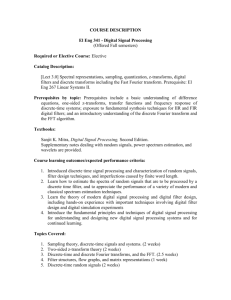

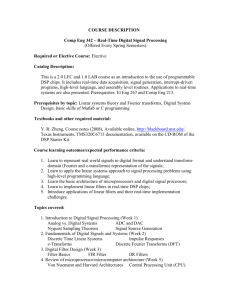

Digital Signal Processing

advertisement

Digital Signal Processing Digital Signal Processing uses unique type of data i.e. signal, for processing Signals A signal refers to any continuous function of one or more variables such as time, space, frequency, etc. e.g. Voltage across a resister Velocity of a vehicle Light intensity of an image Temperature, pressure inside a system Signal Processing Signal Processing refers to the science of analyzing time-varying physical process. There are two category of signal processing: Analog Signal Processing The term is used to describe a waveform that is continuous in time and can take a continuous range of amplitude values. It will be more correct to say continuous signal processing. Digital Signal Processing A digital signal, which is discrete-time-signal, is not represented by a continuous waveform and the discrete-time signal quantities. The amplitude that we know one amplitude value of signal at discrete instants in time. Digital Signal Processing Signal to be converted to a form that can be processed by a digital System. Analog I/P Signal A/D Converter Digital I/P Signal Digital Signal Processor Digital O/P Signal D/A Converter Analog O/P Signal Benefits: Digital Signal Processing • Flexibility of the system offered by the software component • Better control of accuracy requirements • Ease of storage and offline processing • Lower cost of processors • Compression and coding techniques are efficient to implement Limitations • Speed of operation of digital processors • Noise due to quantization and switching DSP Study Related with Technical DisciplinesScience, Engineering and Mathematics DSP Application DSP Technology DSP technology is with its own mathematics, algorithms and the techniques that are used to manipulate the signals in digital form. DSP technology is nowadays commonplace in such devices as mobile phones, multimedia computers, video recorders, CD players, hard disc drive controllers and modems, and will soon replace analog circuitry in TV sets and telephones. Telecommunication Multiplexing Compression Echo Control Audio Processing Music Speech generation Speech recognition -Continued Echo Location Sonar Radar Reflection Seismology Image Processing Medical Digital Filter Filters • Filters are signal conditioners • Filter functions by accepting an input signal, blocking prespecified frequency components and passing the original signal minus those components to the output. Filter Types • Lowpass- Allows only low frequency signals to its outputs. • Highpass-Allows only high frequency signals to its outputs. • Bandpass-Allows only output signals within its narrow, government-authorized range of frequency spectrum. • Bandstop-Allows both low and high frequencies, but blocks a predefined range of frequencies. DSP Filtering Procedures DFT (Discrete Fourier Transform) DTFT (Discrete Time Fourier Transform) DTFS (Discrete Time Fourier Series) FFT (Fast Fourier Transform) Discrete Fourier Transform (DFT) Powerful procedures for digital signal processing. It enables us to analyze, manipulate, and synthesize signals in ways not possible with continuous signal processing. A mathematical procedure used to determine the harmonic, or frequency, content of a discrete signal sequence. DFT defined as the discrete frequency-domain sequence X(m) as: N-1 X(m) = x(n)e –j2 nm/N n=0 Where, x(n) is a discrete sequence of time-domain sampled values of the continuous variable x(t). j = -1 m= the index of the DFT output in the frequency domain. M=0,1,2,3,….,N-1 n= the time-domain index of the input samples, n=0,1,2,3,……,N-1 N=the number of samples of the input sequence and the number of frequency points in o/p. Fast Fourier Transform (FFT) • FFT is an algorithm for efficient computation of DFT • Divide and conquer approach- Radix-2, Radix-4 Decimation in time/frequency • Goertzel Algorithm- DFT computed as the output of a linear filter Digital Filters Takes a digital input, gives a digital output. There are two main types of digital filters: Finite Impulse Response (FIR) Filter FIR digital filters use only current and past input samples to obtain a current output sample value. Infinite Impulse Response (IIR) Filter In IIR filters, some of the filter’s previous output samples are used to calculate the current output sample. Programmable DSPs (P-DSP) The P-DSPs are specially designed for digital signal processing application. The main components of P-DSPs are: I) Multiplier & Multiplier Accumulator (MAC) It requires array multiplication.The multiplication as well as accumulating to be carried out using hardware elements by two ways: A dedicated MAC unit implemented in hardware which has integrated multiplier and accumulator in a single hardware unit. Use of multiplier and accumulator separately. II) The Processor Architecture There are mainly two types of architecture of microprocessor: a) Von Neumann Architecture Processing Unit Result Operands Status Data Bus Opcode Instructions Data/Instruction Control Unit Address Data and Program Memory In this architecture a single address bus and a single data bus for accessing the programme as well as data memory area. So if MACD (MAC data) instruction is to be executed in a machine with this architecture it requires four clock cycles. That is due to a single address and data bus. b) Harvard Architecture Result/Operands Processing Unit Status Opcode Control Unit Data Memory Address Instructions Address Program Memory In this architecture there are two separate buses for the programme and data memory. Hence the content of programme memory and data memory can be accessed in parallel. The instruction code can be fed from the programme memory to the control unit while the operand is fed to the processing unit from the data memory. The processing unit consist of the registers and processing elements such as MAC units, multiplier, ALU, Shifters etc. The P-DSP follow the modified Harvard Architecture Results/Operands Processing Unit Status Data Memory Opcode Address Control Unit Instructions Address Program Memory In this architecture one set of bus is used to access a memory that has both programme and data and another that has data alone. Data can also be transferred from one memory to another. This modified Harvard Architecture is used in several P-DSPs e.g. P-DSPs from Texas Instruments and analog devices. III) Memory for P-DSPs 1. Multiple Access Memory The number of memory accesses/clock period can be increased by using a high-speed memory that permits more than one memory access/clock period. e.g. The DARAM (dual access RAM) permits two memory access/clock period. Multiple accesses may be connected to the processing units of the P-DSPs by using the Harvard Architecture 2) Multiported Memory The dual port memory has two independent data and address buses as shown in the following fig. Address Bus 1 Address Bus 2 Data Bus 1 Dual Port Memory Data Bus 2 Two memory access is can be achieved in a clock period. Multiported memory dispense with the need for storing the programme and data in two different memory chips in order to permit simultaneous access to both data and programme memory. E.g. Motorola DSP561XX processor has a single ported programme memory and a dual ported data memory. IV) Processor Architecture Examples i) An Overview of Motorola DSP563XX Processors The Motorola DSP56300 family P-DSPs is deployed in a number of applications such as wireless infrastructure, Internet telephony, based transceiver station, Network Interface cards, base station controllers and high speed modem banks. The Motorola DSP56300 core is compose of: Data ALU Multiplier Accumulator (MAC) Address Generation Unit (AGU) Programme Control Unit (PCU) On-chip peripherals On-chip Memory Internal Buses Direct Memory Access (DMA) ii) An Overview of TMS320C5X (Texas Instruments) The TI has a large number of processors in its family this are used in number of areas such as; toys, hard disk drives, modems, cell phones, filters, hi-fi systems, voice mail, barcode reader, motor control, video telephone etc. Architecture of TMS320C5X DSPs This processor has advanced Harvard architecture with separate memory bus structure for programme and data. This DSP composed of: Bus structure Central arithmetic logic unit (CALU) Auxiliary Register ALU (ARAU) Index Register (INDX) Auxiliary Register compare Register (ARCR) Block Move Address Register (BMAR) Block Repeat Registers (RPTC, BRCR, PASR, PAER) Parallel Logic Unit (PLU) Memory-Mapped Registers Program Controller On-Chip Memory On-Chip Peripherals