Hardware Project Unit 2 Review on Logic Elements Sau

advertisement

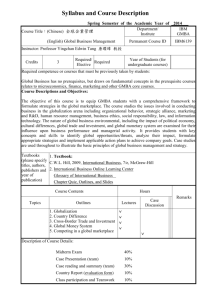

Unit 2 Reviews on Logic Elements Department of Communication Engineering, NCTU 1 2.1 Decoders and Encoders Department of Communication Engineering, NCTU 2 Hardware Project Unit 2 Review on Logic Elements Sau-Hsuan Wu 3-to-8 line decoder The i th output is 1 if the input binary value is equal to i Department of Communication Engineering, NCTU 3 Hardware Project Unit 2 Review on Logic Elements Sau-Hsuan Wu 4-to-10 line decoder Department of Communication Engineering, NCTU 4 Hardware Project Unit 2 Review on Logic Elements Sau-Hsuan Wu In general a n-to-2n decoder can generate the all 2n minterms Because an n-input decoder generates all of the minterms of n variables, n-variable functions can be realized by ORing together selected minterm outputs from a decoder Department of Communication Engineering, NCTU 5 Hardware Project Unit 2 Review on Logic Elements Sau-Hsuan Wu An encoder performs the inverse function of a decoder E.g. 8-to-3 priority encoder If more that one input is 1, the highest number determines the output D is 1 if any input is 1, otherwise d is 0 Department of Communication Engineering, NCTU 6 2.2 Register and Register Transfers Department of Communication Engineering, NCTU 7 Hardware Project Unit 2 Review on Logic Elements Sau-Hsuan Wu A 4-bit register is composed of 4 D-type FFs which share a common clock, clear (Clr) and chip enable (CE) Department of Communication Engineering, NCTU 8 Hardware Project Unit 2 Review on Logic Elements Sau-Hsuan Wu The symbol notation for a 4-bit register Department of Communication Engineering, NCTU 9 Hardware Project Unit 2 Review on Logic Elements Sau-Hsuan Wu Data are passed from one register to another. In this case, whether Ai or Bi is sent to Di depends on En Department of Communication Engineering, NCTU 10 Hardware Project Unit 2 Review on Logic Elements Sau-Hsuan Wu A 8-bit register with tri-state output enable (En), and its corresponding symbol Department of Communication Engineering, NCTU 11 Hardware Project Unit 2 Review on Logic Elements Sau-Hsuan Wu Registers use output enable (for releasing data) and chip enable (for accepting data) to transfer data on a bus Department of Communication Engineering, NCTU 12 Hardware Project Unit 2 Review on Logic Elements Sau-Hsuan Wu Accumulator : the output of adder is fed back as one of a addend Department of Communication Engineering, NCTU 13 2.3 Shift Registers Department of Communication Engineering, NCTU 14 Hardware Project Unit 2 Review on Logic Elements Sau-Hsuan Wu A shift register is a register whose data can be shifted right or left A 4-bit right-shift register Department of Communication Engineering, NCTU 15 Hardware Project Unit 2 Review on Logic Elements Sau-Hsuan Wu The timing diagram of a 4-bit right shift register Department of Communication Engineering, NCTU 16 Hardware Project Unit 2 Review on Logic Elements Sau-Hsuan Wu A right-shift register with inverted rotation feedback Two possible output patterns which depend on the initial state This is called Johnson counter Department of Communication Engineering, NCTU 17 2.4 Design of Binary Counters Department of Communication Engineering, NCTU 18 Hardware Project Unit 2 Review on Logic Elements Sau-Hsuan Wu A synchronous counter is a counter whose FFs are all driven by a clock. While for a asynchronous counter, the output of FF serves as a driving clock of the next FF A 3-bit synchronous counter implemented with T-FFs Department of Communication Engineering, NCTU 19 Hardware Project Unit 2 Review on Logic Elements Sau-Hsuan Wu Design the functions of TC , TB , and TA with a state table and a truth table First, draw a stable which lists the present state and the next state, then draw the truth table of the functions Department of Communication Engineering, NCTU 20 Hardware Project Unit 2 Review on Logic Elements Sau-Hsuan Wu Logic minimizations with the Karnaugh map Department of Communication Engineering, NCTU 21 Hardware Project Unit 2 Review on Logic Elements Sau-Hsuan Wu For D-FFs, DA is equal to the next state of FF A. So we only need a state table for counters designed with D-FFs Department of Communication Engineering, NCTU 22 Hardware Project Unit 2 Review on Logic Elements Sau-Hsuan Wu An alternative design with D-FFs Department of Communication Engineering, NCTU 23 Hardware Project Unit 2 Review on Logic Elements Sau-Hsuan Wu Design of up-down counter The state table and the state graph of a up-down counter Department of Communication Engineering, NCTU 24 Hardware Project Unit 2 Review on Logic Elements Sau-Hsuan Wu The logic functions of inputs One can verify the function by setting U=0 and D=1, or vice versus. For example, U=0 and D=1 Department of Communication Engineering, NCTU 25 Hardware Project Unit 2 Review on Logic Elements Sau-Hsuan Wu A up-down counter synthesized with D-FFs Department of Communication Engineering, NCTU 26 Hardware Project Unit 2 Review on Logic Elements Sau-Hsuan Wu Design of loadable counter with count enable Department of Communication Engineering, NCTU 27 Hardware Project Unit 2 Review on Logic Elements Sau-Hsuan Wu The next-state equations Department of Communication Engineering, NCTU 28 Hardware Project Unit 2 Review on Logic Elements Sau-Hsuan Wu Design of loadable up-dn counter with count enable? Realize this counter with GAL 22V10 Due on the next meet Department of Communication Engineering, NCTU 29 2.5 Counter of Other Sequences Department of Communication Engineering, NCTU 30 Hardware Project Unit 2 Review on Logic Elements Sau-Hsuan Wu A five state counter Define the next states of three unused states 001、101、110 as unspecified The counter can be realized with T-FFs T =present state’ next state List the truth table for the next states of TA , TB , TC Use the Karnaugh map Department of Communication Engineering, NCTU 31 Hardware Project Unit 2 Review on Logic Elements Sau-Hsuan Wu Notice that T = Q+ Q So, first design Q+ = f (A,B,C) Use Karnaugh map for Q=0 and Q=1, respectively For Q=0, have T = Q+ For Q=1, have T = (Q+ )’ Department of Communication Engineering, NCTU 32 Hardware Project Unit 2 Review on Logic Elements Department of Communication Engineering, NCTU Sau-Hsuan Wu 33 Hardware Project Unit 2 Review on Logic Elements Sau-Hsuan Wu After simplification TA C B TB C A CB TC C B CB Notice that even if the next state of 001,101 and 110 are not specified at the beginning, they are assigned certain values implicitly while being used as the don’t care conditions for circuit simplifications Department of Communication Engineering, NCTU 34 Hardware Project Unit 2 Review on Logic Elements Sau-Hsuan Wu Circuit realization Department of Communication Engineering, NCTU 35 Hardware Project Sau-Hsuan Wu The effects of don’t care conditions Unit 2 Review on Logic Elements When CBA=001, TC TB TA = 110, then C+B+A+ =111 When CBA=101, TC TB TA = 011, then C+B+A+ =110 When CBA=110, TC TB TA = 101, then C+B+A+ =011 The final counter Department of Communication Engineering, NCTU 36 Hardware Project Unit 2 Review on Logic Elements Sau-Hsuan Wu An alternative design with D-FFs This is much easier since DC = C+, DB = B+ and DA = A+ So, the functions are DC B DB C BA DA CA BA A(C B ) Department of Communication Engineering, NCTU 37 2.6 Derivation of Flip-Flop Input Equations Department of Communication Engineering, NCTU 38 Hardware Project Unit 2 Review on Logic Elements Sau-Hsuan Wu In counter design, we mainly derive the input equations of FFs. This can be done either with the true table of the present states and the next states, or with the next-state map Department of Communication Engineering, NCTU 39 Hardware Project Unit 2 Review on Logic Elements Department of Communication Engineering, NCTU Sau-Hsuan Wu 40 Hardware Project Unit 2 Review on Logic Elements Department of Communication Engineering, NCTU Sau-Hsuan Wu 41 2.7 Programmable Logic Array Department of Communication Engineering, NCTU 42 Hardware Project Unit 2 Review on Logic Elements Sau-Hsuan Wu A programmable logic array (PLA) with n inputs and m outputs is a device that can realize m functions of n variables by means of sum-of-products. A PLA consists of an AND array with n input lines and a OR array with m output lines Department of Communication Engineering, NCTU 43 Hardware Project Unit 2 Review on Logic Elements Sau-Hsuan Wu An example OR Array AND Array Department of Communication Engineering, NCTU 44 2.8 Programmable Array Logic Department of Communication Engineering, NCTU 45 Hardware Project Unit 2 Review on Logic Elements Sau-Hsuan Wu Different PLA, the product term of a programmable array logic (PAL) can not be shared by multiple OR gates. Besides, the number of inputs of the OR is fixed and limited, e.g. Department of Communication Engineering, NCTU 46 Hardware Project Unit 2 Review on Logic Elements Sau-Hsuan Wu A commercial device : GAL20V8B Department of Communication Engineering, NCTU 47 Hardware Project Unit 2 Review on Logic Elements Department of Communication Engineering, NCTU Sau-Hsuan Wu 48 Hardware Project Unit 2 Review on Logic Elements Department of Communication Engineering, NCTU Sau-Hsuan Wu 49 Hardware Project Unit 2 Review on Logic Elements Department of Communication Engineering, NCTU Sau-Hsuan Wu 50 2.9 Programming PAL with ABELHDL http://mazsola.iit.uni-miskolc.hu/cae/docs/xabel.html Department of Communication Engineering, NCTU 51 Hardware Project Unit 2 Review on Logic Elements Sau-Hsuan Wu Basic Boolean operations MODULE and_ff2 TITLE 'And gate and flip-flop' input_1,input_2,Clk pin; input_1,input_2,Clk,reset,!oe pin; output_q pin istype 'reg_d'; Equations output_q.clk = Clk; output_q.ar = reset; output_q.q := input_1 & input_2; output_q.oe = oe; END Department of Communication Engineering, NCTU 52 Hardware Project Unit 2 Review on Logic Elements Department of Communication Engineering, NCTU Sau-Hsuan Wu 53 Hardware Project Unit 2 Review on Logic Elements Sau-Hsuan Wu Adder MODULE adder TITLE 'full adder block' a, b, cin, sin sum, carry pin ; pin istype ‘com'; Equations sum = ((a & b) $ sin) $ cin; carry = (cin & (a & b)) # ((a & b) & sin) # (cin & sin); END Department of Communication Engineering, NCTU 54 Hardware Project Unit 2 Review on Logic Elements Sau-Hsuan Wu MODULE mux4to1 TITLE '4 to 1 mux' "Inputs id15..id0 pin; s0,s1 pin; "Outputs y3..y0 pin istype 'com'; "Sets IND = [id15..id12]; INC = [id11..id8]; INB = [id7..id4]; INA = [id3..id0]; YSET = [y3..y0]; SEL = [s1,s0]; Equations YSET = IND & (SEL == 3) # INC & (SEL == 2) # INB & (SEL == 1) # INA & (SEL == 0); END Department of Communication Engineering, NCTU 55 Hardware Project Unit 2 Review on Logic Elements Sau-Hsuan Wu module sreg8w "Inputs d7..d0, clk, rst, load, l_r, si pin; "Outputs q7..q0 pin istype 'reg'; "Sets DATIN = [d7..d0]; "data input group LSHIFTD = [q6..q0,si]; "output data shifted left, with serial input RSHIFTD = [si,q7..q1]; "output data shifted right, with serial input DATOUT = [q7..q0]; "output data group "Intermediate equations LSHIFT = (l_r == 0); "SHIFT LEFT when s_l is low RSHIFT = (l_r == 1); "SHIFT RIGHT when s_l is high Equations DATOUT := DATIN & load "Load in value if LOAD mode. # LSHIFTD & LSHIFT "Shift data left if LSHIFT mode. # RSHIFTD & RSHIFT; "Shift data right if RSHIFT mode. DATOUT.clk = clk; DATOUT.ar = rst; End sreg8w Department of Communication Engineering, NCTU 56 Hardware Project Unit 2 Review on Logic Elements Sau-Hsuan Wu MODULE Counter TITLE '4 bit counter circuit' DECLARATIONS clk, !OE pin 1,13; "Clock input rst pin 14 ; "Asynchronous reset preset pin 23; "high value sets count = 1 ld pin 11; "high value sets count = input d3..d0 pin 7,8,9,10 ; "Counter inputs q3..q0 pin 18,17,16,15 istype 'reg'; "Counter outputs data= [d3..d0]; count = [q3..q0]; "Creating output bus EQUATIONS count.clk = clk; "Counter clock input count.ar = rst; "Counter reset input count.ld = preset; "Counter preset to ^h4 count.oe = OE; when ld then count := data; "count = data when ld high, synchrounous load else when !ld then count := count + 1; "Counting when ld low END Department of Communication Engineering, NCTU 57 Hardware Project Unit 2 Review on Logic Elements Sau-Hsuan Wu MODULE toplev TITLE '8 bit Johnson counter' "Performs an 8 bit Johnson or ring count synchronously. "Inputs CLK,SYSCLR,RUN pin; "Outputs Q7,Q6,Q5,Q4,Q3,Q2,Q1,Q0 pin istype 'reg_d,buffer'; "Sets count = [Q7,Q6,Q5,Q4,Q3,Q2,Q1,Q0]; "Counter set. prev = [Q6,Q5,Q4,Q3,Q2,Q1,Q0,!Q7]; "Counter set is fed from this set. "It is much easier to perform wide "operations such as counters or mathematical "functions by establishing signal sets. Equations count.d = prev.q & RUN "increment count if RUN # count.q & !RUN; "hold if not RUN count.clk = CLK; count.ar = SYSCLR; END Department of Communication Engineering, NCTU 58 Hardware Project Unit 2 Review on Logic Elements Sau-Hsuan Wu Bi-directional pin assignment Module biabel //ABEL Description of the Bidirectional Circuit //Input pins: ctrl pin; in1 pin; //Output pins: bidir1 pin; out1 pin; Equations bidir1.oe = ctrl; out1 = bidir1.pin; bidir1 = in1; end Department of Communication Engineering, NCTU 59