FM Transmitter

advertisement

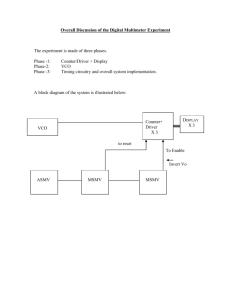

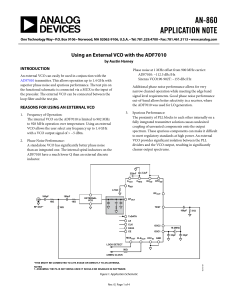

FM Transmitter FM Modulation using VCO fout i c c f mt t t t c f mt dt c SPM Ac cos c t c f mt dt [1] Vin c - Free Running Frequency of VCO Corresponding DC bias Cf - Gain of VCO Block Diagram Input DC Bias Vcc/2 VCO PA Chipset • 4046 Phase-Locked Loop • LM7171 Wide-Band Power Amplifier • 741 Op Amp 4046 PLL Only use the VCO 4046 VCO Characteristic C1>=100pF Schematic PCB Layout Considerations • The signal traces should be short and wide to lower the impedance. • The width of the signal traces has to satisfy current driving capacity. • Any used board area should be shorted to ground to reduce AC noise. • Sockets and pads will induce extra capacitance, so components should be directly soldered to board. • Surface mount components are preferred over discrete ones for less lead inductance. PCB Layout Measured Results • Carrier Frequency: 15MHz • Bandwidth: Controllable • Output Power: 500mW FM Receiver FM Demodulation using PLL [2] K p K v F s f i s K p K v F s 1 f K v Ve s Ve sK p F s s K v K p F s s i Cf mt in PFD LF i VCO Ve Loop Filter Design L 4 n n 2 n R2C 0.7 K p Kv N R1R2 C [3] VCO Design • VCO free running frequency = Carrier Frequency • VCO Frequency Range is no smaller than Bandwidth • Large VCO gain will increase PLL natural frequency n and thus improves PLL tracking capability Block Diagram BPF LNA PFD LF VCO Amp Chipset • 4046 PLL • CLC425 Wide-band LNA 4046 PLL Schematic PCB Layout Superheterodyne FM Receiver Block Diagram Input Matching Mixer IF Amp + IF Filter LO FM Demodulator Amp Chipset • TDA7000 – FM Radio • LM3875 – Audio Power Amplifier TDA7000 [4] IF Filter Quadrature Demodulator H s 1 R2 1 j R1 R2 C Vout fin IF Harmonic Distortion RF 75 kHz IF=70kHz 2IF IF IF IF IF 15kHz IF Distortion Suppression FLL Correlator To suppress interstation noise • Not Modulated • Lightly Modulated • Heavily Modulated Schematic PCB Layout Monolithic FSK Transmitter [5] Block Diagram PLL Reference Frequency Dual Modulus Prescaler Digital Input Analog Input A/D Converter Shift Register Clock Data Sampling Rate Output Inverter NAND – 2 Input NAND – 3 Input NAND – 4 Input NOR – 2 Input XOR Transmission Gate Edge-Triggered D Flip-Flop D Flip-Flop with ‘CLEAR’ Voltage Comparator 8-to-3 Encoder A/D Converter Parallel-Serial Shift Register Phase-Frequency Detector VCO Dual Modulus Prescaler [6] Output Driver To drive capacitive load with minimum delay A0 Wn ,W p A1 Wn ,Wp N ln AN 1 Wn ,W p CL Cin 1 N C A L Cin Capacitor Driving Capability CL=100p f=50MHz Synthesizer Synthesizer Response ADC and SR Response Chip Layout Digital Switching Noise [7] Noise Mechanism • Digital switching injects current into substrate through various kinds of capacitance, which propagates through the substrate and affects analog circuits. • Digital switching draws current from power supply rail with impedance and thus creates voltage drop on power supply rail. Digital Switching Noise in PLL • PLL is a typical mixed-signal integrated circuit PFD LF VCO Noise Coupling /N Simulation Results Error Voltage VCO output Noise Reducing Techniques • Use Differential Topology • Separate Power Supply Rails • Use guard rings • Multi-chip Module • Heterogeneous integration Test Structure 1 PFD LF VCO /N All building blocks share power supply rails Chip Layout 1 Test Structure 2 PFD LF VCO /N The counter uses separate power supply rails Chip Layout 2 Test Structure 3 PFD LF VCO /N • The counter uses separate power supply rails • The PFD and VCO are shielded and ring guarded Guard Ring p+ Sink the coupling P-type Substrate p+ On-Chip Shielding Metal 3 Via2 Via1 Contact Ohmic Contact ICs Radiation Chip Layout 3 Test Structure 4 PFD LF VCO /N • The counter uses separate power supply rails • Use guard rings around PFD and VCO • Implement LC VCO LC VCO Lower Phase Noise than Ring Oscillator Oscillator Basics • Positive feedback of 2n phase shift • Unity loop gain rp - Tank Loss 1 0 gm Q [8] LC 1 rp rp V1 g mV1 rp 0L • Phase noise is reverse proportional to Q L C Chip Layout Electromagnetic Coupling Microstrip Line Coupling 4 3 L W 1 S 2 [9] Electric Field Distribution Even Mode Odd Mode Impedance Matrix cot l j Z Z oe oo 2 cot l j Zoe Zoo 2 Z csc l j Z Z oe oo 2 csc l j Z oe Zoo 2 cot l 2 cot l j Zoe Z oo 2 csc l j Zoe Z oo 2 csc l j Z oe Z oo 2 j Zoe Zoo csc l 2 csc l j Z oe Zoo 2 cot l j Z oe Zoo 2 cot l j Z oe Z oo 2 j Zoe Z oo Zoe - even mode characteristic impedance Zoo - odd mode characteristic impedance - propagation constant 2 c2 csc l 2 csc l j Zoe Zoo 2 cot l j Zoe Zoo 2 cot l j Zoe Z oo 2 j Z oe Z oo Different Configurations Low Pass Band Pass Band Pass Band Pass Experiment Setup f 100MHz 2.9GHz P 0dBm Signal Generator Metal (Copper) Line 1 Coupling Metal (Copper) Line 2 FR-4 Substrate Ground Plane Spectrum Analyzer f ? P ? Results The coupling depends on L, W, S, and Integrated Inductor Coupling • Coupling between integrated spiral inductors • Coupling from spiral inductors to transistors [10] 2.5D Integrated Inductor [11] Interference Effects on PLL Performance [12] References 1. 2. 3. 4. 5. Jerry D. Gibson, Principles of Digital and Analog Communications Floyd M. Gardner, Phaselock Techniques Roland E. Best, Phase-Locked Loops – Theory, Design, and Applications W.H.A. Van Dooremolen and M. Hufschmidt, A complete FM radio on a chip R. Jacob Baker, Harry W. Li, David E. Boyce, CMOS Circuit Design, Layout, and Simulation 6. J. Navarro Soares and W.A.M. Van Noije, A 1.6-GHz Dual Modulus Prescaler Using the Extended True-Single-Phase-Clock CMOS Circuit Technique, IEEE Journal of SSCC, Vol.34, No.1, Jan 1999 7. Patrik Larsson, Measurements and Analysis of PLL Jitter Caused by Digital Switching Noise, IEEE Journal of SSCC, Vol.36, No.7, July 2001 8. Dan H. Wolaver, Phase-Locked Loop Circuit Design 9. E.M.T.Jones and J.T.Bolljahn, Coupled-Strip-Transmission-Line Filters and Directional Couplers, IRE Trans on Microwave Theory and Techniques, 1956 10. A.O.Adan, M.Fukumi, K.Higashi, T.Suyama, M.Miyamoto, M.Hayashi, Electromagnetic Coupling Effects in RFCOMS Circuits, 2002 IEEE MTT-S Digest 11. Jaime Aguilera and Joaquin De No, A Guide for On-Chip Inductor Design in a Conventional CMOS Process for RF Application 12. Murat F. Karsi, William C. Lindsey, Effects of CW Interference on Phase-Locked Loop Performance, IEEE Trans on Comm, Vol.48, No.5, May 2000