Overall Discussion of the Digital Multimeter Experiment

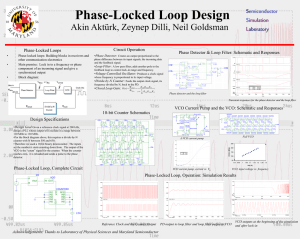

advertisement

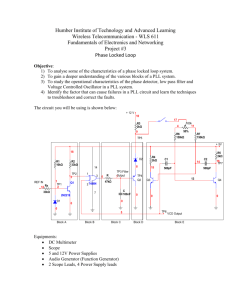

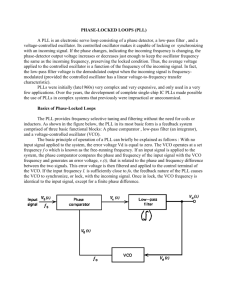

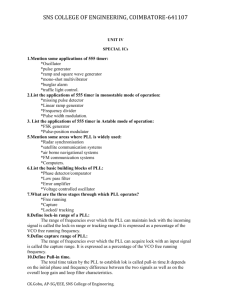

Overall Discussion of the Digital Multimeter Experiment The experiment is made of three phases. Phase -1: Phase-2: Phase -3: Counter/Driver + Display VCO Timing circuitry and overall system implementation. A block diagram of the system is illustrated below: Counter+ Driver X3 VCO DISPLAY X3 to reset To Enable Invert Vo ASMV MSMV MSMV Discussion: 123- Digital counter Voltage Controlled Oscillator Timing control circuitry A - 4026: Decade counter /divider with decoded 7-segement display output The first stage that was constructed in the lab consists of a three stage synchronous decade counter with a 7-segment LED display. The 4026 decade counter with a decoded output was used. The decoded output drives a 7-segment CC LED display. The display counts the input pulses available at pin no. 1 of the 4026. The count advances on every positive edge transition of the clock input. The count continues until the reset (at pin no. 11) is set high. The completion of this stage is necessary for the final stage of the digital Multimeter. Refer to the datasheet on this IC on the courses web page. Also, for your report, verify that the output of each stage is a 10 (i.e., the input frequency to stage 2 is 1/10th the input frequency to the first stage, and so on ..) Also, refer to the timing chart in the datasheet. B- 4046: Phase Lock Loop In this experiment, only the VCO portion of the PLL is used. However, for the general benefit, the PLL is discussed briefly in this handout. Background Information: A PLL is basically a closed loop frequency control system. A phase locked loop is a controlled oscillator whose instantaneous frequency is dynamically adjusted through multiplicative feedback and low pass filtering. The simplified PLL configuration that will be used for analysis purposes is shown in Figure 1 below. There are three fundamental component blocks: the voltagecontrolled oscillator (VCO), the phase detector (PD), and the loop filter with amplifier (G(s)). A PLL has many applications in communications (FM and FSK modulation/demodulation), frequency synthesis, frequency synchronization and control, and tone detection. Refer to this site for graphical illustrations: http://www.hep.ph.ic.ac.uk/~hallg/Instrumentation/Lectures/Phasesensitivedetection. pdf#search=%22PLL%20applications%22 VCO The VCO is an oscillator whose instantaneous frequency o (t ) is controlled by the control voltage v c (t ) as follows: o (t) c K c vc (t) (1) The waveform produced by the VCO can be a square wave, a sine wave, or one of many other periodic signals. The constant c is called the center frequency of the VCO. Note from (1) that this is simply to free running frequency of the VCO when the control voltage v c is zero. The constant K c is the VCO gain. It is a measure of the sensitivity of the VCO frequency to variations in the control voltage. The VCO center frequency can be tuned through the selection of the external discrete components R and C . PD The phase detector (PD) is a two input/ one output circuit having the following property. If the two inputs are periodic and have the same period, then the DC component of the PD output should be approximately proportional to the phase angle between the two periodic inputs. A four quadrant analog multiplier functions as the PD. Indeed, if the input v i is a sine wave and the VCO output v o is any periodic waveform, then: x DC K d sin( i o ) (2) Here x DC denotes the average value or DC component of the PD output, x (t ) . Similarly, i and o represent the input signal vi (t ) and VCO output signal v o (t ) respectively. Finally, the "constant" K d is called the PD gain. When the phase angle between the inputs is small, x dc is a linear function of the phase angle since sin( i o ) is approximately equal to ( i o ) under these conditions. Loop Filter The loop filter (including the amplifier) is the third fundamental component of the PLL. The filter is usually realized with external discrete components. In this way, the PLL circuit can be tuned. The loop filter is typically a passive low pass filter such as an RC lag filter. The function of the loop filter is to extract the DC component of the PD output. Since the PD is a mixer, it's output will typically be periodic, and will contain frequencies corresponding to the sums and differences of the frequencies present in vi (t ) and v o (t ) . When the circuit is in phase lock, the input frequency f i equals the output frequency f o . The filter output voltage is constant. If the input frequency increases slightly, the phase angle difference i o will increase with time. Thus, from eq (2), the dc output of the phase detector will increase, and then the dc output of the filter will increase. This will cause an increase to the input of the VCO, therefore increasing the VCO output frequency and bringing it up to meet the input frequency. The phase angle stabilizes at a new equilibrium, and phase lock is maintained. The new value of i o yields larger constant output from the phase detector, which in turn drives the VCO at a higher frequency (further from the center frequency). A similar adjustment takes place when the input frequency is slightly below the VCO frequency. In phase lock, this control circuit (PD, amplifier, and filter) is continuously adjusting the VCO frequency to equal the input frequency. The ability to maintain phase lock is governed by Eq. 2. To maintain stability, the VCO frequency must increase when i o increases. From Eq. 2, however, this will happen only when i o is less than 90 o . (or 90 o ). By monitoring the control voltage fed back to the VCO, we can exploit this servo-mechanism feature to demodulate FM signals. PLL in Frequency synthesis: A simple frequency synthesizer is shown below The error is reduced to zero only when the output frequency is equal to N times the input frequency., Thus, by varying N, different output frequencies are obtained. PLL’s Three Modes of Operation a. Tracking – free running b. Capture c. Lock In case (a), the input frequency and the VCO’s frequency are too far apart. The VCO is consequently oscillating at an almost random frequency – free running. The VCO continues to track the input frequency – if the input frequency is within a capture range, the VCO tracks the input until a lock is achieved. Here, fin = fvco. Once a lock is achieved, the VCO can track the input to a wider range – lock range. http://www.uoguelph.ca/~antoon/gadgets/pll/pll.html 2- The 4046 PLL is low power, linear VCO. a. Lecture notes on the 4046 operation b. Refer to data sheet c. The experiment 3- Timing and relationship to the system a. Lecture notes