Question 2

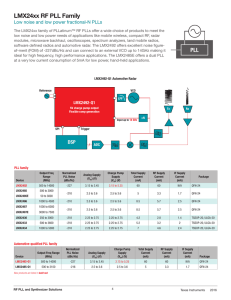

advertisement

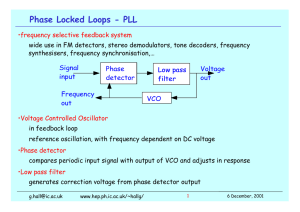

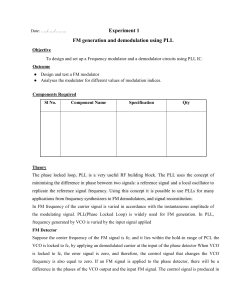

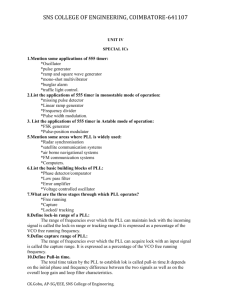

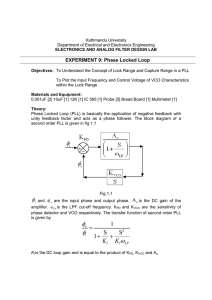

ECE Department Electronics Lab ECE371 Student ID محمد محمود احمد عبد المتعال محمد مرسي عبد العظيم مرسي محمد مصطفى حسين الغوري محمد وائل جمال عيسى عايش 33563/33564/33565/33566 Experiment # E10 Experiment Name Introduction to PLLs Student Name Date Attended Shift 2 Grader Signature Accuracy: Neatness: Results analysis: Total Grade: Simulations and measurements performed accurately and fully. Lab testing procedures followed. Graphs and tables presented in a neat and readable shape. Graphs are interpretable and units of each quantity are clearly written. Axes are clearly labeled (quantity and unit) Results discussed and observations made. Comparison between measured and simulated results is outlined. In case of falsified or copied results, the grade is set to ZERO while informing the lab supervisor to take a disciplinary action 10 10 10 1 30 EXPERIMENT E-X Phase Locked Loop Question 1: Write down a summary of PLL experiment theory in the area below: (Don’t copy and paste from the internet or the experiments notes itself) PLL theory PLL is a system that generates a signal that has a frequency equal to the i/p one ; when the phase difference between the i/p & o/p signals is const then they have the same freq, as -phase = integration freq - in other words simply the PLL generates an o/p signal whose phase tracks the i/p '' PASHE LOCKED LOOP '' It`s a negative feedback system much similar to the ''buffer'' circuit , the circuit consists of three main blocks phase detector, LPF and VCO . *The PD can be implemented simply using XOR gate as when the i/p signal & the feedback are not the same then the output is 1 & equals zero if the two inputs are the same. When the phase difference between the inputs increases, the width of the output pulses increases linearly then the average value of the output increases linearly. *The output is then passed through a LPF to take the required average value. As it only passes the DC component which is the required average value and filters the other harmonics. *The VCO: It generates an output signal whose 2 frequency is proportional to the input voltage, and continues the loop. Question 2: Insert the required plots in the specified spaces: a) Orcad Schematics b) VCO response (Output frequency VS Vctrl) c) The PLL output signal when Vctrl = 1 V (VS time) 3 4 Question 3: Insert the required plots in the specified spaces: a) PLL Orcad schematics b) Inputs of the phase-frequency detector at input frequency = 1 KHz c) Minimum and Maximum Frequencies Fmin = ………500 Hz……, corresponding control voltage = …0.54V………. Fmax= ……4 KHz…... corresponding control voltage = …4.7V……….. 5 Minimum Frequency Graph Maximum Frequency Graph 6 Question 4 (Bonus): Insert the required plots in the specified spaces: a) PLL Orcad schematics (with divider) b) Inputs of the phase-frequency detector at input frequency = 1 KHz 7 c) Input and Output of the PLL (on the same graph) d) Minimum and Maximum Frequencies (input) Fmin = …………… , corresponding control voltage = …………. Fmax= …………….., corresponding control voltage = ………….. 8