Combinational & Sequential Logic Circuits - digitalelectronics-cm

advertisement

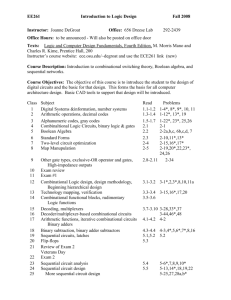

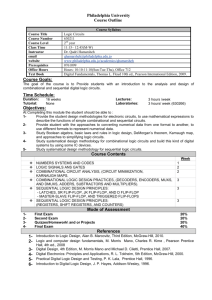

Digital Electronics Module 3 Combinational and Sequential Logic Circuits PREPARED BY Academic Services Unit January 2012 © Applied Technology High Schools, 2012 1 Module 3: Combinational and Sequential Logic Circuits Combinational and Sequential Logic Circuits Module Objectives Upon successful completion of this module, students should be able to: Describe the operation of the XOR, XNOR gates. Describe the operation of the clocked and un-clocked SR-Latch. Describe the operation of the D and JK Flip Flops. Distinguish between combinational logic and sequential logic. Use of sequential logic in simple applications. Module Contents: # 2 Topic Page No. 1. Introduction to Combinational logic 03 2. The Exclusive-OR (XOR) 04 3. The Exclusive-NOR (XNOR) 05 4. Lab Activity#3 07 5. Lab Activity#4 10 6. Sequential Logic 12 7. Latches and Flip-Flops 12 8. The NOR Gate S-R Latch 13 9. Level Triggered Latch 16 10. Level Triggered D-Type latch 18 11. Edge-Triggered Flip Flop 20 12. Lab Activity#1 (XOR) 22 13. Lab Activity#2 (XNOR) 23 14. Lab Activity#5 (Clocked SR-Latch) 25 15. Lab Activity#6 (JK-Flip Flop) 29 Module 3: Combinational and Sequential Logic Circuits 1. INTRODUCTION Combinational logic: When logic gates (such as AND, OR and NOT) are connected together to produce a specified output for certain specified combinations of input variables, with no storage involved, the resulting network is called combinational logic. Definition The combinational logic can be defined as “is that logic in which all outputs are directly related to the current combination of values on its inputs”. Combinational logic is probably the easiest circuitry to design. The outputs from a combinational logic circuit depend only on the current inputs. Much of logic design involves connecting simple combinational logic circuits to construct a larger circuit that performs a much more complicated function. Simple and often-used combinational logic circuits are XOR and XNOR. 1.1 The Exclusive-OR and Exclusive-NOR gates These two gates are actually formed by a combination of other gates already discussed. Because of their fundamental importance in many applications, these gates are treated as basic gates with their own unique symbols. 3 Module 3: Combinational and Sequential Logic Circuits 2 The Exclusive-OR (XOR) 2.1 The XOR Logic Circuit and Symbol Referring to logic circuit in Figure 1, you can see how an XOR gate is made up of the combination of AND, OR, and NOT gates. The standard symbol for the XOR gate is shown in Figure 2. Note that XOR gate has only two inputs, it never has more than two inputs. A Y1 AND-1 NOT A OR X X XOR B NOT AND-2 B Y2 Figure 2 XOR logic symbol Figure 1 XOR logic Circuit 2.2 XOR Logical Operation and Truth Table The logical operation of XOR is such that the output is high only when the two inputs are at opposite levels. The operation of XOR with two inputs A and B and output X is stated as follows: If A is LOW and B is HIGH, OR if A is HIGH and B is LOW, then X is HIGH If A and B are both HIGH or both LOW, then X is LOW The truth table illustrates this operation is Table 1. INPUTS A B X 0 0 0 0 1 1 1 0 1 1 1 0 Table 1 Truth table for XOR gate 2.3 XOR Logical Function The two variables expression “X = A B” is called the Logical XOR Function. Referring to logic circuit in Figure 1, XOR function can be illustrated as follows: The inputs to the AND-1 are A and B ; then Y1 A B . The inputs to the AND-2 are A and B ; then Y2 A B . 4 OUTPUT Module 3: Combinational and Sequential Logic Circuits Continue (XOR Logical Function) The inputs to the OR are Y1and Y2 ; then X Y1 Y2 . Hence X = A B = ( A B ) + ( A B ) and it mean the following: If (A and B) are at opposite levels; then X is high. Otherwise X is Low. Conduct Lab Activity #1 on page 22. 3. The Exclusive-NOR (XNOR) 3.1 The XNOR Logic Circuit Referring to logic circuit in Figure 3; you can see how an XNOR gate is made up of the combination of AND, OR, and NOT gates. A Y1 AND NOT Z OR NOT X NOT AND B Y2 Figure 3 XOR logic Circuit 3.2 The XNOR Symbol Standard symbol for the Exclusive-NOR (XNOR) gate is shown in Figure 4. The XNOR gate has only two inputs. The bubble on the output indicates that its output is opposite that of XOR gate. 5 A XNOR X B Figure 4 XNOR logic symbol Module 3: Combinational and Sequential Logic Circuits 3.3 XNOR Logical Operation and Truth Table The logical operation of XNOR is such that when the two inputs are opposite the output is LOW. The operation of XNOR with two inputs A and B and output X can be stated as follows: If A is LOW and B is HIGH, OR if A is HIGH and B is LOW, then X is LOW If A and B are both HIGH or both LOW, then X is HIGH The truth table illustrates this operation is Table 2. INPUTS OUTPUT A B X 0 0 1 0 1 0 1 0 0 1 1 1 Table 2 Truth table for XNOR gate 3.4 XNOR Logical Function The expression X A B is called the Logical XNOR Function. Referring to logic circuit in Figure 3, XNOR function can be illustrated as follows: The output of the XOR part is Z = A B. But the output of XNOR part is X Z . Then the output of XNOR can be written as X A B and it means: If A and B both are High or both Low, then X is High. Otherwise X is Low. Applications: Google to find at least 2-applications for each gate. XOR XNOR a) ………………………………………………… a) ………………………………………………… b) ………………………………………………… b) ………………………………………………… c) ………………………………………………… c) ………………………………………………… Conduct Lab Activity #2 on page 23. 6 Module 3: Combinational and Sequential Logic Circuits Practical 4. Lab Activity#3: Central Heating Pump OBJECTIVES: To understand the operation of general combinational logic circuits. EQUIPMENT LT345: Logic Tutor Power supply unit (5V @ 50mA) CIRCUIT DIAGRAM +5VDC 0VDC S1 Q ON OFF AND ON OFF NOT S2 Figure 5 general combinational logic circuits Before you start identify the following parts a) Identify the switches located at the bottom of LT345 Kit. b) Identify LED’s located at the top of LT345 Kit c) Identify the +5V and 0V socket located at the top of LT345 Kit PROCEDURE 1) To clearly understand the connections shown in the patching diagram of Figure 6, the circuit is redrawn in Figure 5. 2) Make the connections as shown in the patching diagram of Figure 6. 3) Connect the power supply to the +5V and 0V sockets. 4) Don’t switch ON the power supply till the instructor check you circuit. 5) Connect each of S1 and S2 to one switch. Then, connect Q to one LED. 7 Module 3: Combinational and Sequential Logic Circuits PATCHING DIAGRAM Figure 6 Patching Diagram (combinational logic circuits) OBSERVATIONS Set both switches to the values indicated in Table3 and record the state of Q (LED). Switches Output S1 S2 OFF OFF OFF ON ON OFF ON ON Q (LED) Table 3 Q State Apply this Experimental circuit to an actual life application by: Assuming the following: S1 represents the Heating Switch (Heating SW) S2 represents the Temperature Sensor (Temp Sen.) Q represents the Pump Explain the operation of the implemented circuits using the following words: COLD 8 ON HOT OFF Pump Temperature (Sensor) Heating Switch Module 3: Combinational and Sequential Logic Circuits Step#1 Put the operation in a truth table (Table 4) Switches The inputs are: Heating Switch Temp Sensor Output Pump The Temp. Sensor. The ON/OFF Switch of the Heating system. The Output of the system is the Pump Table 4 System Operation Step#2 Explain the operation ........................................................................................................ ........................................................................................................ ........................................................................................................ ........................................................................................................ ........................................................................................................ ........................................................................................................ ........................................................................................................ Implement the Logic circuit which can perform this operation 9 Module 3: Combinational and Sequential Logic Circuits Practical 5. Lab Activity#4: Multiplexer Circuit OBJECTIVES: To understand the operation of the Multiplexer Circuit. EQUIPMENT LT345: Logic Tutor Power supply unit (5V @ 50mA) +5VDC 0VDC ON OFF S NOT ON OFF NOT Q AND G1 A OR ON OFF B AND G2 Figure 7 Multiplexer logic circuits Before you start identify the following parts a) Identify the switches located at the bottom of LT345 Kit. b) Identify LED’s located at the top of LT345 Kit c) Identify the +5V and 0V socket located at the top of LT345 Kit PROCEDURE 1) To clearly understand the connections shown in the patching diagram of Figure 8, the circuit is redrawn in Figure 7. 2) Make the connections as shown in the patching diagram of Figure 8. 3) Connect the power supply to the +5V and 0V sockets. 4) Don’t switch ON the power supply till the instructor check you circuit. 5) Connect each of S, A, B to one switch. Then, connect Q to one LED. 10 Module 3: Combinational and Sequential Logic Circuits PATCHING DIAGRAM Figure 8 Patching Diagram (Multiplexer logic circuits) OBSERVATIONS Set all switches (S, A, and B) to the values indicated in the truth table and record the state of Q (LED) in Table 5. Inputs Switches S A B OFF OFF OFF OFF OFF ON OFF ON OFF OFF ON ON ON OFF OFF ON OFF ON ON ON OFF ON ON ON Output Q (LED) Table 5 Q State ASSIGNMENT a) Define the term Multiplexer. b) Write the logic functions of the two AND-gates (G1 and G2) c) If we send the input S direct to (G1), does the result remains same? d) Write the logic functions of the second NOT gate in term of S. 11 Module 3: Combinational and Sequential Logic Circuits 6. Sequential Logic A digital logic function made of basic logic gates (AND, OR, NOT, etc.) in which the output values depend not only on the values currently being presented to its inputs, but also on previous input values. 6.1 Definition Briefly the sequential logic can be defined as “is that logic in which the output depends on a sequence of its input values”. 7 Latches and Flip-Flops In this part of the module we will examine two types of sequential logic circuits: the Latches and the Flip-Flops. Latches and Flip-Flops are bistable elements having two stable states. Because of their storing ability, they are useful as basic building block for registers and memories. It is a bistable element that can have its output latched 1) Latches HIGH (Set) or LOW (Reset), hence the name S-R Latch. It is a synchronous bistable device that can have its output 2) Flip-Flops changes state only on the clock edge. Main difference between Latches and Flip-Flops Latch: It is active when clock either at logic high level or at low level. Flip-Flop: It is active only on the clock edges. Example of Latches Example of Flip-Flops 1) SR Latch 1) JK flip-flops 2) Clocked SR Latch 2) T-type flip-flops 3) D Latch 3) Edge triggered D-FF 12 Module 3: Combinational and Sequential Logic Circuits 8. The NOR Gate S-R Latch The most basic memory element is the S-R LATCH. The S-R latch has two main inputs: the Set (S) and the REST (R), and two outputs Q and Q . It has Two-inputs R and S, and two-outputs Q and Q 8.1 The S-R Latch Logic Circuit and Symbol Figure 9 shows how SR latch is formed with two cross-coupled NOR-gates. R, Q , and Q are the inputs and the output of gate G1. S, Q, and Q are the inputs and the output of gate G2. These arrangements must preserve, otherwise the Set and Reset will have the opposite meaning. The symbol of the NOR-Gate S-R latch is shown in Figure 10. R S NOR G1 Q S NOR G2 Q R Figure 9 S-R Latch logic Circuit Q Q Figure 10 Latch logic symbol 8.2 SR latch Logical Operation Referring to Figure 9, initially assume that both inputs R and S and output Q are LOW [i.e. R = S = 0 and Q = 0] Now G2 inputs are G = 0 and S = 0, therefore G2 output is Q = 1. G1 inputs are Q = 1 and R = 0, therefore G1 output is Q = 0. Change S to HIGH G2 inputs become Q = 0 and S = 1, therefore G2 output is Q = 0. Now G1 inputs will change to Q = 0 and R = 0, therefore G1 output will change to Q = 1 the latch is in the Set state. Solve Exercise 1 to find out the other inputs combinations and their corresponding outputs states. 13 Module 3: Combinational and Sequential Logic Circuits Important Note Note that the inputs condition (S = R = 1) is not allowed, because it generates unpredictable output state and it is called invalid condition. Exercise #1 Change S back to LOW and follow the same process given above to determine the states of the outputs Q an Q . Change R to HIGH and follow the same process to determine the states of the outputs Q and Q . 8.3 NOR Gate S-R Latch Truth Table If the input S is ON and the R is OFF, the output (Q) will be set to ON. If the input S is OFF and the R is ON, the output (Q) will be set to OFF. If both the inputs S and R are OFF, the output (Q) will remain the same as its previous value. If both the inputs S and R are ON, the output state is unpredictable. The truth table of S-R latch which illustrates this operation is Table 6. Inputs Outputs Operation R S Q Q 0 0 Q Q No Change (same as previous) 0 1 1 0 The output Set to ON 1 0 0 1 The output Reset to OFF 1 1 Invalid condition unpredictable output state Table 6 Truth table for S-R Latch Terminology used Terms Meanings No change Latch remains in previous state (store the previous output. Latch Set The output (Q) Set to ON (i.e. Q = 1). Latch Reset The output (Q) Reset to OFF (i.e. Q = 0). Invalid Simultaneous High’s on both inputs (i.e. R = S =1) not Condition allowed. It generates unpredictable output state. 14 Module 3: Combinational and Sequential Logic Circuits Solution to Exercise #1 the latch is in the Set state, therefore G1 output is Q = 1 Changing S back to LOW G2 inputs become Q = 1 and S = 0, therefore G2 output is Q = 0. Now G1 inputs is Q = 0 and R = 0 G1 output remain unchanged in the Set state Q = 1. Remember G2 output is Q = 0, changing R to HIGH G1 inputs become Q = 0 and R = 1, therefore G1 output is Q = 0 the latch is in the Reset state. Notes: ……………………………………………………………………………………..……….. ……………………………………………………………………………………..……….. ……………………………………………………………………………………..……….. ……………………………………………………………………………………..……….. ……………………………………………………………………………………..……….. ……………………………………………………………………………………..……….. ……………………………………………………………………………………..……….. ……………………………………………………………………………………..……….. ……………………………………………………………………………………..……….. ……………………………………………………………………………………..……….. ……………………………………………………………………………………..……….. ……………………………………………………………………………………..……….. ……………………………………………………………………………………..……….. 15 Module 3: Combinational and Sequential Logic Circuits 9. Level Triggered Latches To have control over the Latch’s operation, a clock signal is applied to decide when a latch is enabled or disabled and when the output changes its state. The clock signal ensures that the device is triggered into operation at the right time and is denoted with C Clock Signal or EN Enable Signal. Definition The Level Triggered latch can be defined as “a logic device that changes its output state in response to a HIGH or LOW level of the clock”; and hence the name Level Triggered latch”. 9.1 Level Triggered S-R Latch The operation of Level Triggered SR latch is the same as SR Latch except that its output state changes only when the clock level is HIGH. 9.2 Level Triggered SR latch Logic Symbol Figure 11 shows the logic symbol of level-triggered SR latch. The logic circuit for a level-triggered S-R latch is shown in Figure 12. CK This logic circuit illustrates how S-R Q R latch is modified to add the clock input (CK). Q S Figure 11 Level Triggered SR latch logic symbol 9.3 Level Triggered SR latch Logic Circuit R AND NOR Q NOR Q CK S AND Figure 12 Level Triggered SR latch logic Circuit 16 Module 3: Combinational and Sequential Logic Circuits 9.4 Level Triggered SR latch operation and Truth Table Referring to the logic circuit in Figure 12, you can see that the inputs to the latch (S and R) are only enabled when the clock signal (CK) is HIGH. This can be realized as follows: When the level of the clock signal is HIGH (logic-1), the two-AND gates passes the (S and R) inputs through to the latch and the device is enabled. When the level of the clock signal is LOW (logic-0), the two-AND gates blocks the (S and R) inputs from reaching the latch and the device is disabled. The when CK is HIGH, the circuit operation is identical to that of the SR latch. The truth table illustrates this operation is shown in Table 7. Latch Outputs Q Comments CK R S Inputs 0 0 0 0 0 0 0 1 0 0 As long as the clock level CK is 0 1 0 0 0 0 1 1 0 0 NO Change AND Inputs 1 0 0 0 0 Q No Change (same as previous) 1 0 1 0 1 1 The output Set to ON 1 1 0 1 0 0 The output Reset to OFF 1 1 1 1 1 Invalid unpredictable output state LOW the output remain same as previous (No Change will occur). Table 7 Truth table for Level Triggered SR Latch Notes: ……………………………………………………………………………………..……….. ……………………………………………………………………………………..……….. Conduct Lab Activity #5 on page 25. 17 Module 3: Combinational and Sequential Logic Circuits 10. Level Triggered D-type Latch The D-type latch is basically a S-R latch with small circuit modification. This modification was introduced to ensure that the S and R inputs are never HIGH or LOW at the same time. So D-latch is used to eliminate the undesirable invalid state occurs in the S-R latch. Definition The D-type latch is a Data-type circuit that can latch (store) a binary 1 or 0. 10.1 D-type Latch Logic Circuit and Symbol The basic D-type latch logic circuit is shown in Figure 14. It has only two Q D inputs: D Data-input and CK Clockinput. The NOT gate ensure that the CK C inputs to the AND gates are at opposite Q level and consequently the inputs S and R to the latch are at opposite level. The logic symbol for the D-type latch is Figure 13 Level Triggered D-type shown in Figure 13. latch logic symbol 10.2 Level Triggered D-Type latch Logic Circuit D R NOT AND CK AND NOR Q NOR Q S Figure 14 Level Triggered D-Type latch logic Circuit 18 Module 3: Combinational and Sequential Logic Circuits 10.3 Level Triggered D-Type latch operation and Truth Table Referring to the logic circuit in Figure 14, the operation of D-type Latch can be explained as follows: As long as the clock level is Low, the AND gates outputs S and R are also Low. With low level S and R, the output Q remains unchanged. When the CK is High, the input S follows D and the input R follows D . Therefore with CK = High, when D is High the latch will Set and when D is Low the latch will Reset. This can be stated another way, the output Q follows the input D when CK is High (D = 1 the latch Set, D = 0 the latch Reset). The truth table illustrates this operation is shown in Table 8. AND Inputs Latch Inputs Outputs Comments CK D R S Q 0 0 0 0 NO 0 1 0 0 1 0 1 0 0 The output Reset to OFF 1 1 0 1 1 The output Set to ON Change As long as the CK is LOW, the output remains same as previous. Table 8 Truth table for Level Triggered D Latch Notes: ……………………………………………………………………………………..……….. ……………………………………………………………………………………..……….. ……………………………………………………………………………………..……….. ……………………………………………………………………………………..……….. 19 Module 3: Combinational and Sequential Logic Circuits 11. Edge-Triggered Flip Flop Edge-Triggered Flip Flop is a type of flip-flop in which the data are entered and appear on the output on the same clock edge. They are of two types: a) Positive Edge-Triggered JK-FF b) Negative Edge-Triggered JKFF In this type the FF responses to the In this type the FF responses to the Positive Edge of the clock Negative Edge of the clock Negative Edge of the clock Positive Edge of the clock 11.1 Edge-Triggered J-K Flip Flop The J-K flip-flop is the most widely used type of flip-flop. The operation of JK-FF is identical to that of the S-R flip-flop in the SET, RESET, and NOChange conditions. The difference is that the JK-FF has no Invalid State. 11.2 Edge-Triggered JK-FF Symbol Figure 15 shows a basic positive Edge- Q J Triggered JK-FF. It differ from the S-R flip-flop in that the Q output is connected back to the CK input of G1, and the Q output is connected back to the input of G2. J and K are the two C Q K control inputs. The logic symbol for EdgeFigure 16 Edge-Triggered JK-FF logic symbol Triggered JK-FF is shown in Figure 16. 11.3 Edge-Triggered JK-FF Logic Circuit AND G1 K R NOR Q NOR Q CK J AND G2 S Figure 15 Level Triggered D-Type latch logic Circuit 20 Module 3: Combinational and Sequential Logic Circuits 11.4 Edge-Triggered JK-FF Truth Table If CK is LOW, no matter what (J or K) are the output remains the same. If both J and K are LOW, no matter CK is the output remains the same. On the positive edge if J is HIGH and K is LOW, the flip-flop will SET. On the positive edge if J is LOW and K is HIGH, the flip-flop will RESET. If both J and K are HIGH, the flip-flop will Toggle on each clock pulse. The truth table illustrates this operation is shown in Table 9. Inputs Outputs Comments J K CK Q X X 0 Q No Change (same as previous) 0 0 Q No Change (same as previous) 0 1 0 The Flip-Flop RESET 1 0 1 The Flip-Flop SET 1 1 Q The Flip-Flop Toggle Table 9 Truth table of JK Flip Flop Terminology used Terms Meanings The action of a flip-flop when it changes state on each clock pulse. Toggle (The output switches back and forth between OFF and ON) Conduct Lab Activity #6 on page 29. 21 Module 3: Combinational and Sequential Logic Circuits 12. Lab Activity #1: OBJECTIVES: REQUIREMENTS To verify the truth table of XOR-gate using Design PC or Laptop Soft\Tina. TINA Software PROCEDURE d) Open Tina. e) Click “Gates Tab”. Drag (2-AND’s, 2-NOT’s, 1-OR, & 2-Pull down resistors) to the Edit-area. f) Click “Basic Tab”. Drag 4-GND, 1-Battery, & 2-Switches to the Edit-area. g) Now arrange and connect the parts as shown in Figure-17 below. h) Click to ON the “Interactive mode-tab” to start the simulation. i) Change the switches A and B (ON/OFF) to form the combination given in Table 10 and note the corresponding output states (X). Circuit Diagram: XOR-gate using TINA Figure 17 XOR Logic Circuit 22 Module 3: Combinational and Sequential Logic Circuits OBSERVATIONS For each switching combination of A and B note the Switches corresponding output state of (X) in Table 10. VERIFICATION: Compare Table 10 with the truth table of XOR gate (Table 1) and note your remarks below. ………………………………………………………………………………… ………………………………………………………………………………… ………………………………………………………………………………… A B OFF OFF OFF ON ON OFF ON ON Output X Table 10 Output State 13. Lab Activity #2: OBJECTIVES: REQUIREMENTS To verify the truth table of XNOR gate using Design PC or Laptop Soft\Tina. TINA Software PROCEDURE a) In the existing circuit of Figure 17; remove the wire connecting the ORgate with Light1 (X). Connect NOT-gate between them as in Figure 18. b) The new construction forms an XNOR logic circuit. c) Repeat steps (e & f) to confirm the action of XNOR-gate by verifying its truth table. Note your observations in Table 11. OBSERVATIONS: Note the output state of (X) for Switches A B VERIFICATION: OFF OFF Compare Table 11 with the truth table of XNOR gate OFF ON (Table 2) and note your remarks below. ON OFF ………………………………………………………………………………… ON ON each combination of A and B in Table 11. ………………………………………………………………………………… 23 Output X Table 11 Output State Module 3: Combinational and Sequential Logic Circuits Circuit Diagram: XNOR-gate using TINA Figure 18 XNOR Logic Circuit Notes: ………………………………………………………………………………………..……….. ………………………………………………………………………………………..……….. ………………………………………………………………………………………..……….. ………………………………………………………………………………………..……….. ………………………………………………………………………………………..……….. ………………………………………………………………………………………..……….. ………………………………………………………………………………………..……….. ………………………………………………………………………………………..……….. ………………………………………………………………………………………..……….. ………………………………………………………………………………………..……….. 24 Module 3: Combinational and Sequential Logic Circuits 14. Lab Activity #5: Note: The students should try to complete all the 4-tasks (under this Labactivity) in a block and not to carry some part to the next day or week. OBJECTIVES: REQUIREMENTS To understand the operation of clocked SR-Latches Logic Tutor LT345 and to verify their truth tables. Power Supply 5V Circuit Diagram: Figure 19 clocked SR-Latch Circuit PROCEDURE: Task-I a) Don’t switch ON the power unless the instructor check you circuit. b) Connect the supply leads (Black) and (Red) to 0V and +5V sockets of the LT-board. c) Now make the connections in accordance to the circuit of Figure 19 and the Patching Diagram of Figure 20 below. d) Set S and R initially to '0' and switch on power. Switch ON the power to the LT345. The numeric indicator should indicate '0'. e) The output of the push-button S6 goes to '1' every time the button is pressed. f) Operate the push-button S6 once after each change of R and S. g) Proceed now by setting the dip switches R and S to the values shown in Table 12. Observe the resulting value of Q before and after each step. 25 Module 3: Combinational and Sequential Logic Circuits PATCHING DIAGRAM Figure 20 clocked SR-Latch Circuit OBSERVATIONS Copy and complete the table shown. The sequence is made to ensure that Inputs Switches S6 S R 1 OFF OFF 2 ON OFF 3 ON OFF 4 OFF OFF 5 OFF ON Note: Qn and Qn+1 represent the 6 OFF ON values of Q before and after the 7 OFF ON every possible progression is tested. Set the switches (S and R) OFF. Press S6 once, this represent (stste-1). Set the S ON and R OFF. Press S6 once, this represent (stste-2). Fill in these values in the blank positions of the table. Output Qn clock signal; take note of the moment where the change in Q occurs. 26 Table 12 Q State Module 3: Combinational and Sequential Logic Circuits Qn+1 PROCEDURE: Task-II When you have completed Table 12 of Task-I, study the results for the pairs of rows (1, 4), (5, 6), and (2, 3). Use the same rows order (1, 4), (5, 6), Inputs Switches S6 S R 1, 4 OFF OFF 5, 6 OFF ON 2, 3 ON OFF 7 ON ON and (2, 3) to complete Table 13. Output Qn+1 Table 13 Q State PROCEDURE: Task-III Redraw the circuit of Figure 19 and mark in the logic states at all inputs and outputs when the clock is at '1' and S and R = 01, 10, and 11 in turn. S6 S R 1 0 1 1 1 0 1 1 1 G4 G15 G13 (Q) G6 G18 Task-IV: Circuit Diagram Figure 21 clocked D-Flip Flop 27 Module 3: Combinational and Sequential Logic Circuits G14 ( Q ) PROCEDURE: Task-IV a) Construct the circuit of Figure 21 by adding NOT- Inputs Output gate (G22) to the existing circuit of Figure 20. D Qn+1 b) Alter D (between 0 & 1) and operate the pushbutton alternately to complete Table 14. c) Confirm the action of the clocked D-Flip Flop by verifying it is truth table. 0 1 Table 14 Q State Notes: ………………………………………………………………………………………..……….. ………………………………………………………………………………………..……….. ………………………………………………………………………………………..……….. ………………………………………………………………………………………..……….. ………………………………………………………………………………………..……….. ………………………………………………………………………………………..……….. ………………………………………………………………………………………..……….. ………………………………………………………………………………………..……….. ………………………………………………………………………………………..……….. ………………………………………………………………………………………..……….. ………………………………………………………………………………………..……….. ………………………………………………………………………………………..……….. ………………………………………………………………………………………..……….. ………………………………………………………………………………………..……….. ………………………………………………………………………………………..……….. ………………………………………………………………………………………..……….. 28 Module 3: Combinational and Sequential Logic Circuits 15. Lab Activity #6: OBJECTIVES: REQUIREMENTS To understand the operation of clocked JK-Flip- PC or Laptop Flops and to verify their truth tables. TINA Software PROCEDURE: Task-I a) Make the connections in accordance to the circuit of Figure 22 and the Patching Diagram of Figure 23 as follow. b) Connect FF1 to the four slide switches (S1, S2, S3, & S4). Connect the pushbutton S6 to the CLK input of the JK-FF. Then connect the output Q to the LED LP1. c) For the moment set both P and C to binary '1'. d) Switch ON the power and set the clock pulse high. Copy the truth table (Table 15) and complete it by applying inputs in the sequence shown. e) Operate the clock pulse switch once after each new setting. f) Record the state of Q (Qn before the clock pulse) and (Qn+1 after the clock pulse) in each case. Circuit Diagram and Truth Table: Figure 22 Circuit Diagram JK-FF CLK J K 1 1 0 2 0 0 3 1 1 4 0 0 5 1 1 6 1 0 7 0 1 8 0 1 Qn Qn+1 Table 15 Truth Table JK-FF 29 Module 3: Combinational and Sequential Logic Circuits PATCHING DIAGRAM Figure 23 JK-Flip Flop Procedure: Task-II When you have completed your table Inputs Switches S6 S R (2, 4) 0 0 (7, 8) 0 1 and (3, 5) in this order, and complete (1, 6) 1 0 the abbreviated table (Table 16). (3, 5) 1 1 (ignoring row 1), collect the results of the pairs of rows (2, 4), (7, 8), (1, 6) Output Qn+1 Table 16 Abbreviated Table Observation: Compare Table 16 with the table for the clocked SR flip-flop from the Simple Latch and the Clocked Flip-flops. Remarks: ………………………………………………………………………………….. ………………………………………………………………………………………………... 30 Module 3: Combinational and Sequential Logic Circuits PROCEDURE: Task-III a) Change the connections to J and K as shown in Figure 24. b) Switch S2 alternately to '0' and '1'. This Set J to 0 and K to 1 alternately. c) Confirm that the behavior of the circuit of Figure 24 is same as that of a D-type flip-flop. Figure 24 JK as D Flip-Flop Questions: Among your group discuss and answer the following questions. 1) What difference do you notice between the tables for the clocked SR and the JK flip-flops? …………………………………………………………………………………………... …………………………………………………………………………………………... 2) At which edge of the clock-pulse does the output change occur? a) the '0' to '1' (leading edge) or at; b) the '1' to '0' (trailing edge) …………………………………………………………………………………………... …………………………………………………………………………………………... 3) If you maintain the clock at '1' whilst altering J and K to some setting different from the one they had when the clock was changed to '1', does the output change too? …………………………………………………………………………………………... …………………………………………………………………………………………... 31 Module 3: Combinational and Sequential Logic Circuits