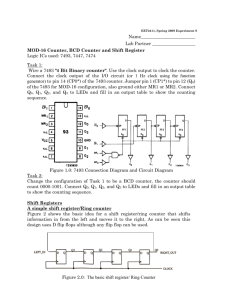

Lab5_SequentialLogicCircuits

advertisement

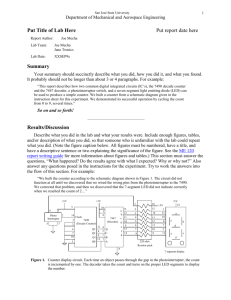

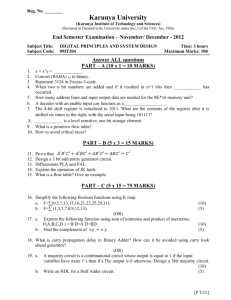

Algonquin College Of Applied Arts and Technology ELE8930 Lab 5 Sequential Logic Circuits Part 1: The RS Flip Flop Objectives: i. ii. iii. To wire and observe the operation of an RS flip flop. To wire and observe the operation of a clocked RS flip flop. To study how flip flops are used as a units of memory. Equipment: 7400 2-input NAND gate IC 555 Timer circuit from lab 1 Procedure: 1. Complete the wiring diagram of schematic 1 for the RS flip flop shown in the figure 1. Use two 2-input NAND gates. figure 1 Sw-1 S Q S FF R Q R Sw-2 Q __ Q Schematic 1 1 Algonquin College Of Applied Arts and Technology 2. With the power off, construct the circuit from step 1. Use two output LED indicator lights with resistors. 3. Turn power ON. Operate the input switches to the positions shown in the input section of Table 2. Using table 1 as a reference, observe and record the output of each circuit in the output part of table 2. 4. In the right column of table 2 write the name of the condition of the outputs. Use the terms hold, set, or reset. Table 1: Truth Table for a RS Flip Flop Mode of Operation INPUTS OUTPUTS S R Q __ Q Prohibited 0 0 1 1 Prohibited - Do not use Set 0 1 1 0 For setting Q to 1 Reset 1 0 0 1 For setting Q to 0 Q __ Q Hold 1 1 Effect on Output Q Depends on previous state TABLE #2 INPUTS 5. S R 0 0 0 1 1 0 1 1 0 1 1 1 1 0 OUTPUTS Q __ Q Mode of Operation (Prohibited, Set, Reset, Hold) Proceed to part 8 and leave this part of your lab assemble. 2 Algonquin College Of Applied Arts and Technology 6. Complete the wiring diagram of schematic 2 for the RS flip flop shown in the figure 2. Use four 2-input NAND gates. Figure 2 Sw-3 S Q CLK CLK FF R Sw-4 Q 9. With the power off, construct the circuit from step 6. Wire the input switches to R and S and the single pulse clock input CLK from the 555 timer circuit. Use two output LED indicator lights with resistors. 10. Turn power ON. Operate the input switches to the positions shown in the input section of Table 4. Using table 3 as an reference, observe and record the output of each circuit in the output part of table 4.. 11. In the right column of table 4 write the name of the condition of the outputs. 3 Algonquin College Of Applied Arts and Technology TABLE 3 - Truth Table for a Clocked R-S Flip Flop INPUTS Mode of Operation OUTPUTS Q __ Q S R Effect on output Q Hold 0 0 Reset 0 1 0 1 Reset or cleared to 0 Set 1 0 1 0 Set to 1 Prohibited 1 1 1 1 Prohibited-do not use No Change No Change TABLE 4 INPUTS OUTPUTS CLK S R ↑ 1 0 ↑ 0 0 ↑ 0 1 ↑ 0 0 ↑ 1 0 ↑ 1 1 ↑ 1 0 ↑ 0 1 ↑ 0 0 ↑ 1 0 Q __ Q Mode of Operation 12. Move the clock input to one of the logic switches and repeat the steps in the table above. 13. Show the instructor your results. INSTRUCTORS INITIALS:________ 4 Algonquin College Of Applied Arts and Technology Part 2 - The D Flip Flop Objective: To operate and test D flip flops using a 7474 IC. Material: 7474 D-type flip flop IC 555 Timer circuit from lab `1 Procedure: 1. Insert the 7474 IC into the mounting board. 2. Refer to figure 3 and the pin-out for the 7474. Wire D, CLR, and PS to switches and CLK to the output of the 555 timer circuit. Wire Q & Q NOT to LEDs. Figure 3 7474 D-type Flop Flop pin-out CLR-Sw-2 Sw-3 Q D FF (7474) CLK Q PS-Sw-1 4. Turn power ON, using table 5 as an reference, fill in table 6. In the right-hand column of Table 2, write the mode of Operation. 5 Algonquin College Of Applied Arts and Technology TABLE 5 - Truth table for a D Flip Flop INPUTS Asynchronous Mode of Operation Synchronous OUTPUTS PS CLR CLK D Q __ Q Asynchronous Set (PS) 0 1 X X 1 0 Asynchronous Reset (CLR) 1 0 X X 0 1 Prohibited 0 0 X X 1 1 Set 1 1 ↑ 1 1 0 Reset 1 1 ↑ 0 0 1 X = Irrelevant, ↑ = Low to High Transition of Clock Pulse TABLE 6 INPUTS Asynchronous 5. OUTPUTS Synchronous PS CLR CLK D 0 1 X X 1 0 X X 0 0 X X 1 1 ↑ 1 1 1 ↑ 0 1 1 ↑ 1 1 0 ↑ 1 1 1 ↑ 1 1 1 ↑ 0 0 1 ↑ 0 __ Q Mode of Operation Move the clock input to one of the switches and repeat the steps in the table above. Next slowly pulse the D flip-flop (start at 0, then 1, and then 0). Can you determine if the flip-flop is positive or negative edge-triggered? Circle the correct answer → 6. Q Show the instructor your results. Positive or Negative INSTRUCTORS INITIALS:________ 6 Algonquin College Of Applied Arts and Technology Part 3 - The JK Flip-Flop Objective: To operate and test JK flip flops using a 7476 IC. Material: 7476 JK flip flop IC 555 Timer Circuit Procedure: 1. Refer to the figure 4 and the pin-out diagram for the 7476 dual JK flip flop. Wire J, K, CLR, and PS to switches and CLK to the output of the 555 timer circuit. Wire Q & Q NOT to LEDs. Figure 4 7476 JK flip flop CLR-Sw-2 Sw-3 J CLK CLK (7476) Sw-4 K Q Q PS-Sw-1 4. Turn power ON, using table 7 as a reference, fill in table 8. In the right-hand column of Table 8, write the mode of operation. 5. Move the clock input to one of the switches and repeat the steps in the table above. 6. Show the instructor your results. INSTRUCTORS INITIALS:________ 7 Algonquin College Of Applied Arts and Technology Table 7 - Truth Table for a JK flip flop INPUTS Mode of Operation Asynchronous OUTPUTS Synchronous PS CLR CLK J K Q __ Q Asynchronous Set (PS) 0 1 X X X 1 0 Asynchronous Reset (CLR) 1 0 X X X 0 1 Prohibited 0 0 X X X 1 1 Hold 1 1 ↓ 0 0 No Change Reset 1 1 ↓ 0 1 0 1 Set 1 1 ↓ 1 0 1 0 Toggle 1 1 ↓ 1 1 Opposite State X = Irrelevant, ↓= High to Low to Transition of Clock Pulse TABLE 8 INPUTS Asynchronous OUTPUTS Synchronous PS CLR CLK J K 0 1 X X X 1 0 X X X 0 0 X X X 0 1 X X X 1 1 ↓ 0 0 1 1 ↓ 0 1 1 1 ↓ 1 0 1 1 ↓ 1 1 1 1 ↓ 1 1 1 1 ↓ 1 1 1 1 ↓ 1 1 Q _ Q Mode of Operation Prohibited PS, CLR, Hold, Reset, Set, Toggle 8 Algonquin College Of Applied Arts and Technology *Part 4: Ripple Counters Objectrive: i. To wire, and test a 4-bit ripple up counter using JK flip flops. ii. To design, wire and test a module-10 ripple counter with digital readout. MATERIAL 7400 2-Input NAND Gate IC Seven-Segment LED Display 7 - 150 Ω, 1/4-W Resistors 2 - 7476 dual J-K Flip-Flop ICs 7447 BCD-to-Seven-Segment Decoder/Driver IC 555 Timer Circuit *SYSTEM DIAGRAM: This lab has three circuits that you will partially design, construct, and test in this experiment. You must design and draw in detail the counters. You will use flip flops when designing these counters. The counter in the third circuit will require a NAND gate. PROCEDURE: To L1 Figure 5 Qd Clock Input 4-Bit Ripple UP Counter D L2 C L3 B L4 A Qc Qb Qa 1. Design a 4-bit, Mod 16, ripple up counter as shown in figure 5 above. Use four JK flip-flops and four output LED indicator lights with resistors. 4-bit Mod 16 ripple UP counter using JK flip flops: 9 Algonquin College Of Applied Arts and Technology 2. Connect power (Vcc) and GND to each 7476 IC. For proper operation connect the following pins to Vcc, J, K, PR, and CLR. 4. Wire the circuit you drew in step 1. Connect CLK input to a single pulse clock. Wire the 7476 ICs and the four output LED indicator lights with resistors. 5. Turn power ON. Operate the 4-bit counter. Observe and record the results in the 4-bit ripple up counter column, Table 9. TABLE 9 INPUT Pulse Number 0 OUTPUTS 4-Bit Ripple UP Counter 4-Bit Ripple DOWN Counter D C B A D C B A 0 0 0 0 1 1 1 1 Decade Counter with Digital Readout 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 6. Show the instructor your results. INSTRUCTORS INITIALS:________ 10 Algonquin College Of Applied Arts and Technology Figure 6 Qd Preset Clock Input 7. 4-Bit Ripple DOWN Counter D C B A Qc Qb Qa Design a 4-bit ripple DOWN counter shown in the figure above. Notice the addition of a PS input for setting the output of the counter to 1111. 4-bit Mod 16 ripple DOWN counter using JK flip flops: 8. Turn power Off. Rewire the 7476 J-K flip-flops to get the down counter you drew in step 7. 9. Turn power ON. Preset (PS to 0 and then back to 1) the outputs to 1111. 10. Operate the down counter by pulsing the CLK input. Observe and record the results in the 4bit ripple down counter column, Table 1. 11. Show the instructor your results. INSTRUCTORS INITIALS:________ 11 Algonquin College Of Applied Arts and Technology Figure 7 Digital Readout Clock Input Qd Module 10 Ripple UP Counter Qc Qb Qa “8” “4” “2” “1” 7447 Decoder a b c d e f g a b c d e f g a f g e b c d 150 + 5 V (Common Anode) 12. Design a module-10 ripple UP counter as shown in figure 7 above. Use four JK flip-flops (7476 IC and one 2-input NAND gate (7400 IC). Module-10 ripple UP counter 13. Construct the counter. Insert the 7447 IC and the seven-segment LED display closely together on the mounting board. Wire the input CLK, the two 7476 ICs, and the 7400 IC. Wire the counter outputs (QD, QC, QB, QA) to the inputs of the 7447 decoder (D, C, B, A). Connect seven 150 Ω limiting resistors between the 7447 decoder and the seven-segment LED display. 12 Algonquin College Of Applied Arts and Technology 14. With the power OFF, connect power (Vcc) and GND to the 7447 IC. Connect +5 V (Vcc) only to the seven-segment LED display. 15. Turn power ON. Operate the module-10 counter by pulsing the input. Observe and record the results in the decade counter with digital readout column, Table 1. 19. Show the instructor your results. INSTRUCTORS INITIALS:________ Part 5 - IC Counters Objecives: To wire and test a up and down counter using a 74192 IC. Material 74192 up/down counter IC SYSTEM DIAGRAM: The 74192 Up/Down Decade Counter is a synchronous decade (base-10) counter that counts in either direction. For normal up-counting sequence, “Load” should be high, and “Clear” should be low. When upcounting, hold the “Down-Count” input high. When down-counting, hold the “Up-Count” input high. Vcc +5 v Figure 8 Clock Pulse 5 Vcc 11 GND 14 16 7 6 74192 Vcc 4 2 3 Qd Binary LED Readout D B C A Qc Qb Qa 8 Decoder GND “8” “4” “2” “1” 7447 Digital Readout a b c d e f g a b c d e f g a f g e b c d 150 + 5 V (Common Anode) 13 Algonquin College Of Applied Arts and Technology Procedure: 1. Insert the 74192 into the proto board and wire up the counter as shown in figure 8 on the previous page. 2. Turn power ON and observe the counter sequence. The 74192 should count from 0 to 9. 3. Show the instructor your results. 4. Rewire the 74192 (See system diagram) for down-counting sequence. The 74192 should now count downward from 9 to 0. 5. Show the instructor your results. INSTRUCTORS INITIALS:__________ INSTRUCTORS INITIALS:__________ 14