E906_Latch_Mannual

advertisement

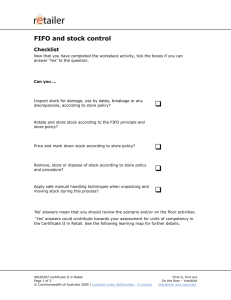

E906 VME FEE Board version 2 Target detector: Hodoscope PCB S/N: 1527-8340 Firmware Rev 1030 This Programmer’s Reference Guide provides general programming information, including memory maps and register data for the E906 VME FEE Board. Please note that this reference guide is limited to a specific firmware version. Please confirm the contents of PCB serial number (CSR [31-16]) and Revision date code (CSR [15-0]) before using this guide. General description: A shift register with a depth of 64 clocks is implemented in the second version of Latch card. Edge-sampling of input signal is done with a 125-MHz internal clock. Upon the receipt of an external trigger into the front panel, the latched signal within a gated window stored in the shift register, is copied from the register of FPGA to the FIFO (a dual-port memory), to be read out. The location of the window in the shift register, corresponding to the delay time of the trigger with respect to the expected signal, and the width of window, accommodating the time jitter of signals in all 64 channels, can be adjusted by the values set in the CSR2 register. A “trigger-enable” command has to be issued from Single-Board-Computer (SBC) in order to make the module be ready to process an external trigger. On the other hand, a “trigger-disable” command will turn the module inactive to any trigger sent. Any modification of CSR and readout of data from FIFO has to be done in the mode of “trigger-disabled”. The BUSY output from the front panel, in the level of TTL, can be used for the DAQ control. The BUSY becomes “OFF” (or cleared) when the “trigger-enable” mode is set for the module by SBC. Upon receipt of a trigger, a 64-bit data will be copied from the register to the FIFO. During this stage of “Copy In Progress” (CIP), the BUSY will be “ON” temporarily for less than 200 ns. After issuing “trigger-disable” for ending the data-taking, the BUSY will return back to “ON”. Key Features VME A32 D32/BLT32 64-bit ECL or LVDS differential inputs 64 clocks shift register 125-MHz internal clock for sampling. 64*16K FIFO 3 user ECL output bits 2 user ECL input bits Two NIM inputs NIM Busy output +5V, -12V power supply Figure 1-1. E906 VME FEE Board Table 1-1. Address Map Offset Access Data width Description 0x000 R/W D32 Control and Status Register (CSR) 0x004 R D32 PCB serial number and Revision date code 0x008 R D32 FIFO status register 0x00C R/W D32 Control and Status Register (CSR2) 0x010 W D32 FIFO test mode enable 0x014 W D32 FIFO test mode disable 0x020 W D32 Clear 0x028 W D32 trigger enable 0x02C W D32 trigger disable 0x050 W D32 Reserved 0x054 W D32 Reserved 0x060 W D32 Reset 0x068 0x100 | 0x1FC W D32 Generate output pulse R/W, BLT D32 128KB FIFO memory space, (32K x 32) Latch signal This card is using Common-Stop Mode to latch 64-bit-ECL-data. Common-Stop Mode Timing Edge-sampling of input signal is done with an 125-MHz (8 ns)internal clock. A shift register with a depth of 64 clocks is implemented in the second version of Latch card. Upon the receipt of an external trigger into the front panel, the latched signal within a gated window stored in the shift register is copied from the register to the dual-port memory, to be read out. The gated window is base on the setting of CSR2(13-8) and CSR2(5-0). Using CSR2(13-8), one can trace the ECL data in the selected 6 events in the pass 64 events. The Edge-Trigger by internal clock An edge-trigger is signaled by a voltage level high-to-low transition, a falling edge on the Internal Clock input. When a negative-going occurs on the NIM-Latch signal, 64-bit ECL data inputs will be stored. Internal Clock ECL Data Input Tsu Th Tsu : Setup time : 2nS (MIN) Th : Hold time : 2nS (MIN) The truth table below summarizes the operations of the edge-triggered latch. Inputs Data to be stored Data [63 : 0] Latch 0 ↓ 0 1 ↓ 1 Relative registers: CSR [12], 0x000; Latch_Mode_Enable, 0x028; Latch_Mode_Disable, 0x02C. Data reading VME controller may read the data that just latch-and-stored after entering the trigger-disabled mode. Control and Status Register REG Bit Control and Status Register, offset + 0x000 31~16 15~13 12 11~10 9 8 7~6 5~4 3~1 0 R R 0 0 X R/W R/W R/W X CLR Reset User_LED R ECL_output_1~3 ECL_input_1~2 R FIFO_status FIFO_test_mode R/W Capture_mode R RSVD Latch_mode_SEL R (edge-trigger mode=1) RSVD Access Project _Code Field X X 0 X 00 000 0 Control and Status Register 2 14 RSVD Range of adjustable Access TTL clock latched Field 13~8 R R R/W 5~0 R R/W X CLR Reset 7~6 Combination of six clock windows for OR operation 15 delay (unit of clock) Bit Control and Status Register 2, offset + 0x00C RSVD REG X X 0 X 00 000 0 PCB serial number and Revision date code REG PCB number and Revision date code Register, offset + 0x004 31~16 Bit 15~8 7~0 PCB_MFG_S/N Data_code, (year) Data_code, (week) Field Access R CLR X Reset X FIFO status register Control and Status Register, FIFO_status_mode = “00”, coarse scale mode. 27~8 3~0 Read_index R Access CLR 7~4 FIFO_usage Field 31~28 Header_byte Bit FIFO status register, offset + 0x008 RSVD REG 0000 X 0 Reset Control and Status Register, FIFO_status_mode = “01”, fine scale mode. Reset 15~0 R Access CLR 27~16 Read_index Field 31~28 Header_byte Bit FIFO status register, offset + 0x008 RSVD REG 0001 X 0 Control and Status Register, FIFO_status_mode = “10”, fine scale mode. 27~16 R Access CLR 15~0 RSVD Field 31~28 Header_byte Bit FIFO status register, offset + 0x008 FIFO_usage REG 0010 X 0 Reset Control and Status Register, FIFO_status_mode = “11”. Display the maximum memory capacity. 27~15 R Access CLR 14~0 Capacity Field 31~28 Header_byte Bit FIFO status register, offset + 0x008 RSVD REG 0011 Reset X 0 LED Lights on the Front Panel: Red_L: Trigger Enabled Red_R: Reset Yellow_L: Read FIFO Yellow_R: Power ON Green1_L: Trigger received Green1_R: Power ON Green2_L: User defined Green2_R: Power ON LEMO Connector: Top: Trigger IN (NIM). Middle: Undefined. Bottom: BUSY OUT (TTL) Example code of DAQ operation (example code: ********************* please post the operation example code on the Wiki page and include the link here****************) - Write ‘X’ Offset + 0x00C. Set up the user-defined delay range and combination of OR-windows in CSR2. This action has to be done when trigger is disabled. - Write ‘X’ Offset + 0x028. Trigger enabled. LED Red_L should be on. Whenever there is a trigger received, the OR results of signals in the specified clock windows will be written into FIFO. In this step, TTL-Busy of the bottom of the front panel is from Low level (0mV) change to (3.3V). After about 144 ns, NIM-Busy will return to the low level when the write to FIFO is finished. Every time when Latch card get a trigger, will take 2 memory space (2*32 bit). Write ‘X’ Offset + 0x02C. Trigger disabled. Write ‘X’ Offset + 0x000. Set proper FIFO status mode. Read Offset + 0x008. Access information of number of events in FIFO. Read Offset + 0x100. Read Data. Data access 或 Block transfer (BLT). Example code of determing the appropriate delay time and width of gateing window. (example code: ********************* please post the operation example code and the instruction of usage on the Wiki page. Include the link here****************)