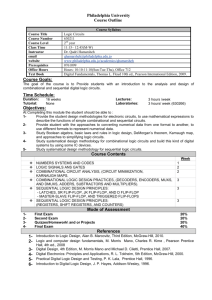

Course outline

advertisement

Course Outline SUBJECT: Digital Circuits I (AEEE 203) LECTURER (Group 1): Dr. Konstantinos Tatas LECTURER (Group 2): Dr. Symeon (Simos) Nikolaou LECTURER (Group 3): Dr. Alexis Polykarpou PREREQUISITES: None NUMBER OF ECTS: 7 HOURS/WEEK: 3+1 SEMESTER: Fall 2007 TEACHING AREA: Classroom and Laboratory CONTACT INFORMATION EMAIL: com.tk@fit.ac.cy, eng.ns@fit.ac.cy, WEBSITE: http://staff.fit.ac.cy/com.tk OFFICE HOURS: Dr. Konstantinos Tatas: Mon : 13 :00 – 16 :00, Tu : 13 :00 – 16 :00 Dr. Symeon Nikolaou: Mon: 10:50-12:50, 15:00:17:00 Tu: 10:30-11:30 Wed: 15:00-17:00 (Subject to change) AIMS AND OBJECTIVES The aims of the course are: To provide a thorough introduction to digital concepts necessary to give the student the ability to understand the world of digital electronics. To state the importance of digital electronics today. To teach students some basic design techniques of combinational logic circuits. Design on sequential synchronous and asynchronous logic circuits SCHEDULE ANALYSIS Week 1: Introductory digital concepts. Analog and digital signals and systems. Introduction to digital systems – Introduction to computer numbering systems: Binary number representation. Week 2: Conversion from representation. decimal to any base and from any base to decimal. BCD Week 3: Fractional and negative number representation: Sign-magnitude, one’s and two’s complement representation. Addition and subtraction using radix complement. Excess and floating-point number representations. Digital codes. Homework 1. Week 4: Combinational circuits. Basic digital components (logic gates), truth tables and logic functions Week 5: 1 Karnaugh maps and algorithmic minimization techniques. Circuit implementation of logic functions. Week 6: Combinational circuit design methodology. Week 7: Mid-term exam Implementations of combinational circuits using only NAND/NOR gates. Week 8: Design of combinational MSI digital circuits adders/subtracters, multiplexers, comparators etc. such as decoders, encoders, Week 9: Sequential circuits: Latches and Set/Reset, Data, JK and Toggle flip-flops. Week 10: Positive and negative edge triggered flip flops. Asynchronous flip-flop inputs. Homework 2. Week 11: Asynchronous counters, synchronous counters and shift registers. Week 12: Introduction to VHDL and computer programs to design and simulate digital circuits. Week 13: Revision METHODOLOGY Teaching is based on lectures and laboratory experiments. The lectures involve the delivery of new material, discussion and example exercises on relevant material. There will be three lecture hours per week and one hour devoted to laboratory exercises during which students will have the chance to put in practice the theoretical principles presented in class. GRADING POLICY Final Exam: 60% Coursework: 40% Test: 15% : To be given on the second week of November Lab: 15% (Best 5 out of 6 will be considered) Assignment 1: 5% Assignment 2: 5% COURSEWORK One test and two assignments will be given during the semester. NOTE The instructor retains the right to adjust the schedule of lectures or tests according to class’ progress or to any effecting external factor. Prior notice will be provided. 2 MAIN TEXTBOOK Mano M M Cileti M D, Digital Design, Fourth Edition, Prentice Hall.,2004 REFERENCES Mano M M, Kime C R, Logic and Computer Design Fundamentals, Third Edition, Prentice Hall.,2004 Sandige R, Digital Design Essentials, Prentice Hall, 2002 Wakerly J, Digital Design Principles and Practices, Fourth Edition, Prentice Hall, 2006 Bartelt T, Digital Electronics-An Integrated Laboratory Approach, Prentice Hall, 2002 OTHER POLICIES Class Attendance: Students are expected to attend classes regularly so that new material can be delivered to all students without delays. On time arrival will be appreciated. Cell phones: All cell phones must be switched to silent mode before entering the class. 3