digital_systems

advertisement

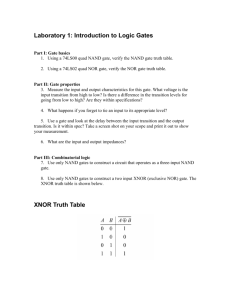

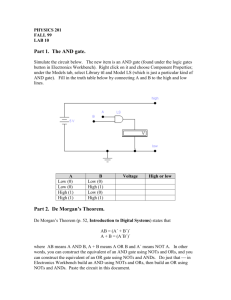

SATHYABAMA UNIVERSITY DEPARTMENT OF EIE SECX1002 - DIGITAL SYSTEMS QUESTION BANK UNIT I Part A 1. Convert gray code 1101 to binary code. 2. Represent the numbers (a) –35 (b) 145 in 2’s complement form. 3. Convert (226)8 = ( )10 = ( )2. 4. Convert the following hexadecimal numbers to decimal (a) AC3 (b) AF8. 5. Perform the arithmetic operation 258 + 754 in Binary 6. Define Demargan’s law. 7. Name any two non – weighted 4 bit binary code. 8. State Consensus theorem. 9. Obtain the truth table of the function F = xy + x’y’ + y’z 10. Express the following switching circuits in binary logic notation. Part B 1. Explain in detail about number systems 2. Simplify the following Boolean equations a) AB + ABC + AB ( D+E ) b) XY + XYZ +XYZ’+X’YZ c) A’B’C’ +A’BC’ +A’BC d) A’BCD’ + BCD’ + BC’D’ + BC’D e) AC + C (A + A’B) 3. Simplify the following Boolean equations and realize using gates a)Y = (AB + C + D) ( C’+ D) (C’ +D +E) b)A = x’y’z + x’ y z + xy’ 4. Perform the following conversions a) (673.124)8 = ( )2 b) (110101)2 = ( )8 c) (1110011)2 = ( )8 d) 49 into Excess-3 and Gray. e) (367)8 = ( )10 f) Convert (5A9.B4)H = ( )2 5. Perform the following Arithmetic operations a) Add (1010001)2 and (0011110)2 ,then converted into Hexadecimal b) Add 4FB ,75D, A12 and C39 c) Subtract the following binary numbers using 2’s compliment addition i. (10111010 - 10010111) ii.(010011011- 101111010) 6. Prove the following using Boolean algebra a) A+ A’B +AB’ = A+B b)AB+ A’B+A’B’ =A’+B UNIT II Part A 1. Minimize the four variable logic function using k-map. f(A,B,C,D) = m (0,1,2,3,,8,9,10,11) Implement AND & OR gate using NOR gate 2. What is standard SOP and Standard POS? 3. Realize f = A’B + AB’ using minimum universal gates. 4. Draw the Timing diagram of 2 input NAND gate 5. What is meant by min and Max terms? 6. Draw the Timing diagram of 2 input NOR gate 7. Show the Boolean function AB’+A’B+AB on a three variable Karnaugh map. 8. Mention the advantages of Karnaugh map 9. Implement f = abcd using two input NAND Gate. 10. Implement f = a + b + c + d using two input NOR Gate. Part B 1. Simplify and draw the circuit for the following function using K-map Y= π M ( 0, 6, 7, 8, 12, 13, 14, 15) 2. Implement the following function using K-map Y= Σ m(0, 1, 2, 3, 4,7,9,10) 3. Simplify the Boolean function using tabulation method F( A,B,C,D) = Σ m (0,2,3,6,7,8,10,12,13) 4. Implement the following functions using NAND-NAND Logic a)Y=AC + ABC + A’BC + AB + D b)F(A, B, C)= Σ m(0,1,3,5) 5. Implement the following functions using NOR - NOR Logic a)Y=AC + BC + AB + D b)F(A, B, C)= M (0,2,4,5,6) 6. Minimize the following expression using K-map a)Y=A’BC’D’+ A’BC’D +ABC’D’ + ABC’D + AB’C’D + A’B’CD’ b)Y= Σ m(2,14,10,11,8,12,3,0) UNIT III Part A 1. Draw a full adder circuit. 2. Mention the types of adders. 3. Draw Adder/Subtractor circuit 4. How a demultiplier can be converted into a decoder? 5. Compare Encoder and decoder. 6. What is meant by a magnitude comparator? 7. What is demultiplexer.? 8. What is meant by comparator? 9. Define Priority Encoder. 10. Draw a 4 to 1 MUX circuit. Part B 1. Explain in detail about half & full Adder, Design a full-Adder using Half-Adder 2. Explain in detail about Binary Parallel adder/ subtractor 3. Draw and explain the circuit for decimal to BCD encoder and BCD to decimal decoder 4. Explain in detail about MUX and Demux 5. Implement the following Boolean function using 4:1 and 8:1 MUX , F(A,B,C)=∑m (1,3,5,6) 6. Design a 2 bit comparator using gates for the given condition A>B, A=B, A<B UNIT IV Part A 1. Distinguish Combinational logic and Sequential logic 2. Define lockout condition. 3. What is the drawback of SR Flipflop? How is it minimized? 4. Write the excitation table of JK Flip Flop. 5. What are the different types of shift registers? 6. Write down the design steps of synchronous counters. 7. How do you carryout state minimization? 8. Draw the logic diagram of a master – slave D-flip flop using NAND gate. 9. What do you mean by critical and Non-critical races? How can they be avoided? 10. Build a D flip-flop from SR flip-flop IC. Part B 1. Draw and explain the 4-bit binary UP-DOWN counter using J-K Flip-flop 2. Explain SISO, SIPO 4-bit shift register with neat diagram 3. Design a MOD-10 counter and explain 4. Design a counter for following sequence using J.K Flip-flop 001,101,100,000,011 5. Draw the logic circuit for 4 stage register with parallel transfer of input data and shift right output data using D-FlipFlop and explain the operation 6. Explain the operation of D flipflop,T flipflop and Master/Slave flip-flop with logic diagram UNIT V Part A 1. What is meant by the term edge triggering? 2. Distinguish ECL logic with TTL logic? 3. What are the universal gates, why they are called so? 4. List the merits of RTL logic family 5. What is tristate logic? 6. List any three advantages of CMOS logic 7. Compare two main features of TTL and CMOS logic gates. 8. down fan in and fan out of a standard TTL IC. 9. Give four advantages of TTL. 10. Define Noise margin. Part B 1. Explain about TTL IC logic family with suitable diagram 2. Draw & explain about the CMOS NAND gate & HTL NAND gate 3. Compare the characteristics of TTL,ECL & MOS IC logic families 4. Classify & explain any two logic IC families with neat sketch 5. Explain the characteristics of logic families. 6. Explain the TTL NOR gate with neat diagram