Unit 1 Notes

advertisement

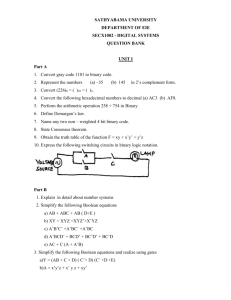

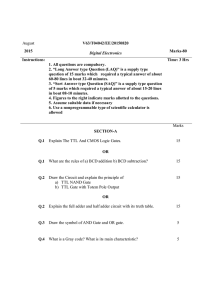

Number System and Logic Families 1. Introduction to digital Electronics & Boolean algebra: Logic Gate Truth Tables As well as a standard Boolean Expression, the input and output information of any Logic Gate or circuit can be plotted into a standard table to give a visual representation of the switching function of the system. The table used to represent the boolean expression of a logic gate function is commonly called a Truth Table. A logic gate truth table shows each possible input combination to the gate or circuit with the resultant output depending upon the combination of these input(s). For example, consider a single 2-input logic circuit with input variables labelled as A and B. There are “four” possible input combinations or 22 of “OFF” and “ON” for the two inputs. However, when dealing with Boolean expressions and especially logic gate truth tables, we do not general use “ON” or “OFF” but instead give them bit values which represent a logic level “1” or a logic level “0” respectively. Then the four possible combinations of A and B for a 2-input logic gate is given as: Input Combination 1. – “OFF” – “OFF” or ( 0, 0 ) Input Combination 2. – “OFF” – “ON” or ( 0, 1 ) Input Combination 3. – “ON” – “OFF” or ( 1, 0 ) Input Combination 4. – “ON” – “ON” or ( 1, 1 ) Therefore, a 3-input logic circuit would have 8 possible input combinations or 2 3 and a 4-input logic circuit would have 16 or 24, and so on as the number of inputs increases. Then a logic circuit with“n” number of inputs would have 2n possible input combinations of both “OFF” and “ON”. 1 Number System and Logic Families So in order to keep things simple to understand, in this tutorial we will only deal with standard 2-input type logic gates, but the principals are still the same for gates with more than two inputs. Then the Truth tables for a 2-input AND Gate, a 2-input OR Gate and a single input NOT Gate are given as: 2-input AND Gate For a 2-input AND gate, the output Q is true if BOTH input A “AND” input B are both true, giving the Boolean Expression of: ( Q = A and B ). Symbol Boolean Expression Q = A.B Truth Table A B Q 0 0 0 0 1 0 1 0 0 1 1 1 Read as A AND B gives Q Note that the Boolean Expression for a two input AND gate can be written as: A.B or just simply ABwithout the decimal point. 2-input OR (Inclusive OR) Gate For a 2-input OR gate, the output Q is true if EITHER input A “OR” input B is true, giving the Boolean Expression of: ( Q = A or B ). 2 Number System and Logic Families Symbol Boolean Expression Q = A+B Truth Table A B Q 0 0 0 0 1 1 1 0 1 1 1 1 Read as A OR B gives Q NOT Gate For a single input NOT gate, the output Q is ONLY true when the input is “NOT” true, the output is the inverse or complement of the input giving the Boolean Expression of: ( Q = NOT A ). Symbol Truth Table A Q 0 1 1 0 Boolean Expression Q = NOT A or A Read as inversion of A gives Q The NAND and the NOR Gates are a combination of the AND and OR Gates with that of a NOT Gate or inverter. 2-input NAND (Not AND) Gate 3 Number System and Logic Families For a 2-input NAND gate, the output Q is true if BOTH input A and input B are NOT true, giving the Boolean Expression of: ( Q = not(A and B) ). Symbol Boolean Expression Q = A .B Truth Table A B Q 0 0 1 0 1 1 1 0 1 1 1 0 Read as A AND B gives NOT-Q 2-input NOR (Not OR) Gate For a 2-input NOR gate, the output Q is true if BOTH input A and input B are NOT true, giving the Boolean Expression of: ( Q = not(A or B) ). Symbol Boolean Expression Q = A+B Truth Table A B Q 0 0 1 0 1 0 1 0 0 1 1 0 Read as A OR B gives NOT-Q 4 Number System and Logic Families As well as the standard logic gates there are also two special types of logic gate function called anExclusive-OR Gate and an Exclusive-NOR Gate. The actions of both of these types of gates can be made using the above standard gates however, as they are widely used functions, they are now available in standard IC form and have been included here as reference. 2-input EX-OR (Exclusive OR) Gate For a 2-input Ex-OR gate, the output Q is true if EITHER input A or if input B is true, but NOT both giving the Boolean Expression of: ( Q = (A and NOT B) or (NOT A and B) ). Symbol Boolean Expression Q = A Truth Table A B Q 0 0 0 0 1 1 1 0 1 1 1 0 B 2-input EX-NOR (Exclusive NOR) Gate For a 2-input Ex-NOR gate, the output Q is true if BOTH input A and input B are the same, either true or false, giving the Boolean Expression of: ( Q = (A and B) or (NOT A and NOT B) ). Symbol Truth Table A B 5 Q Number System and Logic Families Boolean Expression Q = A 0 0 1 0 1 0 1 0 0 1 1 1 B Summary of 2-input Logic Gates The following Truth Table compares the logical functions of the 2-input logic gates above. Inputs Truth Table Outputs For Each Gate A B AND NAND OR NOR EX-OR EX-NOR 0 0 0 1 0 1 0 1 0 1 0 1 1 0 1 0 1 0 0 1 1 0 1 0 1 1 1 0 1 0 0 1 The following table gives a list of the common logic functions and their equivalent Boolean notation. Logic Function Boolean Notation AND A.B OR A+B NOT A 6 Number System and Logic Families NAND A .B NOR A+B EX-OR (A.B) + (A.B) or A EX-NOR (A.B) + or A B B 2-input logic gate truth tables are given here as examples of the operation of each logic function, but there are many more logic gates with 3, 4 even 8 individual inputs. The multiple input gates are no different to the simple 2-input gates above, So a 4input AND gate would still require ALL 4-inputs to be present to produce the required output at Q and its larger truth table would reflect that. The Laws of Boolean As well as the logic symbols “0” and “1” being used to represent a digital input or output, we can also use them as constants for a permanently “Open” or “Closed” circuit or contact respectively. A set of rules or Laws of Boolean Algebra expressions have been invented to help reduce the number of logic gates needed to perform a particular logic operation resulting in a list of functions or theorems known commonly as the Laws of Boolean Algebra. Boolean Algebra is the mathematics we use to analyse digital gates and circuits. We can use these “Laws of Boolean” to both reduce and simplify a complex Boolean expression in an attempt to reduce the number of logic gates required.Boolean Algebra is therefore a system of mathematics based on logic that has its own set of rules or laws which are used to define and reduce Boolean expressions. The variables used in Boolean Algebra only have one of two possible values, a logic“0” and a logic “1” but an expression can have an infinite number of variables all labelled individually to represent inputs to the expression, For example, 7 Number System and Logic Families variablesA, B, C etc, giving us a logical expression of A + B = C, but each variable can ONLY be a 0 or a 1. Examples of these individual laws of Boolean, rules and theorems for Boolean Algebra are given in the following table. Truth Tables for the Laws of Boolean Boolean Expression A+1=1 A+0=A A.1=A A.0=0 A+A=A A.A=A Equivalent Description A in Switching Circuit Law or Rule parallel with closed = "CLOSED" A in parallel with series with series with open = "A" A in closed = "A" A in open = "OPEN" A in parallel with series with A = "A" A in Boolean A = "A" 8 Annulment Identity Identity Annulment Idempotent Idempotent Algebra Number System and Logic Families NOT A = A A+A=1 A.A=0 A+B = B+A A.B = B.A A+B = A.B A.B = A+B NOT NOT A (double negative) = "A" A in parallel with NOT A = "CLOSED" A in series with NOT A = "OPEN" A in parallel with B= with B= B in parallel with A A in series B in series with A Double Negation Complement Complement Commutative Commutative invert and replace OR with de AND Theorem invert and replace AND with de OR Theorem Morgan’s Morgan’s The basic Laws of Boolean Algebra that relate to the Commutative Law allowing a change in position for addition and multiplication, the Associative Law allowing the removal of brackets for addition and multiplication, as well as the Distributive Law allowing the factoring of an expression, are the same as in ordinary algebra. Each of the Boolean Laws above are given with just a single or two variables, but the number of variables defined by a single law is not limited to this as there can be an infinite number of variables as inputs too the expression. These Boolean laws detailed 9 Number System and Logic Families above can be used to prove any given Boolean expression as well as for simplifying complicated digital circuits. A brief description of the various Laws of Boolean are given below with Arepresenting a variable input. Description of the Laws of Boolean Algebra Annulment Law – A term AND´ed with a “0” equals 0 or OR´ed with a “1” will equal 1. o A . 0 = 0 A variable AND’ed with 0 is always equal to 0. o A + 1 = 1 A variable OR’ed with 1 is always equal to 1. Identity Law – A term OR´ed with a “0” or AND´ed with a “1” will always equal that term. o A + 0 = A A variable OR’ed with 0 is always equal to the variable. o A . 1 = A A variable AND’ed with 1 is always equal to the variable. Idempotent Law – An input that is AND´ed or OR´ed with itself is equal to that input. o A + A = A A variable OR’ed with itself is always equal to the variable. o A . A = A A variable AND’ed with itself is always equal to the variable. 10 Number System and Logic Families Complement Law – A term AND´ed with its complement equals “0” and a term OR´ed with its complement equals “1”. o A . A = 0 A variable AND’ed with its complement is always equal to 0. o A + A = 1 A variable OR’ed with its complement is always equal to 1. Commutative Law – The order of application of two separate terms is not important. o A.B=B.A The order in which two variables are AND’ed makes no difference. o A+B=B+A The order in which two variables are OR’ed makes no difference. Double Negation Law – A term that is inverted twice is equal to the original term. o A = A A double complement of a variable is always equal to the variable. de Morgan´s Theorem – There are two “de Morgan´s” rules or theorems, (1) Two separate terms NOR´ed together is the same as the two terms inverted (Complement) and AND´ed for example, A+B = A. B. 11 Number System and Logic Families (2) Two separate terms NAND´ed together is the same as the two terms inverted (Complement) and OR´ed for example, A.B = A +B. Other algebraic Laws of Boolean not detailed above include: Distributive Law – This law permits the multiplying or factoring out of an expression. o A(B + C) = A.B + A.C (OR Distributive Law) o A + (B.C) = (A + B).(A + B) (AND Distributive Law) Absorptive Law – This law enables a reduction in a complicated expression to a simpler one by absorbing like terms. o A + (A.B) = A (OR Absorption Law) o A(A + B) = A (AND Absorption Law) Associative Law – This law allows the removal of brackets from an expression and regrouping of the variables. o A + (B + C) = (A + B) + C = A + B + C (OR Associate Law) o A(B.C) = (A.B)C = A . B . C (AND Associate Law) 12 Number System and Logic Families Boolean Algebra Functions Using the information above, simple 2-input AND, OR and NOT Gates can be represented by 16 possible functions as shown in the following table. Function Description Expression 1. NULL 0 2. IDENTITY 1 3. Input A A 4. Input B B 5. NOT A A 6. NOT B B 7. A AND B (AND) A.B 8. A AND NOT B A.B 9. NOT A AND B A.B 10. NOT A AND NOT B (NAND) A . B 11. A OR B (OR) A+B 12. A OR NOT B A+B 13 Number System and Logic Families 13. NOT A OR B A+B 14. NOT OR (NOR) A+B 15. Exclusive-OR A.B + A.B 16. Exclusive-NOR A.B + A.B Laws of Boolean Algebra Example No1 Using the above laws, simplify the following expression: (A + B)(A + C) Q = (A + B).(A + C) A.A + A.C + A.B + B.C– Distributive law A + A.C + A.B + B.C – Idempotent AND law (A.A = A) A(1 + C) + A.B + B.C – Distributive law A.1 + A.B + B.C – Identity OR law (1 + C = 1) A(1 + B) + B.C – Distributive law A.1 + B.C – Identity OR law (1 + B = 1) Q = A + (B.C) – Identity AND law (A.1 = A) Then the expression: (A + B)(A + C) can be simplified to A + (B.C) as in the Distributive law. Number System : 14 Number System and Logic Families A set of values used to represent different quantities is known as Number System". For example, a number system can be used to represent the number of students in a class or number of viewers watching a certain TV program etc. The digital computer represents all kinds of data and information in binary numbers. It includes audio, graphics, video, text and numbers. The total number of digits used in a number system is called its base or radix. The base is written after the number as subscript such as 51210. Some important number systems are as follows. Decimal number system Binary number system Octal number system Hexadecimal number system The decimal number system is used in general. However, the computers use binary number system. The octal and hexadecimal number systems are used in the computer. Decimal number System See Also: Convert decimal numbers to binary numbers The Decimal Number System consists of ten digits from 0 to 9. These digits can be used to represent any numeric value. The base of decimal number system is 10. It is the most widely used number system. The value represented by individual digit depends on weight and position of the digit. Each number in this system consists of digits which are located at different positions. The position of first digit towards left side of the decimal point is 0. The position of second digit towards left side of the decimal point is 1. Similarly, the position of first digit towards right side of decimal point is -1. The position of second digit towards right side of decimal point is -2 and so on. 15 Number System and Logic Families The value of the number is determined by multiplying the digits with the weight of their position and adding the results. This method is known as expansion method. The rightmost digit of number has the lowest weight. This digit is called Least Significant Digit (LSD). The leftmost digit of a number has the highest weight. This digit is called Most Significant Digit (MSD). The digit 7 in the number 724 is most significant digit and 4 is the least significant digit. See Also: Number Bases Example: The weights and positions of each digit of the number 453 are as follows: Position 2 1 0 Weights 102 101 100 Face value 4 5 3 The above table indicates that: The value of digit 4 = 4x102 = 400 The value of digit 4 = 5x10 = 50 The value of digit 3 = 3x10 = 3 The actual number can be found by adding the values obtained by the digits as follows: 400 + 50 + 3 =45310 Example: The weights and positions of each digit of the number 139.78 are as follows. Position 2 1 0 Weights 102 101 100 16 . -1 -2 10-1 10-2 Number System and Logic Families Face Value 1 3 9 7 8 The above table indicates that: The value of digit 1 = 1x102 = 100 The value of digit 3 = 3x101 = 30 The value of digit 9 = 9x100 = 9 The value of digit 7 = 7x10-1 = 0.7 The value of digit 8 = 8x10-2 = 0.08 The actual number can be found by adding the values obtained by the digits as follows: 100 + 30 + 9 + 0.7 + 0.8 = 139.78 Binary Number System Digital computer represents all kinds of data and information in the binary system. Binary Number System consists of two digits 0 and 1. Its base is 2. Each digit or bit in binary number system can be 0 or 1. A combination of binary numbers may be used to represent different quantities like 1001. The positional value of each digit in binary number is twice the place value or face value of the digit of its right side. The weight of each position is a power of 2. The place value of the digits according to position and weight is as follows: Position 3 2 1 0 Weights 23 22 21 20 Example: Convert 101112 decimal number Position 2 1 0 17 -1 -2 Number System and Logic Families Weights 102 101 100 10-1 10-2 Face Value 1 3 9 7 8 101112 = 1 x 24 + 0 x 23 + 1 x 22 + 1 x 21 + 1 x 20 = 1 x 16 + 0 + 1 x 4 + 1 x 2 + 1 x 1 = 16 + 0 + 4 2 + 1 = 2310 Example: Convert 101.1012 Position 2 1 0 Face Value 1 0 1 Weight 24 21 20 101.1012 = . -1 -2 -3 1 0 1 2-1 2-2 2-3 1 x 22 + 0x21 + 1 x 20 + 1x 2-1 + 0 x 2-2 + 1 x 2-3 = 1 x 4 + 0 + 1 x 1 + ½ + 0 + 1/8 = 4 + 0 + 1 + 0.5 + 0.125 = 5.62510 Octal Number System Octal Number System consists of eight digits from 0 to 7. The base of octal system is 8. Each digit position in this system represents a power of 8. Any digit in this system is always less than 8. Octal number system is used as a shorthand representation of long binary numbers. The number 6418 is not valid in this number system as 8 is not a valid digit. The place value of each digit according to position and weight is as follows. Position 4 3 2 18 1 0 Number System and Logic Families Weight 84 83 82 81 80 Example: convert 458 to decimal number 458 = 4 x 81 + 5 x 80 = 4x8+5x1 = 32 + 5 = 3710 Hexadecimal number system The Hexadecimal Number System consists of 16 digits from 0 to 9 and A to F. The alphabets A to F represent decimal numbers from 10 to 15. The base of this number system is 16. Each digit position in hexadecimal system represents a power of 16. The number 76416 is valid hexadecimal number. It is different from 76410 which is seven hundred and sixty four. This number system provides shortcut method to represent long binary numbers. The place value of each digit according to position and weight is as follows: Position 4 3 2 1 0 Weights 164 163 162 161 160 Example: Convert 3A16 to decimal number 3A16 = 3 x 161 + A x 160 = 3 x 16 + 10 x 1 = 48 + 10 = 5810 19 Number System and Logic Families Conversion Between Different Number Systems Positional number systems Our decimal number system is known as a positional number system, because the value of the number depends on the position of the digits. For example, the number 123 has a very different value than the number 321, although the same digits are used in both numbers. (Although we are accustomed to our decimal number system, which is positional, other ancient number systems, such as the Egyptian number system were not positional, but rather used many additional symbols to represent larger values.) In a positional number system, the value of each digit is determined by which place it appears in the full number. The lowest place value is the rightmost position, and each successive position to the left has a higher place value. In our decimal number system, the rightmost position represents the "ones" column, the next position represents the "tens" column, the next position represents "hundreds", etc. Therefore, the number 123 represents 1 hundred and 2 tens and 3 ones, whereas the number 321 represents 3 hundreds and 2 tens and 1 one. The values of each position correspond to powers of the base of the number system. So for our decimal number system, which uses base 10, the place values correspond to powers of 10: ... 1000 100 ... 10^3 10 1 10^2 10^1 10^0 20 Number System and Logic Families Converting from other number bases to decimal Other number systems use different bases. The binary number system uses base 2, so the place values of the digits of a binary number correspond to powers of 2. For example, the value of the binary number 10011 is determined by computing the place value of each of the digits of the number: 1 0 0 1 1 the binary number 2^4 2^3 2^2 2^1 2^0 place values So the binary number 10011 represents the value (1 * 2^4) + (0 * 2^3) + (0 * 2^2) + (1 * 2^1) + (1 * 2^0) = 16 0 + 0 2 1 = 19 The same to any number 2 number in base 5 + principle applies + base. number 2132 base 5 corresponds to 2 1 3 5^3 5^2 5^1 5^0 place values 21 + For example, the Number System and Logic Families So the value of the number is (2 * 5^3) + (1 * 5^2) + (3 * 5^1) + (2 * 5^0) = (2 * 125) + (1 * 25) + (3 * 5) + (2 * 1) = 250 + 15 + 2 + 25 = 292 Converting from decimal to other number bases In order to convert a decimal number into its representation in a different number base, we have to be able to express the number in terms of powers of the other base. For example, if we wish to convert the decimal number 100 to base 4, we must figure out how to express 100 as the sum of powers of 4. 100 = (1 * 64) + (2 * 16) + (1 * 4) + (0 * 1) = (1 * 4^3) + (2 * 4^2) + (1 * 4^1) + (0 * 4^0) Then we use the coefficients of the powers of 4 to form the number as represented in base 4: 100 = 1210 base 4 22 Number System and Logic Families One way to do this is to repeatedly divide the decimal number by the base in which it is to be converted, until the quotient becomes zero. As the number is divided, the remainders - in reverse order - form the digits of the number in the other base. Example: Convert the decimal number 82 to base 6: 82/6 = 13 remainder 4 13/6 = 2 remainder 1 2/6 0 remainder 2 = The answer is formed by taking the remainders in reverse order: 2 1 4 base There are many methods or techniques which can be used to convert numbers from one base to another. We'll demonstrate here the following Decimal to Other Base System Other Base System to Decimal Other Base System to Non-Decimal Shortcut method - Binary to Octal Shortcut method - Octal to Binary Shortcut method - Binary to Hexadecimal Shortcut method - Hexadecimal to Binary Decimal to Other Base System 23 Number System and Logic Families Steps Step 1 - Divide the decimal number to be converted by the value of the new base. Step 2 - Get the remainder from Step 1 as the rightmost digit (least significant digit) of new base number. Step 3 - Divide the quotient of the previous divide by the new base. Step 4 - Record the remainder from Step 3 as the next digit (to the left) of the new base number. Repeat Steps 3 and 4, getting remainders from right to left, until the quotient becomes zero in Step 3. The last remainder thus obtained will be the most significant digit (MSD) of the new base number. EXAMPLE Decimal Number: 2910 Calculating Binary Equivalent: Step Operation Result Remainder Step 1 29 / 2 14 1 Step 2 14 / 2 7 0 Step 3 7/2 3 1 Step 4 3/2 1 1 24 Number System and Logic Families Step 5 1/2 0 1 As mentioned in Steps 2 and 4, the remainders have to be arranged in the reverse order so that the first remainder becomes the least significant digit (LSD) and the last remainder becomes the most significant digit (MSD). Decimal Number: 2910 = Binary Number: 111012. Other base system to Decimal System Steps Step 1 - Determine the column (positional) value of each digit (this depends on the position of the digit and the base of the number system). Step 2 - Multiply the obtained column values (in Step 1) by the digits in the corresponding columns. Step 3 - Sum the products calculated in Step 2. The total is the equivalent value in decimal. EXAMPLE Binary Number: 111012 Calculating Decimal Equivalent: Step Step 1 Binary Number 111012 Decimal Number ((1 x 24) + (1 x 23) + (1 x 22) + (0 x 21) + (1 x 20))10 25 Number System and Logic Families Step 2 111012 (16 + 8 + 4 + 0 + 1)10 Step 3 111012 2910 Binary Number: 111012 = Decimal Number: 2910 Other Base System to Non-Decimal System Steps Step 1 - Convert the original number to a decimal number (base 10). Step 2 - Convert the decimal number so obtained to the new base number. EXAMPLE Octal Number: 258 Calculating Binary Equivalent: STEP 1: CONVERT TO DECIMAL Step Octal Number Decimal Number Step 1 258 ((2 x 81) + (5 x 80))10 Step 2 258 (16 + 5 )10 Step 3 258 2110 Octal Number: 258 = Decimal Number: 2110 STEP 2: CONVERT DECIMAL TO BINARY Step Operation Result 26 Remainder Number System and Logic Families Step 1 21 / 2 10 1 Step 2 10 / 2 5 0 Step 3 5/2 2 1 Step 4 2/2 1 0 Step 5 1/2 0 1 Decimal Number: 2110 = Binary Number: 101012 Octal Number: 258 = Binary Number: 101012 Shortcut method - Binary to Octal Steps Step 1 - Divide the binary digits into groups of three (starting from the right). Step 2 - Convert each group of three binary digits to one octal digit. EXAMPLE Binary Number: 101012 Calculating Octal Equivalent: Step Binary Number Octal Number Step 1 101012 010 101 Step 2 101012 28 58 27 Number System and Logic Families Step 3 101012 258 Binary Number: 101012 = Octal Number: 258 Shortcut method - Octal to Binary Steps Step 1 - Convert each octal digit to a 3 digit binary number (the octal digits may be treated as decimal for this conversion). Step 2 - Combine all the resulting binary groups (of 3 digits each) into a single binary number. EXAMPLE Octal Number: 258 Calculating Binary Equivalent: Step Octal Number Binary Number Step 1 258 210 510 Step 2 258 0102 1012 Step 3 258 0101012 Octal Number: 258 = Binary Number: 101012 Shortcut method - Binary to Hexadecimal Steps Step 1 - Divide the binary digits into groups of four (starting from the right). Step 2 - Convert each group of four binary digits to one hexadecimal symbol. 28 Number System and Logic Families EXAMPLE Binary Number: 101012 Calculating hexadecimal Equivalent: Step Binary Number Hexadecimal Number Step 1 101012 0001 0101 Step 2 101012 110 510 Step 3 101012 1516 Binary Number: 101012 = Hexadecimal Number: 1516 Shortcut method - Hexadecimal to Binary Steps Step 1 - Convert each hexadecimal digit to a 4 digit binary number (the hexadecimal digits may be treated as decimal for this conversion). Step 2 - Combine all the resulting binary groups (of 4 digits each) into a single binary number. EXAMPLE Hexadecimal Number: 1516 Calculating Binary Equivalent: Step Hexadecimal Number Binary Number 29 Number System and Logic Families Step 1 1516 110 510 Step 2 1516 00012 01012 Step 3 1516 000101012 Hexadecimal Number: 1516 = Binary Number: 101012 Binary Arithmetic VLSI design components on most microchips perform binary arithmetic. These components are easier to design than ones performing decimal arithmetic. Addition: 0 + 0 = 0 0 + 1 = 1 1 + 0 = 1 = 0 1 + 1 = 0 and carry 1 to the next column Subtraction: 0 - 0 0 - 1 = 1 and borrow 1 from next column (equivalent to subtracting one from that next column, alternative to binary subtraction is to use 2's 1 complement, - see 0 1-1=0 Multiplication 30 later) = 1 Number System and Logic Families 0 * 0 = 0 0 * 1 = 0 1 * 0 = 0 1*1=1 Examples: 1 1 0 1 _____________ 1101 *1011 1 1 1 1 1 1 1 1 1 1101 11101 10000 +1011 - 10011 - 1101 11 1 1 0 1 1 0 1 1 // 1 0 0 1 0 0 0 1 1011 1 1 1 0 1011 0 0 0 0 1101 11000 1010 1101 1 1 0 1 1011 10001111 10 (note on multiplication example: each partial product is either zero or the multiplicand shifted over an appropriate number of places). 31 Number System and Logic Families Representation of Negative Numbers There are several ways of representing negative binary numbers: sign and magnitude system, 1's complement, 2's complement, R's complement, etc. 1. Sign and Magnitude: Consider n-bit word: first bit is sign bit (0 for plus, 1 for negative), other n-1 bits are magnitude. One can represent any one of 2 n-1 positive integers or 2n-1 negative integers. However with this representation the design of arithmetic components to perform arithmetic is awkward. 2. 1's complement : A negative number, -N, is represented by its 1's complement defined as taking the positive number N and complementing bit by bit to produce the negative number -N. Alternatively -N = ( 2n - 1 ) - N. As an example consider n=4, -N is represented by 15 - N , so 0 0 1 0 = N, N=2, -N is 1 1 0 1 = 13 ( or =15 - N = 15 - 2) . Note that in this n=4 number system , -0 and -8 have no representation. 3. 2's complement system: a positive number N, is represented by a 0 followed by the magnitude of N. However a negative number -N is represented by it's 2's complement, N*. For n-bit system, N* = 2n - N , or complement N bit by bit and then Add 1. As an example consider 0010 (N=2), -N is formed by taking 1101 + 1 = 1110 (or = N*= 2n - N = 16 - 2 = 14) . 4. R's complement system: For base R system, with word length = n bits, for a positive number N then R's complement is N* = Rn - N and (R-1)'s complement is (Rn-1)-N. As an example, R=8 (octal), n=4, then the 8's complement of 03458 is 100008 32 Number System and Logic Families 03458 = 74338 . and the 7's complement is (100008 - 1) -03458 = 7777 - 0345 = 74328 . Note that just as the 1's complement can be formed on a bit by bit approach, the (R-1)'s complement can be formed on a digit by digit approach, so for octal numbers the 7's complement can be formed by subtracting each digit from 7 . Addition of 2's complement numbers Perform the addition in the same manner you would do for two positive numbers. (ignore any carries from the sign position). This way will always be correct, except when an overflow occurs. For an n bit word an overflow exists if the correct representation of the sum (including sign) requires more than n bits. If two positive nbit numbers sum to form a negative n-bit number or if two negative n-bit numbers sum to form a positive n-1 sum < 2n-1 0011 0100 sum >= 2 0101 n-bit -N > number, +N 0110 0111 Correct 1101 occured. sum > 2n-1 1011 1100 1010 1010 (1) 1011 has -M sum <= 2n-1 1011 +M 0101 0110 > then overflow Wrong Overflow! 1111 Correct 0001 (1)1001 (1) Correct, ignore Correct, carry from sign ignore bit Addition of 1's complement numbers 33 carry. last 0101 Wrong, Overflow! Number System and Logic Families Similar to 2's complement arithmetic, except carry from the sign bit is added to the n bit sum in the right most position, this is called the "end-around carry". 1010 0110 1100 1010 1011 1001 0101 1001 (1)0000 (1)0111 1 "end-around carry" 1 "end-around (1)0011 1 carry" 1110 Correct 0001 correct overflow) (no 1000 Correct (no overflow) 0100 Wrong , Overflow! Note again, one can extend arithmetic to any base. For example base R, R's complement representation for negative numbers, add numbers and discard the carry from ie. the 4 digit octal last digit numbers, Consider -0345 position. + 0672 : - 0345 in 8's complement is 7433 -345 in 7's complement is 7432 + 7433 7432 0672 +0672 ===== ===== (1)0325 (1)0324 34 Number System and Logic Families discard carry , 0325 1 "end-around carry" ===== 0325 Codes Code is a symbolic representation of discrete information. Codes are of different types. In digital electronics, codes are used to communicate the information between computers. These codes represent the information symbolically as a string of bits 0 and 1 and rules defined by the code decide the arrangement of these bits. Codes can be broadly categorized into three categories 1) Weighted Codes 2) Unweighted Codes 3) Sequential Codes 1)Weighted Codes These codes are positionally weighted and each position with in the binary equivalent of the number is assigned a fixed value. Thus, they obey positional weighting principal. Binary Coded Decimal(BCD) is an example of weighted codes. In this code, the binary equivalent of a number will always remain same. To understand how to compute bcd equivalent of a number, you may refer below link: Binary Coded Decimal 2)Unweighted Codes 35 Number System and Logic Families These codes are not positionally weighted i.e. each position with in the binary equivalent of the number is not assigned a fixed value. Thus, unweighted codes do not obey positional weighting principal. Grey code is an example of unweighted codes.In grey code, computation not only depends on the bit under consideration but also on the neighboring bits. Due to which, unlike weighted codes, the binary equivalent of a number may return different values on each computation Excess-3 code is also an example of unweighted code. To understand how to compute grey code or excess-3 equivalent of a number, you may refer below link: Grey Code Excess-3 Code 3)Sequential Codes A code is said to be sequential when each succeeding code is one binary number greater than the preceeding code. BCD and Excess-3 codes are examples of sequential codes in digital electronics. Thus, this post summarizes various codes used in digital electronics to communication information. Feel free to leave your footprints in the comments section below for any queries, suggestions or feedback. Binary Codes 36 Number System and Logic Families Decimal numbers can be coded in terms of binary signals. The simplest coding is binary coded decimal or BCD, where each decimal digit is replaced by it's 4 bit binary equivalent. Example: 937.25 is 100100110111.00100101 9 3 7. 2 5 1001 0011 0111. 0010 0101 Note that the result is quite different from that obtained by converting the number as a whole Below into is a table of binary binary. codes for decimal digits: Decimal 8421 6311 excess-3 2out-of-5 Gray Digit (BCD) Code Code Code Code 0 0000 0000 0011 00011 0000 1 0001 0001 0100 00101 0001 2 0010 0011 0101 00110 0011 3 0011 0100 0110 01001 0010 4 0100 0101 0111 01010 0110 5 0101 0111 1000 01100 1110 6 0110 1000 1001 10001 1010 7 0111 1001 1010 10010 1011 8 1000 1011 1011 10100 1001 9 1001 1100 1100 11000 1000 37 Number System and Logic Families the 8421 and 6311 are called weighted codes, where if weights are w3,w2,w1,w0 then code a3,a2,a1,a0 represents decimal number N, N=w3 a3 + w2 a2 + w1 a1 + w0 a0 excess-3 code is obtained by adding 3 (0011) to each of the BCD codes 2 out of 5 code, has exactly 2 out of 5 bits that are '1', which is useful for error checking gray code: codes for successive decimal digits differ in one bit only. Useful for low power applications, where reduction in switching is important. (ie difference between 6 and 7 is in bit 4 only) in general the decimal value of a coded digit cannot be computed by a single formula when a non-weighted code is used. other codes, such as ASCII, EBCDIC involve letters, symbols, punctuation marks, etc... Code Conversion: 1) Binary to gray code conversion Binary to gray code conversion is a very simple process. There are several steps to do this types of conversions. Steps given below elaborate on the idea on this type of conversion. (1) The M.S.B. of the gray code will be exactly equal to the first bit of the given binary number. (2) Now the second bit of the code will be exclusive-or of the first and second bit of the given binary number, i.e if both the bits are same the result will be 0 and if they are different the result will be 1. (3)The third bit of gray code will be equal to the exclusive-or of the second and third bit of the given binary number. Thus the Binary to gray code conversion 38 Number System and Logic Families goes on. One example given below can make your idea clear on this type of conversion. Let (01001) be the given binary number (01001)2 = ( ? )Grey Exor Exor Exor Exor 0 1 0 0 1 0 1 1 0 1 =(01101)grey Gray code to binary conversion Gray code to binary conversion is again very simple and easy process. Following steps can make your idea clear on this type of conversions. (1) The M.S.B of the binary number will be equal to the M.S.B of the given gray code. (2) Now if the second gray bit is 0 the second binary bit will be same as the previous or the first bit. If the gray bit is 1 the second binary bit will alter. If it was 1 it will be 0 and if it was 0 it will be 1. (3) This step is continued for all the bits to do Gray code to binary conversion. 39 Number System and Logic Families (01001)Grey =(?)2 0 1 Ex-Or Ex-Or 0 1 0 0 1 Ex-Or Ex-Or 1 1 0 Answer= (01110)2 BCD (Binary-Coded Decimal) code : Four-bit code that represents one of the ten decimal digits from 0 to 9. Example - (37)10 is represented as 0011 0111 using BCD code, rather than (100101)2 in straight binary code. Thus BCD code requires more bits than straight binary code. Still it is suitable for input and output operations in digital systems. Note: 1010, 1011, 1100, 1101, 1110, and 1111 are INVALID CODE in BCD code. Excess-3 code: 4-bit code is obtained by adding binary 0011 to the natural BCD code of the digit. Example - decimal 2 is coded as 0010 + 0011 = 0101 as Excess-3 code. It not weighted code. Its self-complimenting code, means 1's complement of the coded number yields 9's complement of the number itself. Used in digital system for performing substraction operations. 40 Number System and Logic Families ASCII (American Standard Code Information Interchange) code : It is 7-bit or 8-bit alphanumeric code. 7-bit code is standard ASCII supports 127 characters. Standard ASCII series starts from 00h to 7Fh, where 00h-1Fh are used as control characters and 20h-7Fh as graphics symbols. 8-bit code is extended ASCII supports 256 symbols where special graphics and math's symbols are added. Extended ASCII series starts from 80h to FFh. EBCDIC (Extended Binary Coded Decimal Interchange Code) code 8-bit alphanumeric code developed by IBM, supports 256 symbols. It was mainly used in IBM mainframe computers. Switching Characteristics of BJT & FET: BJTs are characterized by linear current transfer function between the collector current and the base current. They have much larger transconductance and they can achieve much higher input signal gain thanks to their current control. In addition, they have higher speeds and higher maximum operating frequency. Consequently, they are preferred in the amplifier circuits and in the linear integrated circuits as well as high frequency and high power applications. When BJTs are operated as switches, they consume appreciable power and therefore they are less suitable in VLSI integrated circuits. They are used in very high speed logic circuits such as TTL and ECL. They consume more area on the chip than the mos transistors. The FETs are characterized by high input impedance and some types of FETS operate 41 Number System and Logic Families as a relay such as the enhancement MOSFETS making them superior as switches. Their nonlinear transfer characteristics between the drain current and the gate to source voltage and their smaller trans conductance makes them less suitable in amplifier circuits. Therefore, we see that the dominating logic family for implementing memories, CPUs and DSPs are made of MOS transistors especially the complementary CMOS transistors which have good logic performance parameters. The static power consumption of the CMOS is negligible. In summary, the applications of a device and its dominance in some applications stem from its characteristics , availability, cost and familiarity. 1. Transistor–transistor logic (TTL) is a class of digital circuits built from bipolar junction transistors (BJT) and resistors. It is called transistor–transistor logic because both the logic gating function (e.g., AND) and the amplifying function are performed by transistors (contrast with RTL and DTL). 2. A particular characteristic of TTL signals is that the inputs to a gate “float high” — i.e. rise to a logical ‘1’ — if left unconnected. This means that the main requirement for driving a TTL input is to “pull down” the level to near 0V. This typically takes a few milliamps per input. This is usually described by saying that a TTL signal source has to be able to “sink” a relatively large current. Typically, TTL gates take around 10-20 nanoseconds to switch level. Hence we can ‘clock’ TTL and pass bits through the gates at rates up to around 50MHz provided the circuits are designed carefully. With care, speeds approaching 100MHz are possible, but for high speed operation other forms of logic Lots of TTL gates are available 42 may work better. Number System and Logic Families Transistor Transistor Logic or TTL Under Digital ElectronicsThe full form of TTL is Transistor Transistor Logic. This is a logic family which is mainly build up of NPN transistors, PN junction diodes and diffused resistors. The basic building block of this logic family is NAND gate and there are various subfamilies of this logic gate those are standard TTL, advanced Schottky TTL, schottky TTL, low power TTL, high power TTL, fast TTL etc. now to know about this family in a more descriptive way we will discuss the internal structure and characteristic parameters of some of its subfamilies. Standard TTL The above figure shows the internal structure and characteristics of a standard TTL NAND gate. The NAND gate of it is a quad two input type. And it has four circuits of 5400/740. In plain ways the circuit of this type of TTL operates as follows. The Q1 showed in the figure is a two emitter NPN transistor. This type is NAND gate is analogous to two transistors whose base and emitter terminals are joined together. The 43 Number System and Logic Families diodes named as D2 and D3 are used to limit the input voltages which are negative in nature. Low Power TTL This is a subfamily under the main family. This is named so because lower power consumption and dissipation is achieved. Though the speed at which the operation is done is somewhat reduced. The above figure is of a low power TTL which is made using NAND gates. The NAND gate used in this is of 74L00 or 54L00 type and is of quad two input type. The construction of this type of TTL is almost similar to that of standard TTL except the resistance which is of a higher value. For this increased value of the resistance the power dissipation of the circuit is lowered. High Power TTL 44 Number System and Logic Families Unlike the low power TTL the High power TTL is the high speed edition of the standard TTL. The speed of operation of this type of TTL is more than the previously discussed. The power dissipation for this higher than other previously discussed TTLs. The above diagram is of a high power TTL NAND gate. The NAND gate is a quad two input of type 74H00 or 54H00. The above drawn figure is very similar to that of a standard TTL except Q3 transistor and D1 diode combination, which has been replaced by an arrangement of Q3, Q5 and R5. The speed of operation is higher and the power dissipation is also higher for this type of TTLs. Schottky TTL 45 Number System and Logic Families Another TTL subfamily is Schottky TTL. This design was used to speed up the time of operation. The speed offered by this type of TTL is twice the speed that is offered by the high power TTL. The power dissipation for both the TTLs are same and there is no extra power consumption. The figure above represents the basic NAND based diagram of Schottky TTL. The circuit diagram is pretty much similar to that of a high power TTL, here the Q transistor of high power TTL is missing. The Schottky transistor which is used for this type TTL is nothing but a bipolar transistor which has its base and collector connected by a schottky diode. This Schottky TTL is further devided in many parts like low power Schottky, Advanced low power schottky and advanced Schottky whose discussion has been avoided due to complexities. Basic Properties of some TTL Families. 74 family Supply Voltage ‘1’ Level Output Current 74LS family 54 family +5V (+/- 0.5V) +5V (+/- 0.5V) +5V (+/- 0.25V) 0.4mA 0.4mA 46 0.4mA Number System and Logic Families ‘0’ Level Ouput Current 16mA 8mA 16mA ‘1’ Level Input Voltage (min) 2V 2V 2V ‘0’ Level Input Voltage (max) 0.8V 0.8V 0.8V ‘1’ Level Input Current 0.04mA 0.05mA 0.04mA ‘0’ Level Input Current 1.6mA 0.4mA 1.6mA Important characteristics of digital ICs 1. Fan out 2. Power dissipation 3. Propagation Delay 4. Noise Margin 5. Fan In 6. Operating temperature 7. Power supply requirements 1. Fan-out Fan out specifies the number of standard loads that the output of the gate can drive without impairment of its normal operation 2. Power dissipation Power dissipation is measure of power consumed by the gate when fully driven by all its inputs. 3. Propagation delay Propagation delay is the average transition delay time for the signal to propagate from input to output when the signals change in value. It is expressed in ns. 47 Number System and Logic Families 4. Noise margin It is the maximum noise voltage added to an input signal of a digital circuit that does not cause an undesirable change in the circuit output. It is expressed in volts. 5. Fan in Fan in is the number of inputs connected to the gate without any degradation in the voltage level. 6. Operating temperature All the gates or semiconductor devices are temperature sensitive in nature. The temperature in which the performance of the IC is effective is called as operating temperature. Operating temperature of the IC vary from 00 C to 700 c. TTL NAND Gate Basic TTL NAND Gate The circuit diagram for a 2-input LS-TTL NAND gate, part number 74LS00, is shown in Figure TTL-1. The NAND function is obtained by combining a diode AND gate with an inverting buffer amplifier. The circuit’s operation is best understood by dividing it into the three parts that are shown in the figure and discussed in the next three paragraphs: • Diode AND gate and input protection. • Phase splitter. • Output stage. Q5 VCC = +5 48 Number System and Logic Families Diodes D1X and D1Y and resistor R1 in Figure TTL-1 form a diode AND gate, as in Section Diode.2. Clamp diodes D2X and D2Y do nothing in normal operation, but limit undesirable negative excursions on the inputs to a single diode-drop. Such 49 Number System and Logic Families negative excursions may occur on HIGH-to-LOW input transitions as a result of transmission-line effects, discussed in Section Zo. Transistor Q2 and the surrounding resistors form a phase splitter that controls the output stage. Depending on whether the diode AND gate produces a “low” or a “high” voltage at VA, Q2 is either cut off or turned on. The output stage has two transistors, Q4 and Q5, only one of which is on at any time. The TTL output stage is sometimes called a totem-pole or push-pull output. Similar to the p-channel and n-channel transistors in CMOS, Q4 and Q5 provide active pull-up and pull-down to the HIGH and LOW states, respectively. The functional operation of the TTL NAND gate is summarized in Figure TTL-2(a). The gate does indeed perform the NAND function, with the truth table and logic symbol shown in (b) and (c). TTL NAND gates can be designed with any desired number of inputs simply by changing the number of diodes in the diode AND gate in the figure. Commercially available TTL NAND gates have as many as 13 inputs. A TTL inverter is designed as a 1-input NAND gate, omitting diodes D1Y and D2Y in Figure TTL-1. IILmax The maximum current that an input requires to pull it LOW IIHmax The maximum current that an input requires to pull it HIGH IOLmax The maximum current an output can sink in the LOW state while maintaining an output voltage no more than VOLmax. Since current flows into the output, IOLmax has a positive value, 8 mA for most LS-TTL outputs IOHmax The maximum current an output can source in the HIGH state while maintaining an output voltage no less than VOHmin. Since current flows out of the output, IOHmax has a negative value, −400 µA for most LS-TTL outputs. Fanout: fanout is a measure of the number of gate inputs that are connected to (and driven by) a single gate output. TTL Subfamilies: 50 Number System and Logic Families TTL NAND Gate with Totem Pole Outputs A two input standard TTL NAND gate is a multiple emitter transistor for the inputs A and B. the output transistors Q3 and Q4 form a totem-pole output arrangement. Operation: If A or B is low, the base-emitter junction of Q1 is forward biased and its basecollector junction is reverse biased. Then there is a current from Vcc through R1 ti the base emitter junction of Q1 and into the LOW input, which provides a path to the ground for the current. Hence there is no current into the base of Q2 and making it into cur-off. The collector of Q2 is HIGH and turns Q3 into saturation. Since Q3 acts as a emitter follower, bu providing a low impedance path from Vcc to the output, making the output into HIGH. At the same time, the emitter of Q2 is at ground potential, keping Q4 OFF. When A and B are high, the two input base emitter junctions of Q1 are reverse niased and its base collector junction is forward biased. This permits current through R1 and the base collector junction of Q1 into the base of Q2, thus driving Q2 into saturation. As a result Q4 is turned ON by Q2, and producing LOW ourput which is near ground potential. At the same time, the collector of Q2 is sufficiently at LOW voltage level to keep Q3 OFF. TTD NAND Gate with open-collector outputs A two input TTL NAND gate with open collector output is the collector of the transistor Q3 with nothing connected to it, hence it is known as ‘open collector output’. But the circuit is not completed and in order to get the proper HIGH and LOW logic levels at the output of the circuit; an external pull-up resistor must be connected between Vcc and the collector of Q3. 51 Number System and Logic Families Operation: A low on either input A or input B forward biases the base emitter junction of Q1 and reverse biases it’s base collector junction. There is current through R1 and the base emitter junction of Q1 out to the low input. Then there is ni current into the base of Q2 and hence Q2 is in off. When both inouts are high, the base emitter junction of Q1 is reverse biased and it’s base collector junction is forward biased. This oermits current through R1 and the base collector junction of Q1 into the base of Q2, thus driving Q2 into saturation. As a result on by Q2, thus driving Q2 into saturation. As result, Q3 is turned on bu Q2. When Q3 is on, the output is connected to near ground through the saturated transistor; resulting the output as LOW. TTL – CMOS Introduction: Theory: A logic family of monolithic digital integrated circuit devices is a group of electronic logic gates constructed using one of several different designs, usually with compatible logic levels and power supply characteristics within a family. Many logic families were produced as individual components, each containing one or a few related basic logical functions, which could be used as "building-blocks" to create systems or as so-called "glue" to interconnect more complex integrated circuits. A "logic family" may also refer to a set of techniques used to implement logic within VLSI integrated circuits such as central processors, memories, or other complex functions. Some such logic families use static techniques to minimize design complexity. Other such logic families, such as domino logic, use clocked dynamic techniques to minimize size, power consumption, and delay. The first transistor– transistor logic family of integrated circuits was introduced by Sylvania as Sylvania Universal High–Level Logic (SUHL) in 1963. Texas Instruments introduced 5400 Series TTL family in 1964. Transistor–transistor logic uses bipolar transistors to form its integrated circuits. TTL has changed significantly over the years, with newer versions replacing the older types. Since the transistors of a standard TTL gate are saturated switches, minority carrier storage time in each junction limits the switching speed of the device. Variations on the basic TTL design are intended to reduce these effects and improve speed, power consumption, or both. 52 Number System and Logic Families The German physicist Walter H. Schottky formulated a theory predicting the Schottky effect, which led to the Schottky diode and later Schottky transistors. Schottky transistors have a much higher switching speed than conventional transistors because the Schottky junction does not promote charge storage, leading to faster switching gates. Gates built with Schottky transistors use more power than normal TTL and switch faster. With Low-power Schottky (LS), internal resistance values were increased to reduce power consumption and increase switching speed over the original version. The introduction of Advanced Low-power Schottky (ALS) further increased speed and reduced power consumption. A faster logic family called Fast (Schottky) (F) was also introduced that was faster than normal Schottky TTL. 2 Input TTL NAND Gate Interfacing considerations Like DTL, TTL is a current-sinking logic since a current must be drawn from inputs to bring them to a logic 0 level. At low input voltage, the TTL input sources current which must be absorbed by the previous stage. The maximum value of this current is about 1.6 mA for a standard TTL gate.[17] The input source has to be low-resistive enough (<500 Ω) so that the flowing current creates only a negligible voltage drop (<0.8 V) across it, for the input to be considered as a logical "0". TTL inputs are sometimes simply left floating to provide a logical "1", though this usage is not recommended. Standard TTL circuits operate with a 5-volt power supply. A TTL input signal is defined as "low" when between 0 V and 0.8 V with respect to the ground terminal, and "high" when between 2.2 V and VCC (5 V) and if a voltage signal ranges between 0.8 V and 2.0 V were to be sent into the input of a TTL gate, there would be no certain response from the gate and therefore it is considered "uncertain" (precise logic levels vary slightly between sub-types and by temperature). TTL outputs are 53 Number System and Logic Families typically restricted to narrower limits of between 0.0 V and 0.4 V for a "low" and between 2.6 V and VCC for a "high", providing at least 0.4 V of noise immunity. Standardization of the TTL levels was so ubiquitous that complex circuit boards often contained TTL chips made by many different manufacturers selected for availability and cost, compatibility being assured; two circuit board units off the same assembly line on different successive days or weeks might have a different mix of brands of chips in the same positions on the board; repair was possible with chips manufactured years (sometimes over a decade) later than original components. Within usefully broad limits, logic gates could be treated as ideal Boolean devices without concern for electrical limitations. In some cases (e.g., when the output of a TTL logic gate needs to be used for driving the input of a CMOS gate), the voltage level of the "totem-pole" output stage at output logical "1" can be increased up to VCC by connecting an external resistor between the V3 collector and the positive rail. It pulls up the V5 cathode and cuts-off the diode. However, this technique actually converts the sophisticated "totem-pole" output into a simple output stage having significant output resistance when driving a high level (determined by the external resistor). Sub-types Successive generations of technology produced compatible parts with improved power consumption or switching speed, or both. Although vendors uniformly marketed these various product lines as TTL with Schottky diodes, some of the underlying circuits, such as used in the LS family, could rather be considered DTL.[21] Variations of and successors to the basic TTL family, which has a typical gate propagation delay of 10ns and a power dissipation of 10 mW per gate, for a power– delay product (PDP) or switching energy of about 100 pJ, include: Low-power TTL (L), which traded switching speed (33ns) for a reduction in power consumption (1 mW) (now essentially replaced by CMOS logic) High-speed TTL (H), with faster switching than standard TTL (6ns) but significantly higher power dissipation (22 mW) Schottky TTL (S), introduced in 1969, which used Schottky diode clamps at gate inputs to prevent charge storage and improve switching time. These gates operated more quickly (3ns) but had higher power dissipation (19 mW) Low-power Schottky TTL (LS) – used the higher resistance values of lowpower TTL and the Schottky diodes to provide a good combination of speed (9.5ns) and reduced power consumption (2 mW), and PDP of about 20 pJ. 54 Number System and Logic Families Probably the most common type of TTL, these were used as glue logic in microcomputers, essentially replacing the former H, L, and S sub-families. Fast (F) and Advanced-Schottky (AS) variants of LS from Fairchild and TI, respectively, circa 1985, with "Miller-killer" circuits to speed up the low-tohigh transition. These families achieved PDPs of 10 pJ and 4 pJ, respectively, the lowest of all the TTL families. Low-voltage TTL (LVTTL) for 3.3-volt power supplies and memory interfacing. Most manufacturers offer commercial and extended temperature ranges: for example Texas Instruments 7400 series parts are rated from 0 to 70 °C and 5400 series devices over the military-specification temperature range of −55 to +125 °C. Special quality levels and high-reliability parts are available for military and aerospace applications. Radiation-hardened devices are offered for space applications. TTL CHARACTERISTICS Each logic family is characterized by several important parameters. These properties, and how they relate to the TTL logic families in particular, are explained below: Fan-in is the maximum number of inputs to a gate. Although physical considerations limit fan - in, more pragmatic factors, such as limitations on the number of pins possible on IC packages and their standardization predominate. TTL NAND gates typically provide 1, 2, 4, or 8 inputs. If more than eight inputs are required, then a network of NAND gates must be employed Fan -out specifies the number of standard loads that the output of a gate can drive without impairing its normal operation. A standard load is defined to be the amount of current required to drive an input of another gate in the same logic family. A voltage transfer curve is a graph of the input voltage to a gate versus its output voltage; when the input voltage is 0 V, the output is HIGH at 3.3 V. As the input voltage is increased from 0 to 0.7 V, the output remains relatively constant (Region I). Beyond 0.7 V to about 1.2 V, the output decreases more gradually with increasing input voltage (Region II). The threshold voltage, the voltage on the transfer curve at which Vout= Vin and occurs in Region III, is found at the intersection of the transfer curve and the line Vout= Vin. Finally, in Region IV, the output remains constant at 0.2 V as the input voltage is increased. Noise immunity is a measure of the ability of a digital circuit to avert logic level changes on signal lines when noise causes voltage level changes. 55 Number System and Logic Families The propagation delay time for a gate is the time required for the output to respond to a change in an input. In all practical gates, a time lag exists between an input change and the corresponding output response. The time interval between the instants when the input and output change states are not a satisfactory measure of the delay time of a logical device for two reasons. First, the input signals to gates and the output signals produced by gates are not the idealized pulses studied in theory. TTL gates are available in three different types of output configurations. Totem - pole output gates are used in most logic; in this case, the gate by itself drives its output HIGH or LOW depending on the gate’s inputs. Connecting the outputs of two or more totem -pole gates together produces undefined output values, may damage the device and should never be done. Open - collector output gates can only drive their output LOW; for input combinations where the output should be HIGH, an external pullup resistor connected the supply voltage is needed to produce the HIGH. The outputs of open - collector gates to be wired together; the result is to effectively AND all the output signals together. Three - state (or tri – state) output gates provide, as their name implies, three output states. Like totem -pole output gates, tri - state gates can drive their output either HIGH or LOW, as determined by the input combination, but they also have a control input that overrides the effect of the other inputs and places the gate output in a ‘third state’. In the third state the internal transistors of the gate are effectively disconnected from the gate output and the output is in an open circuit or high - impedance state. This allows a direct wire connection of many tri - state gate outputs to a common line; however, when this is done, all but at most one of the tri - state output gates connected together must be in the high - impedance state at any given time. CMOS CMOS logic is exemplified by its extremely low power consumption and high noise immunity. Hence, it is prevalently used in devices demanding low power dissipation, such as digital wristwatches and other battery powered devices, or in devices operated in noisy environments, such as industrial plants. A wide variety of CMOS logic devices in the 4000 series are available. Unlike TTL logic, CMOS logic requires two supply voltages, VDD and VSS. In typical logical designs, VDD ranges from +3 V to +16V. The other supply, VSS, is normally grounded. Also, the physical representation of the binary states in CMOS logic is not entirely compatible with TTL logic. As a consequence of CMOS's extremely high input impedance, the logic levin CMOS systems are essentially VDD and ground. If, for example, a 5 volt power supply is used, LOW typically ranges from 0 to 0.01 V and HIGH from 4.99 to 5.0 V for 56 Number System and Logic Families CMOS outputs. Input voltages ranging from 3.5 to 5 V are recognized as HIGH and voltages from 0 to 1.5 V as LOW. It may appear that CMOS output logic levels, using a 5 V power supply, completely conform to the TTL logic level ranges of 0 to 0.8 V for LOW and 2.0 to 5.5 V for HIGH. However, the voltage level ranges representing HIGH and LOW are not the only factors that determine whether two logic family are compatible or not. The amount of current that can be supplied by outputs and that can be assimilated by inputs of gates within each logic family is another consideration. Specifically, when CMOS drives TTL logic, the crucial question is whether the CMOS output, in the LOW state, can sink enough of the current originating at the TTL input to ensure that the voltage at the TTL input does not exceed its maximum LOW level input voltage of 0.8 V. Typical CMOS gates can sink about 0.4 mA in the LOW state while maintaining an output voltage of 0.4 V or less. This is sufficient to drive two lowpower TTL inputs, but generally insufficient to drive even one standard TTL input. In any case, loss of dc noise immunity is an inevitable result. It is better to use a special buffer such as a 74C901 to drive standard TTL from CMOS. The HIGH state poses no problems. Similarly, improper circuit operation may result from connecting TTL outputs to CMOS inputs. In the LOW state, a TTL output can drive CMOS directly. However, the guaranteed TTL HIGH output level of 2.4 volts is not a valid input level for CMOS. If the TTL output drives only CMOS inputs, then essentially no current is drawn and the HIGH output may be 3.5 V or higher. (A pull-up resistor to +5 can be connected to the gate output to assure that the output is above 3.5V.) CMOS CHARACTERISTICS The voltage transfer curve - curves in the transition region are almost vertical. This narrow transition region is the reason for CMOS logic's high noise immunity. Not much voltage range is covered in the transition from one state to the other. In contrast to TTL devices, the threshold voltage depends on the supply voltage and is approximately half the supply voltage. As with TTL logic, current spiking occurs during switching. Hence, bypass capacitors are used in CMOS logic design as well. However, they are not as critical as in TTL logic design because of CMOS's high noise immunity. Whereas the typical quiescent (static) power dissipation (power dissipation of a device that is not changing logic states) of TTL IC's was about 40 mW, the power dissipation of CMOS IC's are typically 25 nW. However, as the frequency of switching increases, The input impedance, in either state, of CMOS gates is typically 1012 Ω. The input capacitance is 5 pF. The output impedance depends on the particular device, and is on the order of 1 kΩ, for either state. 57 Number System and Logic Families The propagation delay times for CMOS devices are relatively long due to their high output impedance. Typical delay times are 60 nsec for VDD= 5 V, and 25 nsec for VDD= 10 V. Doubling the supply voltage more than doubles the speed of a CMOS gate. The rise and fall transition times are typically 70 nsec. For VDD= 5V. Thus CMOS devices operate significantly slower than TTL devices Floating inputs in CMOS logic guarantee neither LOW nor HIGH outputs and cause increased susceptibility to noise, as well as excessive power dissipation. Hence, all unused inputs should be connected to VDD or VSS, as appropriate The fan-out of CMOS devices is usually greater than 50 because the input current requirement of CMOS logic is nil (∼pA). However, current is required to charge and discharge the capacitance of CMOS inputs during logic transitions. Hence, the greater the fan-out the longer the propagation delays. 58