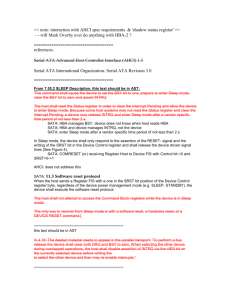

Command Completion (4

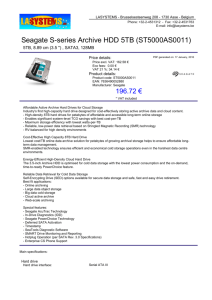

advertisement

T13/f10137r1 ATA8-AST Section 4.3 Replacement Text for ATA8-AST section 4.3 Nov. 23, 2010 Revision 1 Technical Editor: Jim Hatfield 389 Disc Device Longmont, CO 80503 USA 720-684-2120 James.C.Hatfield@seagate.com Seagate/Jim Hatfield Page 1 of 6 Nov. 23, 2010 T13/f10137r1 ATA8-AST Section 4.3 Document Status Revision History Rev Date 0 Aug. 10, 2010 1) Initial draft 1 Nov. 23, 2010 1) Applied comments from August 2010 plenary Seagate/Jim Hatfield Description Page 2 of 6 Nov. 23, 2010 T13/f10137r1 1 ATA8-AST Section 4.3 Introduction When ATA/ATAPI-7 was converted into ATA8-ACS, the editor removed some transport-specific requirements, with the intention that they would be moved to ATA8-APT and ATA8-AST. 2 Scope These are additions or replacements to sections of ATA8-AST to restore the material removed from ATA8-ACS. 3 Changes to ATA8-AST [editors note: Modify these definitions in Clause 3] 3.1.a Command Aborted A response by a device reporting that a command was aborted (see 4.3.2.1). 3.1.b Command Acceptance A response by a device reporting that a command has benn accepted (see 4.3.2.2). 3.1.c Command Completion A response by a device reporting that a command has completed (see 4.3.2.3). Seagate/Jim Hatfield Page 3 of 6 Nov. 23, 2010 T13/f10137r1 ATA8-AST Section 4.3 [editors note: the following replaces section 4.3 of the draft ATA8-AST] 4.3 AST specific ACS-2 Transport Dependent responses 4.3.1 Parallel ATA Emulation In an ATA8-APT device, the ACS-2 fields (e.g., Device, Count, LBA) are implemented as registers within the device. In an ATA8-AST device, the ACS-2 fields (e.g., Device, Count, LBA) are implemented in the host bus adapter as shadow registers. The content of those shadow registers are transmitted between the host and device using FIS data structures. The SATA specification [SATA] uses multiple terms when referencing shadow registers in a host bus adapter (e.g., Shadow Register Block, Shadow Taskfile, or Shadow Command Block). The Parallel ATA Emulation mode is defined in [SATA]. 4.3.2 SATA Definition Details 4.3.2.1Command Aborted An ATA8-AST device reports command aborted by transmitting a Register Device to Host FIS, a PIO Setup FIS, or a Set Device Bits FIS, with: a) BSY bit (see 4.3.2.1) cleared to zero; b) DRQ bit (see 4.3.2.3) cleared to zero; and c) Check Condition (see ACS2) bit set to one or the Error bit (see ACS2) set to one. 4.3.2.2Command Acceptance An ATA8-AST device reports command acceptance by transmitting a Register Device to Host FIS, with: a) BSY bit (see 4.3.2.1) cleared to zero; b) DRQ bit (see 4.3.2.3) cleared to zero; and c) Check Condition (see ACS2) bit set to one or the Error bit (see ACS2) set to one. 4.3.2.3Command Completion An ATA8-AST device reports command completion for commands not in the NCQ feature set by transmitting a Register Device to Host FIS or a PIO Setup FIS, with: a) BSY bit (see 4.3.2.1) cleared to zero; and b) DRQ bit (see 4.3.2.3) cleared to zero. An ATA8-AST device reports command completion for commands in the NCQ feature set by transmitting a Set Device Bits FIS, with bits in DWord 1 set to one for each NCQ command that has completed. 4.3.3 Transport Specific Status Field Bits 4.3.3.1Bit 7 - Busy (BSY) The use of the BSY bit is defined in [SATA]. When the host reads the BSY bit, it is reading the last value that Status field bit 7 had when the device sent a FIS to the host. The host does not directly read BSY from the device. Seagate/Jim Hatfield Page 4 of 6 Nov. 23, 2010 T13/f10137r1 ATA8-AST Section 4.3 4.3.3.2Bit 6 - Device Ready (DRDY) The DRDY bit shall be cleared to zero by the device if: 1) the device processes a power-on reset; 2) the device processes a hardware reset; 3) the device processes a software reset; or 4) an ATAPI device processes: a. a DEVICE RESET command; or b. a DEVICE DIAGNOSTIC command. The DRDY bit shall be set to one: 1) by an ATA device, when it is capable of accepting all commands; and 2) by an ATAPI device prior to command completion except the DEVICE RESET or EXECUTE DEVICE DIAGNOSTIC command for devices implementing the PACKET feature set. If the DRDY bit is cleared to zero, then the device shall accept and attempt to process commands. If the DRDY bit is set to one, then: 1) the device shall accept and attempt to process all implemented commands; and 2) a device that implements the Power Management feature set shall set the DRDY bit set to one when the device is in the PM1:Idle state or the PM2:Standby state (see ACS2). 4.3.3.3Bit 3 - Data Request (DRQ) The use of the DRQ bit is defined in [SATA]. When the host reads the DRQ bit, it is reading the last value that Status field bit 3 had when the device sent a FIS to the host. The host does not directly read DRQ from the device. 4.3.4 Transport Specific Error Field Bits 4.3.4.1Bit 7 - Interface CRC (ICRC) The use of the ICRC bit is defined in [SATA]. 4.3.5 Transport Specific Device Control Field Bits 4.3.5.1Bit 7 - High Order Byte (HOB) The HOB bit is not used by SATA devices. 4.3.5.2Bit 2 - Software Reset (SRST) The use of the SRST bit is defined in [SATA]. 4.3.5.3Bit 1 - Enable INTRQ Interrupt (nIEN) The nIEN bit is not used by SATA devices Seagate/Jim Hatfield Page 5 of 6 Nov. 23, 2010 T13/f10137r1 ATA8-AST Section 4.3 4.3.6 Transport Specific Device Field Bits 4.3.6.1Bit 4 - Device Selection (DEV) The use of the DEV bit is defined in [SATA]. 4.3.7 SLEEP command and PM3:Sleep state As a result of processing the SLEEP command (see ACS2), the device shall: a) report command completion; and b) enter the PM3:Sleep power management state (see ACS2) after a vendor specific time period of not less than 2 seconds after command acceptance. If the device is in the PM3:Sleep state, then: a) if the device detects COMRESET, regardless of the current software settings preservation setting, then the device shall process the hardware reset protocol (see ACS2 and AAM); and b) For an ATA8-AST device, there is no specified way to exit the PM3:Sleep state using the software reset protocol or using the DEVICE RESET command. 4.3.8 Software reset If an ATA8-AST device: 1) receives a Register Host to Device FIS with a) the C bit of the Device Control field set to one (see SATA); and b) the SRST bit set to one in the Device Control register field, then the device shall begin processing the software reset protocol regardless of the device power management state (e.g., PM2:Standby) (see ACS2); and 2) receives a Register Host to Device FIS with a) the C bit of the Device Control field set to one (see SATA); and b) the SRST bit cleared to zero in the Device Control register field, then the device shall complete the software reset protocol. 4.3.9 Transport Specific Resets 4.3.9.1COMRESET The use of COMRESET is defined in [SATA]. It is similar, but not identical to, Hardware Reset (see AAM). Seagate/Jim Hatfield Page 6 of 6 Nov. 23, 2010