Tutorial

advertisement

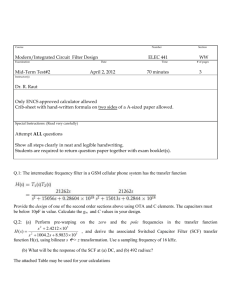

Laboratory 4: High-pass IIR Filter Design I. Introduction In the present project, students are required to implement and simulate a high-pass IIR filter using DSP Builder in the Simulink environment. The design has to be downloaded to the FPGA device on the Stratix II EP2S60 DSP development board to perform hardware simulation and verification. II. Theory An IIR (Infinite Impulse Response) filter, oppositely to FIR filters, has an infinite response to impulse signals, which is explained because it has feedback. Equation (1) describes an IIR filter: N 1 M 1 k 1 k 0 yn a k yn k bk xn k (1) Where: x and y represent the input and output data, respectively. bk is the set of the M feedforward filter coefficients, applied to the input signal samples. a k is the set of the N feedback filter coefficients (if we include a 0 1 ), applied to the previous output samples. M 1 is the feedforward filter order. N 1 is the feedback filter order. The transfer function H (z ) of the IIR filter is expressed as follows: M 1 H ( z) Y ( z ) B( z ) X ( z ) A( z ) bk z k k 0 N 1 1 ak z (2) k k 1 IIR filters can be used in applications that require sharp cut-off or narrow band filters and where linear phase is not a requirement. That is because IIR filters require much lower order implementations than FIR filters for a similar performance. III. Background about DSP Builder and the Altera EP2S60 DSP development board Capabilities of DSP Builder and Simulink were introduced with an example design in the Tutorial: “A/D and D/A Conversion on Altera Stratix II EP2S60 Development Board using Simulink and DSP Builder” [1], which contain a design targeting the 12-bit 125MHz A/D and 14-bit 165 MHz D/A converters onboard. For further information about the Stratix II EP2S60 DSP development board, the student is referred to [2],[3] and [4]. IV. Requirements For this laboratory, students are required to accomplish the next requirements: Design a high-pass IIR filter using the Direct-form II Transposed, with stop-band at 0.05 x FN (where FN is the Nyquist frequency, or half the sampling rate), and using Chebyshev type II method. The transposed structure is the combination of two FIR filters where one is used as a feed forward filter and the other is used as a feedback filter, as shown in the following graph: filtre FIR, coeffs. bk filtre FIR coeffs. ak One advantage of this structure is that delay elements can be shared by both FIR filters, allowing some savings in terms of hardware requirements. To determine the floating-point coefficients use the Matlab command cheby2 with the next specifications: Type: Filter order: Stop-band frequency: Min. attenuation stop-band: high-pass 4 0.05 x FN 30dB Use fdatool from Matlab to verify that the designed filter fulfills the previous specifications. Import the filter (File > Import filter from Workspace). Select ‘Direct-Form II Transposed’ from the drop down menu in Filter Structure and then type the variables names that contain the coefficients in the ‘Numerator’ and ‘Denominator’ fields. In the ‘Units’ field, ‘Normalized (0 to 1)’ has to be select from the drop down menu below Sampling Frequency. Then, click Import Filter, and now you can check the frequency response of the floating-point IIR filter. (Note: you can also directly use freqz in Matlab to observe the frequency response). Verify if the filter response meets the specifications. Which filter order is required if we instead use an FIR filter with similar specifications? Comment the differences. (For the FIR filter, use a direct form filter, Equiripple type, with stopband up to normalised frequency 0.05, and passband starting at normalised frequency 0.1). Obtain a fixed point version of the coefficients bk and ak of the IIR filter by using the Matlab function fi on each set of coefficients. This will produce output values for bk and ak expressed in 16 bits fixed point format, with some bits assigned to an integer part and some bits assigned to a fractional part (unlike the approach from the previous lab #3, where the fixed point coefficients were only using integer values). Determine the integer and fraction lengths of the new coefficients. Use the following synthax as an example: b2=fi(b) b2=b2.data where "b" would represent the variable containing the floating point bk. coefficients, and "b2" would represent the new fixed point coefficients. The coefficients obtained using fi will be used to design the fixed-point version of the filter. NOTE: the number of bits assigned to integer and fractional parts should be used in setting the parameters of the Gain blocks in your mdl files, in which the “Bus Type” option should be set as “Signed Fractional”. Check if the new fixed-point coefficients fulfill the filter specifications by importing them to fdatool as described previously. Check the frequency response of the fixed-point IIR filter, analyze if it adjusts to the requirements and compare it with the frequency response obtained from the floating-point design. Implement the Direct-form II Transposed IIR filter in Simulink (DSP Builder) using the fixed-point coefficients and the A/D and D/A converters onboard. You can use the design given in the Tutorial [1] as a template, operating at 100 MHz. The A/D converter must convert a sinusoidal signal to digital, filter it and finally convert it back to analog through the D/A converter. Place a SignalTap II node at the output of the filter to acquire the signal later (see Figure 1, Tutorial [1]). A reference design from Simulink can be obtained very easily by means of fdatool. First, export the fixed-point filter obtained in previous steps from fdatool to Simulink by clicking File > Export to Simulink Model. In the ‘Destination’ field select ‘New’, and leave the other options by default. Click on Realize Model and a new Simulink window will open with the filter. Double click on the filter block and the filter with the Direct-form II Transposed structure will appear. You can follow the general structure of this design to implement your filter using DSPBuilder blocks. NOTE: the filter designed with fdatool uses Simulink blocks. You must carefully replace Simulink blocks by DSPBuilder components in a new window. Also, be aware of formatting differences, especially to specify buses. A Simulink model fixes the buses formats automatically, whereas a hardware-oriented library as DSPBuilder needs the designer to define, when necessary, the format and size of buses. Also, be careful when applying pipelining techniques, which are not considered in the Simulink version. It is suggested that the Display Block from the Sinks of the Simulink library be used to measure the values after each Gain block, Adder block as well as the output, for the process of determining the settings of the AltBus block and the number of Pipeline Levels in the Gain block. One tip for this tedious but important process: use a Constant block (e.g. with value 1) as the filter input, and set the Stop time in the “Configuration parameters...” under “Simulation” tab at 1*10e-9 (one clock cycle of 100MHz), so that you can check if the values after each Gain block and adder block are correct. Simulate your filter in Simulink with different sinusoidal signals from 100KHz to 5MHz, observing at which frequencies the amplitude of the signal drops significantly. Download your design to the Stratix II EP2S60 DSP development board and test it by using a signal generator and oscilloscope. Capture and analyze the data using SignalTap II Analysis. Show when the amplitude of the signals drops significantly. Also, using the data acquired through SignalTap II, show the frequency content, choosing one input signal frequency in pass-band and another in stop-band. NOTE: you can use similar commands to those given in the Tutorial [1], “Importing the data acquired from the board in Matlab workspace”, step2. The next part of the project involves to design the same high-pass IIR but this time using the Direct-form II Transposed – Second Order Sections (SOS) structure. The aim is to compare this against the traditional transposed form and to determine which method provides the best performance for hardware implementation. Transform the Direct-form II Transposed structure (floating point version, previously obtained) to SOS by using the Matlab command tf2sos. This command gives the SOS matrix and the factor G, which characterize the new IIR filter: [SOS,G] = tf2sos(b,a) Use fdatool from Matlab to verify that the new filter structure fulfills the required specifications in floating-point format. File > Import Filter from Workspace permits to analyze the floating-point design. First, select ‘Direct-Form II Transposed’ from the drop down menu in Filter Structure, check the box ‘Import as second-order sections’, and then type the variables names that contain the SOS matrix and the factor G in the ‘SOS Matrix’ and ‘Gain’ fields, respectively. In the ‘Units’ field, ‘Normalized (0 to 1)’ has to be select from the drop down menu below Sampling Frequency. Then, click Import Filter, and now you can check the frequency response of the floating-point IIR filter. Using the Matlab command fi as before, convert to fixed point the coefficients of the IIR filter with SOS structure, and determine the integer and fraction lengths of the new 16 bits fixed point coefficients. These fixed-point values will be used to design the filter in Simulink. SOS=fi(SOS) SOS=SOS.data G=fi(G) G=G.data Check if the new fixed-point coefficients fulfill the filter specifications by importing them to fdatool as described previously. Check the frequency response of the fixed-point IIR filter, analyze if it adjusts to the requirements and compare it with the frequency response obtained from the floating-point design. Also, compare it against the fixed-point Direct-form II Transposed structure. Which filter form offer the best filter performance? Why? Implement the Direct-form II Transposed SOS IIR filter in Simulink (DSP Builder) using the fixed-point coefficients and the A/D and D/A converters onboard. The A/D converter must convert a sinusoidal signal to digital, filter it and finally convert it back to analog through the D/A converter. Place a SignalTap II node at the output of the filter. Again, a reference design can be obtained easily by means of fdatool. First, export the fixed-point filter obtained in previous steps to Simulink by clicking File > Export to Simulink Model. In the ‘Destination’ field select New, and leave the other options by default. Click on Realize Model and a new Simulink window will open with the filter. Double click on the filter block and the filter with the Direct-form II Transposed SOS structure will appear. You can follow the general structure of this design to implement your filter using DSPBuilder blocks. NOTE: observe the same recommendations given for the DSPBuilder implementation of the Transposed structure, in the previous section. Simulate your filter in Simulink with different sinusoidal signals from 100KHz to 5MHz, observing at which frequencies the amplitude of the signal drops significantly. Download your design to the Stratix II EP2S60 DSP development board and test it by using a signal generator and oscilloscope. Capture and analyze the data using SignalTap II Analysis. Show when the amplitude of the signals drops significantly. Also, using the data acquired through SignalTap II, show the frequency content, choosing one input signal frequency in pass-band and another in stop-band. Validate the theoretical comparison between Transposed and Transposed SOS structures using the results of your tests onboard. V. Submission You must submit: The Simulink models (.mdl) developed using DSP Builder blocks with the two IIR structures: Direct-form II Transposed and Direct-form II Transposed SOS. A report describing the general procedure to accomplish the project requirements, and answering questions regarding filtering and structure comparisons as detailed in the requirements. The report must contain graphs showing the filtered signals and frequency content. VI. References [1] Tutorial: “A/D and D/A Conversion on Altera Stratix II EP2S60 Development Board using Simulink and DSP Builder”. [2] DSP Builder User Guide, ver. 5.1.0, c:\altera\61\DSPBuilder\Doc\ug_dspbuilder.pdf Altera, 2005. Local copy at: [3] Stratix II EP2S60 DSP Development Board Data Sheet, Altera. Available online at: www.altera.com/literature/ds/ds_stratixII_dsp_dev_board.pdf [4] DSP Development Kit Stratix II Edition (Getting Started User Guide), 1.1.0. v., Altera, 2005. Available online at: www.altera.com/literature/ug/ug_stratixII_dsp_dev_kit.pdf