Semidynamic Flip-Flops with skew tolerance

advertisement

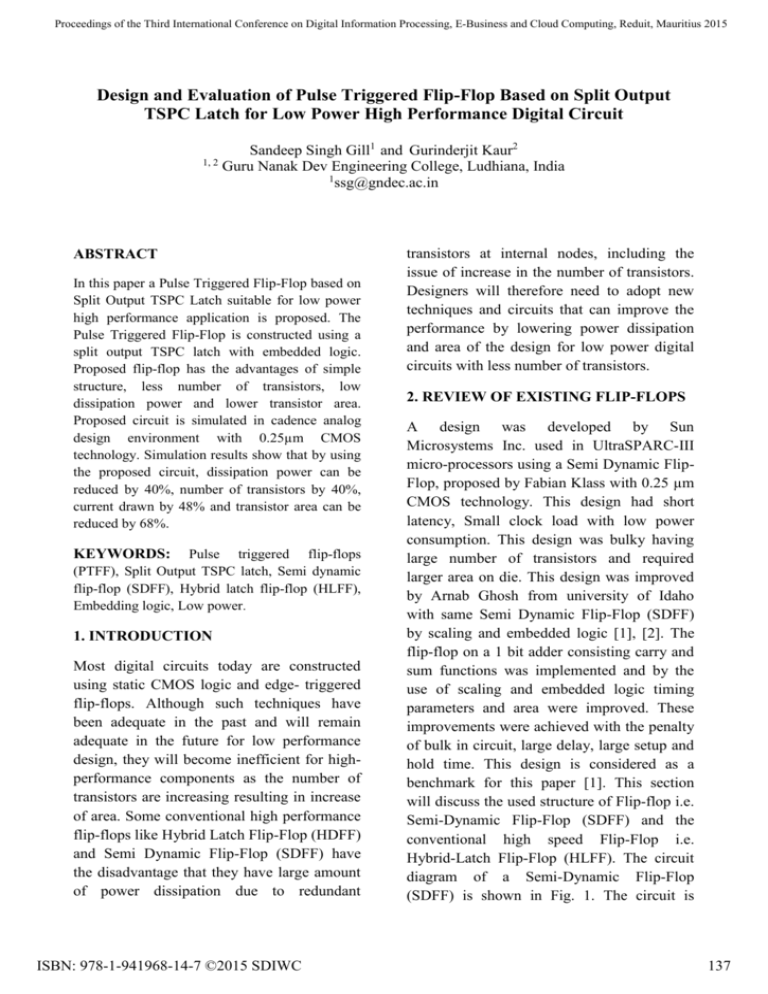

Proceedings of the Third International Conference on Digital Information Processing, E-Business and Cloud Computing, Reduit, Mauritius 2015 Design and Evaluation of Pulse Triggered Flip-Flop Based on Split Output TSPC Latch for Low Power High Performance Digital Circuit Sandeep Singh Gill1 and Gurinderjit Kaur2 1, 2 Guru Nanak Dev Engineering College, Ludhiana, India 1 ssg@gndec.ac.in ABSTRACT In this paper a Pulse Triggered Flip-Flop based on Split Output TSPC Latch suitable for low power high performance application is proposed. The Pulse Triggered Flip-Flop is constructed using a split output TSPC latch with embedded logic. Proposed flip-flop has the advantages of simple structure, less number of transistors, low dissipation power and lower transistor area. Proposed circuit is simulated in cadence analog design environment with 0.25µm CMOS technology. Simulation results show that by using the proposed circuit, dissipation power can be reduced by 40%, number of transistors by 40%, current drawn by 48% and transistor area can be reduced by 68%. KEYWORDS: Pulse triggered flip-flops (PTFF), Split Output TSPC latch, Semi dynamic flip-flop (SDFF), Hybrid latch flip-flop (HLFF), Embedding logic, Low power. 1. INTRODUCTION Most digital circuits today are constructed using static CMOS logic and edge- triggered flip-flops. Although such techniques have been adequate in the past and will remain adequate in the future for low performance design, they will become inefficient for highperformance components as the number of transistors are increasing resulting in increase of area. Some conventional high performance flip-flops like Hybrid Latch Flip-Flop (HDFF) and Semi Dynamic Flip-Flop (SDFF) have the disadvantage that they have large amount of power dissipation due to redundant ISBN: 978-1-941968-14-7 ©2015 SDIWC transistors at internal nodes, including the issue of increase in the number of transistors. Designers will therefore need to adopt new techniques and circuits that can improve the performance by lowering power dissipation and area of the design for low power digital circuits with less number of transistors. 2. REVIEW OF EXISTING FLIP-FLOPS A design was developed by Sun Microsystems Inc. used in UltraSPARC-III micro-processors using a Semi Dynamic FlipFlop, proposed by Fabian Klass with 0.25 µm CMOS technology. This design had short latency, Small clock load with low power consumption. This design was bulky having large number of transistors and required larger area on die. This design was improved by Arnab Ghosh from university of Idaho with same Semi Dynamic Flip-Flop (SDFF) by scaling and embedded logic [1], [2]. The flip-flop on a 1 bit adder consisting carry and sum functions was implemented and by the use of scaling and embedded logic timing parameters and area were improved. These improvements were achieved with the penalty of bulk in circuit, large delay, large setup and hold time. This design is considered as a benchmark for this paper [1]. This section will discuss the used structure of Flip-flop i.e. Semi-Dynamic Flip-Flop (SDFF) and the conventional high speed Flip-Flop i.e. Hybrid-Latch Flip-Flop (HLFF). The circuit diagram of a Semi-Dynamic Flip-Flop (SDFF) is shown in Fig. 1. The circuit is 137 Proceedings of the Third International Conference on Digital Information Processing, E-Business and Cloud Computing, Reduit, Mauritius 2015 faster than TSPC but still has some shortcomings. First, internal node X is truly dynamic, i.e. it is not actively driven by any device during most of the evaluation phase. Second, output Q is high impedance when the clock signal is low. The circuit is composed of a dynamic front-end and a static back-end. The flop samples input D and produces output QB, which is the logic complement of D. The circuit operates as follows. On the falling edge of clock CLK, the flop enters the precharge phase. Fig.1. Semi Dynamic Flip-Flop (SDFF) Node X is precharged high, cutting off node Q from the input stage. The evaluation phase begins with the rising edge of clock CLK. If input D is low, node X would remain high. Node Q would either remain low or will be discharged through transistors. The circuit diagram of Hybrid Latch Flip-Flop is shown in Fig.2. having negative setup time in generating pulse which gives small D-Q delay. It also has small logic-embedding with small penalty. As mentioned earlier this Flip-flop has the disadvantage of large amount of power dissipation [3-13]. 3. PROPOSED FLIP-FLOP To overcome the disadvantages of Design using Semi Dynamic Flip-Flop and Conventional high speed flip flops we proposed a Pulse Triggered Flip- Flop based on split output TSPC latch. It has a simpler structure composed of five transistors and back to back inverters. It is a positive latch if it is triggered by the rising edge of the clock. Back to back inverters enhance the robustness of its output operation. Proposed flip-flop can reduce the power dissipation, current drawn, transistor count, total transistor width and estimated transistor area. Fig.3 Shows the Circuit diagram of Pulse Triggered Flip-Flop based on split output TSPC latch. In proposed circuit clock is applied to pull up circuit to fulfill the need to have a mirror circuit of pull down to implement the embedded logic. Clock is also applied to NMOS at the middle to trigger the circuit, data is applied to pull down circuit. Fig.2. Hybrid Latch Flip-Flop (HLFF) The circuit of Hybrid Latch Flip-Flop consists of two stages: the front end function as pulse generator and the back end is to capture the pulse as a latch. It has the advantage of ISBN: 978-1-941968-14-7 ©2015 SDIWC Fig.3. PTFF based on Split output TSPC latch This circuit will also avoid bulk in the design as compared to Semi Dynamic Flip-Flops (SDFF) as it do not consists of any redundant 138 Proceedings of the Third International Conference on Digital Information Processing, E-Business and Cloud Computing, Reduit, Mauritius 2015 transistors at internal node. An inverted clock is applied to PMOS connected at X and Y node to remove the potential difference between both the nodes. This gate here behaves like a pass gate. At the back end we have cross coupled inverters which is a basic storing element also, it increases the robustness of the circuit. In this cross coupled inverters, width of feedback inverter should be greater than the width of feed through inverter. 4. EMBEDDING LOGIC FUNCTION Fig.4. PTFF based on split output TSPC latch with embedded logic Embedding logic function is an important technique using which we can easily incorporate most logic functions into flop, such as wide OR functions, multiplexers and complex gates. Fig.4. shows the Pulse Triggered Flip-Flop based on split output TSPC latch with embedded Sum and Carry functions. It will reduce the number of combinational stages and clock cycles, which will provide high throughput of the design. 5. SIMULATION RESULTS In this experiment we implemented the design of 1-bit registered adder having sum and carry function using Semi Dynamic Flip-flop [1] discussed in this paper and the proposed Pulse Triggered Flip-flop based on split output TSPC latch. We also simulated and analyzed ISBN: 978-1-941968-14-7 ©2015 SDIWC both the designs using Cadence analog design environment. We compare the transistor count, total transistor width, estimated transistor area, current drawn, power dissipation, C-Q, C-Q̅̅ , D-Q. D-Q̅̅, Set up and hold times and transparency pulse width of circuit. The experiment conditions are shown in Table.1. Simulation results are shown in Table.2 to Table.10. In this experiment all the flip-flops have the same data rate and all transistor sizes are optimized to achieve the desired results. The rise time and fall time of the input signal are 100ps. We can see that Transistor count of the proposed flip-flop is 15, with embedded logic it consists of 19 transistors and for 1 bit registered full adder transistor count is 90 in Table.2. In Table.3, we compare the Total Transistor Width which is 116.04µm for 1-bit registered full adder. We also compare Estimated Transistor Area which is 172.203µm2 for proposed circuit and 250.901µm2 for benchmark [1] in Table.4. In Table.5 transparency pulse width is given, which is 205ps and 180ps for Semi Dynamic Flip-Flip (SDFF) and Pulse Triggered FlipFlop Based on split output TSPC latch respectively. In Table.6 we compare the Set up and Hold time of the proposed and benchmark [1]. We can see at the fall edge the C-Q for benchmark circuit is 120.3ps and for the proposed circuit it is 189.3ps, at the rise edge the C-Q for benchmark circuit is 276.5ps and for the proposed circuit it is 215ps given in Table.7. In Table.8 we can see at fall edge the D-Q for benchmark circuit is146ps and for the proposed circuit it is 207.9ps, at the rise edge the D-Q for benchmark circuit is 293.1ps and for the proposed circuit it is 228.3ps. Table.9 shows the comparison between Current drawn of both the designs which is 0.7nA and 0.23nA for benchmark and the proposed circuit respectively. Power dissipation is also compared in Table.10 139 Proceedings of the Third International Conference on Digital Information Processing, E-Business and Cloud Computing, Reduit, Mauritius 2015 which is 1.4nW for benchmark circuit and 0.445nW for the proposed circuit. Table 4. Estimated Transistor Area Table 1. Experiment Conditions Circuit Design Specification Technology MOSFET Model Benchmark Proposed Work 0.25um TSMC deep submicron 0.25um Nominal 2V 25 degree C Conditions Supply Voltage Temperature Rise time of 100ps input signal Fall time of 100ps input signal Clock frequency 100 MHz Clock duty 50% cycle Delay Between 50% calculations points 0.25um TSMC deep submicron 0.25um Nominal 2V 25 degree C Flip-Flop Flip-Flop with embedded logic 1-bit registered full adder Benchmark design (µm2) 38.115 Proposed design (µm2) 23.607 53.615 35.480 250.901 172.203 100ps 100ps Table 5. Transparency Pulse Width of the Circuit 100 MHz 50% Circuit Between 50% points Flip-Flop Flip-Flop with embedded logic Benchmark design (ps) 193 Proposed design (ps) 180 205 180 Table 2. Transistor Count Transistor count Circuit Flip-Flop Flip-Flop with embedded logic 1-bit registered full adder Table 6. Set up and Hold times Benchmark 23 Proposed 15 Circuit 27 227 19 90 Table 3. Total Transistor Width Circuit Flip-Flop Flip-Flop with embedded logic 1-bit registered full adder 25.695 Proposed design (µm) 15.9 35.995 23.82 168.39 116.04 Benchmark design (µm) ISBN: 978-1-941968-14-7 ©2015 SDIWC Setup time Flip-Flop Flip-Flop with embedded logic Hold time Flip-Flop Flip-Flop with embedded logic Benchmark design Virtual Real (ps) (ps) Proposed design Virtual Real (ps) (ps) -55 237 -58.82 210.3 -30 263 -55.05 223.8 160.3 -133 179 -90 160 -133 126 -154 140 Proceedings of the Third International Conference on Digital Information Processing, E-Business and Cloud Computing, Reduit, Mauritius 2015 Table 7. Comparison of C-Q Clk – Q (ps) (LH) (HL) Benchmark design Flip-Flop 253.5 118 Flip-Flop with 276.5 120.3 embedded logic Proposed design Flip-Flop 226.6 147 Flip-Flop with 215 189.3 embedded logic Circuit Table 10. Power Dissipation Clk – (ps) (LH) (HL) 190.2 305.1 190.1 330 231.5 283.1 280 272.7 Table 8. Comparison of D-Q D – Q (ps) (LH) (HL) Benchmark design Flip-Flop 250.5 220.9 Flip-Flop with 293.1 146 embedded logic Proposed design Flip-Flop 210.8 207.2 Flip-Flop with 228.5 207.9 embedded logic Circuit – (ps) (LH) (HL) 291.4 299.8 231.7 344.7 301.6 266.1 299.9 283.6 Circuit Flip-Flop Flip-Flop with embedded logic 1-bit registered full adder Benchmark design (nW) 1.4 Proposed design (nW) 0.445 1.4 0.456 11.7 4.63 CONCLUSION A Design using Pulse triggered Flip-Flop based on split output TSPC latch is proposed and simulated in a 0.25µm process. Our simulation results justify our analysis that we reduced power dissipation by 40%, transistor area by 68%, transistor count by 40% and current drawn by 48% without affecting the high performance of the circuit. ACKNOWLEDGEMENT The authors thank Guru Nanak Dev Engineering College, Gill Road, Ludhiana, for technical support for implementation and simulation. Table 9. Current Drawn REFERENCES Circuit Flip-Flop Flip-Flop with embedded logic 1-bit registered full adder Benchmark design (nA) 0.7 Proposed design (nA) 0.23 0.7 0.23 6.1 2.1 [1]. A. Ghosh, “Evaluation of semi dynamic flip-flops for low power, High performance Circuits,” University of Idaho: MS Dissertation, 2000. [2]. F. Klass, “Semi-Dynamic and dynamic Flip-Flops with embedded Logic,” Digest of Technical Papers, IEEE Symposium on VLSI Circuits, Honolulu, HI, USA, pp 108-109, June 1998. [3]. F. Klass, C. Amir, A. Das, K. Aingaran, C. Truong, R. Wang, A. Mehta, R. Heald, and G. Yee, “A new family of semi-dynamic and Dynamic flip flops with ISBN: 978-1-941968-14-7 ©2015 SDIWC 141 Proceedings of the Third International Conference on Digital Information Processing, E-Business and Cloud Computing, Reduit, Mauritius 2015 embedded logic for high performance processors,” IEEE Journal of Solid State Circuits, vol.34, no.5, pp. 712-716, May 1999. [4]. G. Yee, “Dynamic logic design and synthesis using clock-delayed domino,” University of Washington: Ph.D. Dissertation 1990. [5]. H. Partovi, H. Partovi, R. Burd, U. Salim, F. Weber, L. DiGregorio, D. Draper, “Flow through latch and edge triggered flip-flop hybrid elements,” ISSCC, Digest of Technical Papers, pp.138-139, Feb. 1996. [6]. J.M Rabaey, “Digital Integrated circuit: A design prospective,” Prentice Hall, 1996. [7]. J.F Lin, “Low-power pulse triggered flip flop design using gated pull-up control scheme,” Department of information and communication Engineering, Chaoyang University of Technology, Taiwan, 2011. [8]. J. Kennedy, R. Eberhart, “Particle Swarm Optimization,” Proceedings of IEEE international Conference on Neural Network, vol. 4, pp. 1942-1948, Nov/Dec 1995. [9]. J.Yuan and C. Svensson, “High-speed CMOS circuit techniques,” IEEE Journal of Solid-State Circuits, vol. 24, pp. 62-70, Feb. 1989. [10]. K.Roy and S. Prasad, Low- power CMOS VLSI Circuit Design. New York: John Wiley and Sons, Inc., 2000. [11]. U. Ko, A. Hill, and P.Balsara, “Design techniques for high-performance, energy-efficient control logic,” IEEE International Symposium on Low Power Electronics and Design, pp. 97-100, Aug. 1996. [12]. V. Stojanovic, V. Oklobdzija, and R. Bajwa, “A unified approach in the analysis of latches and flipflops for low power systems” Proceedings of IEEE International Symposium on Low Power Electronics and Design, Monterery, CA, pp. 227-232, Aug. 1998. [13]. Y. Hu and R. Zhou, “Low clock swing TSPC flip flops for low power applications,” J Circuit Syst Comp., vol. 18, Issue 01, February 2009. ISBN: 978-1-941968-14-7 ©2015 SDIWC 142