VHDL

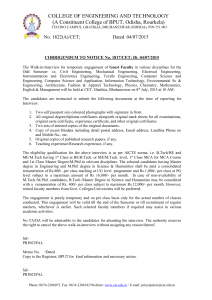

advertisement

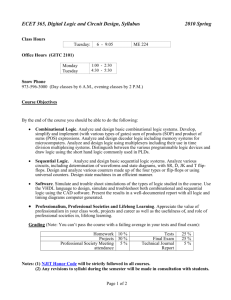

CET 486 – 586 Hardware Description Language: VHDL Introduction to hardware description languages using VHDL. Techniques for modeling and simulating small digital systems using a VHDL simulator C. Sisterna Spring 2003 ECET – CET 486 Textbooks “A VHDL Primer” by J. Bhasker, Prentice Hall, Third Edition Required text Edition. “The Designer’s Guide to VHDL” by Peter Ashenden, Morgan Kaufman. Kaufman Reference text “VHDL for Designers” by Sjoholm and Lindh. Prentice Hall Reference text Hall. “VHDL for Logic Synthesis. An introductory guide for achieving hi i D Design i R Requirements” i t ” by b A Andrew d R Rushton. ht McGraw Hill. Reference text C. Sisterna Spring 2003 ECET – CET 486 General Information P Prerequisites i it Purposes Labs Exercises Quiz Tests C. Sisterna Spring 2003 ECET – CET 486 Grading C. Sisterna Spring 2003 Quizzes 10% Mid Term Exam 20% Labs 25% Project 25% Final Exam 20% ECET – CET 486 Academic Integrity Policy • AIP: http://www asu edu/studentlife/judicial/integrity html http://www.asu.edu/studentlife/judicial/integrity.html • C Code d off C Conduct: d t http://www.asu.edu/aad/manuals/sta/sta104-01.html C. Sisterna Spring 2003 ECET – CET 486 Contact Information Cristian C i ti Si Sisterna t cristian.sisterna@asu.edu Website: www. . . C. Sisterna Spring 2003 ECET – CET 486 VHDL – Introduction Chapter I C. Sisterna Spring 2003 ECET – CET 486 VHDL - Features • Very High Hi h S Speed d IC Hardware H d D Description i ti Language L • • • • • • • The design is technologically independent Allow to design generic components Standard component p already y coded in VHDL Timing verification The designer concern is the functionality Portability: VHDL is an IEEE standard VHDL = S Sequential ti l L Language + C Concurrentt L Language + Net-List + Timing Constraints + Waveform Generation C. Sisterna Spring 2003 ECET – CET 486 VHDL – Features (cont’) • • • • Flexible design methodology: top top-down, down bottom-up bottom up It is not proprietary There is no limit for the design to be described in VHDL Allow description of delay time (minimum and maximum), hold time, setup time • Veryy short development p time • Allow different levels of abstraction (Assembler, C, C++) C. Sisterna Spring 2003 ECET – CET 486 VHDL Flow Design Synthesis y & Optimization Specifications p VHDL C Code d Place & Route Compilation Timing Verification Simulation & Verification Front-end Tools C. Sisterna Spring 2003 Back-end Tools ECET – CET 486 VHDL – General View Introduction to VHDL C. Sisterna Spring 2003 ECET – CET 486 Entity • A hardware abstraction of a Digital System is an entity • Five VHDL design units describe an entity – – – – – C. Sisterna Spring 2003 Entity declaration Architecture body Configuration declaration Package declaration Package body ECET – CET 486 Entity declaration • Describe the external view of an entity entity. The input and output signal names: --===================================================---- entity declaration syntax ---===================================================-entity tit <entity_name> i i is [generic (list_of_generics_their_types_and_value);] [port (list_of_interface_port_names_mode_and_types);] [entity_item_declaration] [begin entity_statements] end [entity] [entity_name]; C. Sisterna Spring 2003 ECET – CET 486 Architecture body • Contains the internal description of the entity --====================================================---- architecture body syntax ---====================================================-architecture <architecture_name> of <entity_name> is [architecture_declarations] begin concurrent_statements; [process_statement block_statement concurrent_procedure_call_statement t d ll t t t concurrent_assertion_statement concurrent_signal_assignment_statement component instantiation statement component_instantiation_statement generate_statement] end [architecture] [architecture_name]; C. Sisterna Spring 2003 ECET – CET 486 Example: Half-adder A B C. Sisterna Spring 2003 X1 Sum A1 Carry ECET – CET 486 Half-adder: entity declaration --================================---- Circuit: Half Adder -- Objective: example VHDL Primer" Primer -- Ref: fig 2.3 "VHDL ---===============================-entity half_adder is port( A: in bit; B: in bit; SUM: out bit; CARRY: out bit); end half_adder; C. Sisterna Spring 2003 ECET – CET 486 A B X1 Sum A1 Carry Half_adder: architecture body as a set of interconnected components STRUCTURAL ---====== structural style of modeling =====--architecture HA_STRUCTURE of HALF_ADDER is component XOR2 port (X, Y: in bit Z: out bit); A end component; component AND2 port ( p (L, , M: in bit; ; N: out bit); end component; B begin X1 XOR2 port X1: t map (A, (A B B, SUM) SUM); A1: AND2 port map (A, B, CARRY); end HA_STRUCTURE; C. Sisterna Spring 2003 ECET – CET 486 X1 Sum A1 Carry Half_adder: architecture body as a set of concurrent assignment statements DATAFLOW ---====== data flow style of modeling ======--architecture HA_DATA_FLOW of HALF_ADDER is begin SUM <= A xor B; CARRY <= A and B; end HA_CONCURRENT; A B C. Sisterna Spring 2003 ECET – CET 486 X1 Sum A1 Carry Half_adder: architecture body as a set of sequential assignment statements BEHAVOIRAL ---========= behavioral style of modeling ========--architecture HA_BEHAVIORAL_2 of HALF_ADDER is begin process (A, B) begin if (A='0' and B='0')then SUM <= '0'; CARRY <= '0'; elsif (A='1' and B='0'| A='0' and B='1')then SUM <= '1'; CARRY <= '0'; A else l -- A'1' '1' and d B='1' '1' X1 SUM <= '0'; CARRY <= '1'; end if if; end process; A1 B end HA_BEHAVIORAL_2; C. Sisterna Spring 2003 ECET – CET 486 Sum Carry Half_adder: architecture body as a mixed style --========= mixed style of modeling =========--architecture HA_BEHAVIORAL_2 of HALF_ADDER is signal SUM1: bit; component AND2 port(L, M: in bit; N: out bit); end component; begin X1: XOR2 port map (A, B, SUM1); -- structural process (A, B) -- behavior begin if (A='0' (A '0' and d B='0')then B '0')th CARRY <= '0'; elsif (A='1' and B='0'| A='0' and B='1')then CARRY <= '0'; else -- A'1' and B='1' CARRY <= '1'; end if; end process; SUM <= SUM1; -- data flow end HA_BEHAVIORAL_2; C. Sisterna Spring 2003 ECET – CET 486 Simulation Waveform Stimulus Text Device Under Results Test (DUT) Test Bench (VHDL Code) C. Sisterna Spring 2003 Waveform ECET – CET 486 Simulation Waveform Stimulus C. Sisterna Spring 2003 ECET – CET 486 Simulation C. Sisterna Spring 2003 ECET – CET 486 Simulation Test Bench a <= '1' 1 , '0' 0 after 10 ns ns, '1' after 39 ns, '0' after 110 ns, '1' after ft 145 ns, '0' after ft 155 ns; b <= '0', '1' after 30 ns, '0' after ft 49 ns, '1' after ft 90 ns, '0' after 115 ns, '1' after 135 ns; assert (a=‘1’ and b=‘1’ and sum=‘0’) report “error when a=b=‘1’ sum /= ‘0’” severity note; C. Sisterna Spring 2003 ECET – CET 486 Simulation C. Sisterna Spring 2003 ECET – CET 486 Download C. Sisterna Spring 2003 ECET – CET 486

![[#BPIDEA-13] Give the option to show `View` count by unique views](http://s3.studylib.net/store/data/007700494_2-3911615de654a0135ad82f55710606d1-300x300.png)