ECET 365 Digital Logic & Circuit Design Syllabus - NJIT

advertisement

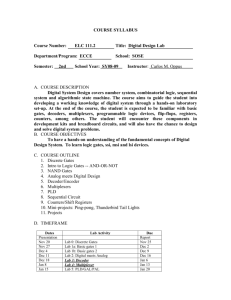

ECET 365, Digital Logic and Circuit Design, Syllabus 2010 Spring Class Hours Tuesday: 6 - 9:05 ME 224 Office Hours (GITC 2101) Monday Tuesday 1:00 - 2:30 4:30 - 5:30 Snow Phone 973-596-3000 (Day classes by 6 A.M., evening classes by 2 P.M.) Course Objectives By the end of the course you should be able to do the following: Combinational Logic. Analyze and design basic combinational logic systems. Develop, simplify and implement (with various types of gates) sum of products (SOP) and product of sums (POS) expressions. Analyze and design decoder logic including memory systems for microcomputers. Analyze and design logic using multiplexers including their use in time division multiplexing systems. Distinguish between the various programmable logic devices and draw logic using the short hand logic commonly used in PLDs. Sequential Logic. Analyze and design basic sequential logic systems. Analyze various circuits, including determination of waveforms and state diagrams, with SR, D, JK and T flipflops. Design and analyze various counters made up of the four types or flip-flops or using universal counters. Design state machines in an efficient manner. Software. Simulate and trouble shoot simulations of the types of logic studied in the course. Use the VHDL language to design, simulate and troubleshoot both combinational and sequential logic using the CAD software. Present the results in a well-documented report with all logic and timing diagrams computer generated. Professionalism, Professional Societies and Lifelong Learning. Appreciate the value of professionalism in your class work, projects and career as well as the usefulness of, and role of professional societies in, lifelong learning. Grading (Note: You can’t pass the course with a failing average in your tests and final exam): Homework 10 % Projects 30 % Professional Society Meeting 5 % attendance Tests Final Exam Technical Journal Report 25 % 25 % 5% Notes: (1) NJIT Honor Code will be strictly followed in all courses. (2) Any revisions to syllabi during the semester will be made in consultation with students. Page 1 of 2 ECET 365: Digital Logic and Circuit Design Text: Brown and Vranesic, Fundamentals of Digital Logic with VHDL Design, 3rd Ed., McGraw-Hill. Software: Quartus II (included with text) Week Date Reading Topics & Activities 1 1/19 1.1 – 1.6 2.1 - 2.6 2 1/26 2.7 , 4.1 - 4.5 3 2/2 2.8 -2.12 3.1 - 3.3 4, 5 2/9, 2/16 3.9 6.1 - 6.4 6.6 - 6.8 Introduction to Combinational Logic, Boolean Algebra, Gates, Logic Diagrams NAND & NOR implementations, Simplification of Expressions, Truth Tables, K-maps, Don’t cares, Multi-output synthesis and analysis Introduction to multiplexers, Introduction to CAD tools and VHDL, NMOS and CMOS gates **Test 1** Transmission Gates, Decoders, Encoders, Multiplexers, Shannon's Expansion VHDL for Combinational Circuits Electrical Considerations Multi-level logic 6 2/23 3.8 4.6 7 3/2 5.1 - 5.3, 5.5 6.5, 9.6 Arithmetic Logic, Comparators Hazards and Glitches 3.6, 3.10 Notes ROMs & PROMs Programmable Logic Devices **Test 2** 7.1 - 7.7 Introduction to Sequential Logic Latches and Flip Flops 8 3/9 Homework & Project due dates #1 Ch. 2: 1, 2, 7, 8, 20, 31, 32 #2 Ch. 4: 1 - 5, 10, 12 First Software Assignment Due #3 Ch. 2: 44, 45, 47 (Use K-maps); Ch. 3: 1, 2, 3 (functional equivalence) #4 Ch. 6: 1 – 6 (Do not need to use only 2:1 MUXs) Project 1 due Instructor Assigned Problems #5 Ch. 5: 1, 3, 4, 5, 17 (see examples in class notes) ; Ch. 6: 19, 20, 24 [selected & conditional (if…else) signal assign.]; Ch. 9: 10 - 12 Project 2 due #6 Ch. 3: 36 – 38 3/16, SPRING BREAK 9 3/23 10 3/30 11 4/6 12 4/13 13,14 4.20, 4/27 #7 Ch. 7: 1, 4, 5, 6, 8 Last day to submit Journal report. Latches and Flip Flops Continued #8 Ch. 7: 10, 11 Project 3 due. 7.8 - 7.12 Registers & Counters, VHDL & CAD tools **Test 3** #9 Ch. 7: 15, 16, 18, 24 8.9 Analysis of Sequential Logic State, Transition, and Excitation Tables State Diagrams 8.1 - 8.7 Design of Sequential Logic: Counters, Universal Counters, Sequence Detectors, State Reduction, Binary Assignment, Excitation Equations Page 2 of 2 #10 Ch. 8: 29 (Develop state equations) Last day to submit Meeting report. #11 Ch. 8: 1, 2, 5, 30 Project 4 due.