ECEN 5014, Spring 2013 – Special Topics: Active Microwave

advertisement

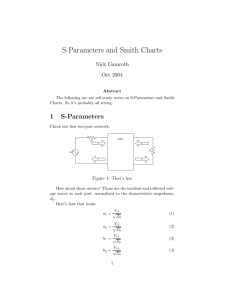

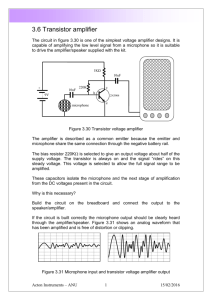

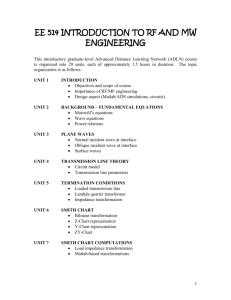

ECEN 5014, Spring 2013 – Special Topics: Active Microwave Circuits and MMICs Zoya Popovic, University of Colorado, Boulder LECTURE 3: SMALL-SIGNAL LINEAR AMPLIFIER DESIGN L3.1.A BILATERAL TWO-PORT NETWORK Transistor S-parameters are usually given as common-source two-port parameters. Since there is feedback between the output and input port of a realistic transistor, the two-port is considered to be bilateral. In that case, the input scattering parameter is affected by the load impedance through this feedback (i.e. it is different from s11 of the device), and the output scattering parameter is affected by the generator impedance (i.e. it is different from s22 of the device). From Fig.L3.1, the input coefficient of the two port, with given s-parameters, terminated in an arbitrary load is found from the reflection coefficient definition: sin b1 s11a1 s12 sLb2 s s s s11 12 21 L , 1 s22 sL a1 a1 where b2 is eliminated from the above expression using the relation b2 s21a1 s22a2 s21a1 s22 sLb2 . Similarly, the output reflection coefficient looking into port 2 is found to be: s12 s21sg , sout s22 1 s11sg where sg is the generator reflection coefficient. These expressions are used to define various transistor and amplifier gain values, as well as for stability analysis, which is discussed below. Fig.L3.1. Input and output scattering parameters of a bilateral two-port network. 1 L3.2. AMPLIFIER PARAMETERS Whether one is interested in buying or designing an amplifier, the following questions need to be answered: 1) What is the maximum and minimum required gain? 2) What is the operating frequency and bandwidth? 3) Is the amplifier matched and stable? 4) What is the required output power? 5) What sort of heat-sinking is required? To answer these questions we need to define a set of parameters that describes the amplifier. These parameters are defined for linear amplifiers with time-harmonic input signals. ag ZS VS a1 S a2 D b1 bg G in L b2 ZL S C om m on -source S-param eters out ( ) in common-source configuration. Fig.L3.2. Transistor as a bilateral two-port network GAIN For gain definitions, people often use the notation shown in Fig.L3.1. There are several definitions of the power gain in terms of the amplifier circuit. One definition useful in amplifier design is the transducer gain, GT: GT Pload Psource 1 | S |2 1 | L |2 1 | S |2 1 | L |2 PL 2 2 | s21 | | s21 | GT |1 s22 L |2 |1 s11 S |2 |1 out L |2 Pav , S |1 in S |2 This definition of gain is a ratio of the power delivered to a matched load divided by the power that the source would deliver to a matched load in the absence of the amplifier. If the amplifier is not matched to the source, then reflected power is lost and a second definition, the power gain, GP, can be defined as: GP Pload P load Psource Prefl Pin 2 1 1 | L |2 2 GP | s 21 | 1 | in |2 | 1 s 22 L |2 Finally, if an amplifier is not matched at the load, the power available from the source will not be delivered to the load, so: GA Pav 1 | S |2 1 | s21 |2 2 Pav , S |1 s11 S | 1 | out |2 Input and output Match A typical transistor with an applied DC-bias has s21 with magnitude greater than 0dB, s11 and s22 with magnitude near 0 dB (poorly matched to 50 ), and a small value of s12 . The point of doing impedance matching is to ensure the stability and robustness of the amplifier, achieve a low VSWR (to protect the rest of the circuit and conserve input power), achieve maximum power gain, and/or to design for a certain frequency response (such as flat gain or input match over a certain frequency band). A typical transistor with an applied DC-bias has with magnitude greater than 0dB, and with magnitude near 0 dB (poorly matched to 50 ), and a relatively small value of | s21 |. The point of doing impedance matching is to ensure the stability and robustness of the amplifier, achieve a low VSWR (to protect the rest of the circuit and conserve input power), achieve maximum power gain, and/or to design for a certain frequency response (such as flat gain or input match over a certain frequency band). The basic criteria in matching circuit design are: The matching network is designed with the attempt to have as low loss as possible (power is expensive and heat is not easy to get rid of). Thus, one tries to avoid using resistive components, although sometimes this is not possible. The bandwidth over which the amplifier has gain will be determined by both the input and output matching network bandwidths. A single-frequency (narrowband) match is always possible, provided that the real parts of the transistor input impedance and the load impedance are not zero (why?). A number of different techniques exist for broadband matching, and we will discuss some of them later. The technology used for the matching network will vary based on frequency range, power range and available real-estate. The matching networks should be as simple as possible and as small as possible. Sometimes, the load will vary (such as in the case of an antenna), and it is desirable to have a variable matching circuit. These circuits can range from simple diode-switched dual loads to adaptive tuning networks which include self-assessment circuits usually in the form of a detector that samples the reflected voltage of the load. Commonly used impedance matching techniques in active circuits are: 1. Lumped element matching; 2. Single stub matching; 3. Double stub matching; 4. Impedance transformers: quarter-wavelength and tapers; 3 5. Slug matching. Stability In a bilateral match, there are a few things to keep in mind: 1) Remember that a conjugate match of the amplifier means matching to the conjugate of in and out, not s11 and s22. 2) Note that in is a function of L, the output loading (and out is a function of the source loading). Therefore, we now have to perform a simultaneous match of the input and output (in other words, what we do at the input affects the output match, and vice versa). 3) Note that the denominators (1 s 22 L ) and (1 s11L ) are < 1. This indicates that for some values of the transistor S-parameters, S, and L, it may be possible for in and out to be > 1, which indicates that the transistor amplifier circuit is giving power back to the source. If a reflection coefficient becomes greater than 1, then oscillations are likely to occur, a phenomenon that we will exploit later in designing oscillators, but is an unwanted effect in amplifiers. Stability is often verified ahead of time, and there are several criteria described later. Power consumption If one is buying an amplifier, the required DC voltage and current are usually given. If one is designing and fabricating an amplifier, does one want to design for a single or dual voltage supply? There is a direct relationship between the amount of DC power consumption and RF output power. Therefore, we can decide how much DC voltage and current to use based on the amount of output power we are interested in. Heat Issues Remember that an amplifier dissipates energy as it performs amplification. Therefore, we must ask how much heat is generated and see how this compares to environmental regulations and to the maximum allowed temperature of the device itself. If necessary, we may need to use some sort of temperature regulation external to the amplifier. A heat sink is often used, but its size (determined by the amount of heat it needs to dissipate) can become quite large compared to the amplifier circuit itself. Forced cooling can be used in the form of a fan (or fans), or even liquid cooling. Amplifier Efficiency Parameters describing the amplifier efficiency quantify the power budget of the amplifier system. 1) Overall Efficiency: from a conservation of energy standpoint, the overall efficiency makes the most sense because it is the ratio of the total output power divided by the total input power ( RF and DC). It is given by 4 ALL 2) POUT PDC PIN Drain (or collector) Efficiency: If we are only interested in the amount of output RF power compared to the amount of input DC power, then we can use the drain (or collector, in the case of a BJT or HBT) efficiency given as C ,D 3) Power Added Efficiency (PAE): The power added efficiency is very useful in that it relates how well the power from the DC supply was converted to output RF power assuming that the input power is lost. Note that if the gain is very large, then the PAE converges to the value of the drain efficiency. PAE is given by PAE 4) POUT PDC POUT PIN PDC Power dissipated: Finally, the total power dissipated is the power that is not accounted for by the input RF, output RF, or input DC power, and can be found from PDISS PDC PIN POUT The dissipated power is usually mostly power lost as heat, but several other mechanisms of power loss are possible. The following are the five main types of amplifier power loss: 1) DC power converted to heat (i.e. I2R losses in the resistive elements of the transistor). 2) The input RF used to control the device. 3) Radiation from amplifier components (transmission lines or lumped elements) – especially if the amplifier is mismatched. 4) Conversion of the output power to harmonics of the fundamental frequency. 5) Loss in the DC and/or control circuitry. L3.3. UNILATERAL SMALL-SIGNAL AMPLIFIER DESIGN While concerns about output power, bandwidth, efficiency, and heat sinking were brought up in the previous section, the basic linear amplifier design discussed next is concerned only with the problem of matching the input and output of the transistor. Amplifier design (whether linear or nonlinear design) almost always begins with transistor analysis (IV curves or equivalent circuit transistor parameters), then with Smith chart analysis, ending with computer aided design. The word linear in this case means that the output power is a linear function of the input power (the gain at a given frequency is constant and does not change with output power). Linearity is a consequence of operating the device in small signal mode. The graphical meaning of small 5 signal can be seen below as related to the IV curves of the device, Fig.L3.3. The term unilateral means that the unilateral condition from the previous section is met. The design begins by taking note of some basic properties of the transistor used as the active device. The IV curves for a BJT (HBT) are shown below. IV curves for a FET are similar and the discussion here applies. (How are IV curves of a FET and bipolar device different?) The quiescent point, Q, indicates the chosen base and collector (gate and drain) DC bias points. The RF input of the common emitter (common source) design creates a current swing on the base, which is translated into a voltage swing on the drain through the amplification process. Given that the bias and input drive level have been chosen for us, our design task is to find input and output matching sections for the transistor. The assumption is that the manufacturers of the transistor were kind enough to give us the S-parameters of the device for the chosen bias point and input drive. For example let us assume that we are given the following S-parameters at 5GHz: Freq 5 GHz S11 S12 S21 S22 0.7100 0 2.560 0.7-30 Fig. L3.3. Example of transistor IV curves and small signal operation. If we now assume 50- source and load impedances, the task becomes to transform both s11 and s22 into 50-. We add reference planes to the circuit diagram so that we can properly define the 6 relevant circuit reflection coefficients. A common notation for the input and output reflection coefficients is in and out , where these represent the reflections off of the input and output of the transistor, respectively (Fig.L3.4). In this unilateral example, they are equivalent to s11 and s22 . S is the reflection coefficient looking into the input matching section toward the source. Similarly, L is defined looking into the output match towards the load. L Load matching Source Load Source matching out in S Fig. L3.4. Reflection coefficients related to the device and matching sections. To perform a conjugate match, we simply want design matching sections such that * S in* and L out This means that for the source we must see, instead of 50 or S=0, the complex conjugate of s11, so S = 0.7100. Similarly, L = 0.7100. By conjugate matching the input and output of the device to the source and load, we have guaranteed the maximum transducer gain possible for this amplifier. This matched transducer gain is a function of s21 and the matching sections and is given by GT in 1 1 S 2 s21 2 1 L 2 1 s22 L 2 L out S S - plane L - plane Figure L3.5. Smith chart illustration of the input and output matching. 7 In Fig.L3.5, in and out can first be plotted on separate Smith charts. Next S and L are plotted before matching is introduced (at 50 Ohms). Finally, a marker is placed 180 from in and out representing the complex conjugate of the input and output impedances of the transistor. An arrow then indicates the transformation that must be made for the source and the load. We may stop here with the design of the unilateral case. We have achieved the best possible match and gain of the device at 5GHz. But we have neglected many things in this simple example: - Usually s12 is not zero or negligibly small; - The transistor in this circuit has behavior at other frequencies which needs to be analyzed; - The small signal approximation might not be quite valid; - Maybe we are concerned with noise, power or efficiency in addition to gain. 3.4. UNILATERAL FIGURE OF MERIT In the above design, it was assumed that | s12 | was zero, or small enough that it can be neglected. Consider the transducer gain formula for the case when |s12| is small. For this case, the formula reduces to the unilateral transducer gain, GTU. What is “small enough” in reality? Observing the expression for transducer gain for the bilateral and unilateral cases, respectively, one can define the following ratio that can be used to define a figure of merit for whether a transistor is unilateral or not, in small signal operation. In the case of maximal unilateral transducer gain when the source and load are matched, the ratio GT/GTU is bounded by Here U is referred to as the unilateral figure of merit. The value of U varies with frequency, since the s-parameters vary with frequency. In order to check if one can use the unilateral approximation at a given frequency, it is advisable to plot U as a function of frequency and determine a range where its absolute value is smaller than approximately -15dB (which corresponds to the ratio GT/GTU being smaller than about 0.25dB). 8 3.5. BILATERAL DESIGN If the s12 parameter is not negligible, the analysis becomes more complex, but we can still follow the strategy in the previous example. If | s12 | 0 , it is mostly due to the capacitance between the gate and drain discussed earlier in the equivalent circuit model of the device. The important result of this input-to-output coupling is that we can no longer say that in s11 as in the unilateral case. Instead, the input and output matching network need to perform conjugate matches as follows: *S in s11 s12 s21 L s s and *L out s22 12 21 S . 1 s22 L 1 s11 S This result has several important implications: 4) A conjugate match of the amplifier means matching to the conjugate of in and out , not s11 and s22 . 5) in is a function of L , the output loading (and out is a function of the source loading). Therefore, we now have to perform a simultaneous match of the input and output (in other words, what we do at the input affects the output match, and vice versa). 6) The denominators (1 s22 L ) and (1 s11 L ) are less than unity. This should make you especially suspicious that for some values of the transistor s-parameters, S, and L, it may be possible for in and out to be greater than unity, which would indicate an instability. Regarding 1) and 2), a simultaneous match can be found analytically by solving simultaneously the equations for the source and load reflection coefficients. The result is: B12 4 C1 S ,M B1 B22 4 C2 2 L ,M B2 2C1 2 2C2 where B1 1 s11 s22 2 2 * C1 s11 s22 2 2 B2 1 s22 s11 2 2 2 C2 s22 s11* where s11s22 s12 s21 is the determinate of the S-matrix. NOTE: you can only use these formulas if the device is unconditionally stable! If it is not (in most cases), you can do few things: 9 - Make it unconditionally stable by adding, e.g. a resistor in the gate, and recalculating the S-parameters of this “new” device; Using a simulator to slowly tune the input and output matches from the unilateral case and watching the trends in gain, stability, match, etc. So, the third implication of non-zero s12 mentioned earlier is potential instability, i.e. whether in and out become greater than 1. If a reflection coefficient becomes greater than 1, then oscillations are likely to occur, a phenomenon that we will exploit later in designing oscillators, but is an unwanted effect in amplifiers. Stability is often verified ahead of time using stability circles of allowed and non-allowed impedances. The derivation of the stability circles is messy but straightforward, to see how it is done, look up, e.g. Gonzales’ book. Alternatively, one can calculate two numbers at a given frequency point to determine if the transistor will be unconditionally stable, i.e. stable for all loads. 1 s11 s22 The stability factor K, given by K , along with the scattering matrix 2 s12 s21 2 2 2 determinant are calculated and compared to unity: - If K 1 and | | 1 , then the transistor is unconditionally stable at that frequency. This means that no matter what the load and source impedances are, in and out will always be less than unity. - If K 1 and | | 1 , the transistor is conditionally stable at that frequency. This means that for some values of the load and source impedances, in and out may exceed unity, in which case we need to do additional work when designing the matching sections, as will be discussed next week in class. When designing an amplifier, it is also necessary to check the stability at other frequencies. If there are instabilities, then it may be necessary to add resistors in the design. In this way, we may trade stability for some gain. Which of the possible combinations of the solutions for S ,M and L ,M in the solutions to the simultaneous matched condition do we choose? It turns out that the two solutions with the negative sign are the ones that are useful for an unconditionally stable network. If | B1 / 2C1 | 1 and B1 0 in the equation for S ,M then the solution with the negative sign produces | S ,M | 1 and the solution with the plus sign results in | S ,M | 1 , and similar statements are true for L ,M , which we will prove next week in class. The maximal transducer power gain under simultaneously matched conditions is GT ,max 1 | L,M |2 1 2 | s21 | , which can be written in the following format: 1 | S ,M |2 |1 s22L,M |2 10 GT ,max | s21 | K K 2 1 . | s12 | Under simultaneous matched condition, GT ,max GP ,max G Av ,max . The maximal stable gain will be the value when K 1 , i.e. Gmax, stable | s21 | / | s12 | . This is a figure of merit for potentially unstable transistors and is often given in manufacturer’s specification sheets. Note that the S-parameters that all of this discussion is based on assume a perfectly grounded source, which is rarely the case. In a hybrid circuit, the source lead inductance can be significant. To ensure stability in this case, you need to re-calculate the S-parameters with an inductor between source and ground and design the matching for this case in any of the ways mentioned above. Typically, K and will have dramatically different values with and without the source inductance, which provides additional positive feedback. Recommended reading related to this lecture: Microwave Transistor Amplifiers, Gonzales, 1984 edition, pages 92-132 Fundamentals of RF and Microwave Transistor Amplifiers, Bahl, parts of Chapter 3 11