Ch5. Synchronous Sequential Logic

advertisement

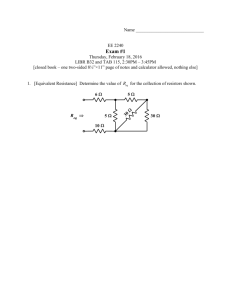

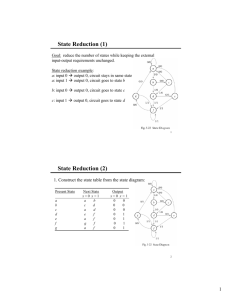

EEA051 - Digital Logic 數位邏輯 Chapter 5 Synchronous Sequential Logic 吳俊興 國立高雄大學 資訊工程學系 December 2005 Chapter 5 Synchronous Sequential Logic 5-1 Sequential Circuits 5-2 Latches 5-3 Flip-Flops 5-4 Analysis of Clocked Sequential Circuits 5-5 HDL for Sequential Circuits 5-6 State Reduction and Assignment 5-7 Design Procedure 2 5-1 Sequential Circuits Combinational circuits The outputs are entirely dependent on the current inputs z Contains no storage elements, no feedback z Sequential circuits Consists of a combinational circuit to which storage elements are connected to form a feedback path z Outputs are a function of both the current inputs and the present state of the storage elements z Storage/memory elements capable of storing binary information z defining the state of the sequential circuit z Next state is a function of external inputs and current state z (inputs, current state) ⇒ (outputs, next state) 3 Types of Sequential Circuits Two major types: depending on timing of their signals Asynchronous sequential circuits (see Chapter 9) The transition happens at any instant of time z Do not use clock pulses. Change of internal state occurs when there is a change in input variables z z Storage elements work as time-delay device Instability problem: may become unstable at times May be regarded as a combinational circuit with feedback Synchronous sequential circuits The transition happens at discrete instants of time z The circuit responds only to pulses on particular inputs z Storage elements are affected only with the arrival of each pulse z 4 Synchronous Clocked Sequential Circuits Clocked sequential circuits (CSC) Synchronous sequential circuits that use clock pulses in the inputs of storage elements z Synchronization is achieved by a master-clock generator to generate a periodic train of clock pulses z most commonly used, no instability problems z Flip-flops: the storage elements used in CSC binary cells capable of storing one bit of information z Maintains a binary state indefinitely until directed by an input signal to switch states z z The states change only during a clock pulse transition major differences in the number of inputs they possess and in the manner in which the inputs affect the binary state 5 The outputs can come either from the combinational circuit or from the flip-flops or both The flip-flops receive their inputs from the combinational circuit and also from a clock signal with pulse that occurs at fixed intervals of time z The flip-flop outputs cannot change and the feedback loop is broken when a clock pulse is not active 6 5-2 Latches Latches: basic circuits to construct flip-flops z capable of storing binary information, impractical for use in synchronous sequential circuits more complicated types can be built upon it SR Latch Two states: Set and Reset states z an asynchronous sequential circuit with two cross-coupled NOR gates z S’-R’ Latch z SR latch with two cross-coupled NAND gates SR latch with control input z 0 signal to change its state Determines when the state of the latch can be changed D Latch z eliminate undesirable condition of indeterminate state in SR latch 7 SR Latch Two inputs labeled S for set and R for reset (S,R)=(1,0): set (Q=1, the set state) (S,R)=(0,1): reset (Q=0, the reset/clear state) (S,R)=(0,0): normal condition z z no operation, in either the set or the reset state depending on which input was most recently at 1 (S,R)=(1,1): indeterminate state (Q=Q'=0) z consider (S,R) = (1,1) ⇒ (0,0) unpredictable next state when both inputs return to 0 (depend on which input returns to 0 first) Q = [R+(S+Q)’]’ = R’(S+Q) Q’ = [S+(R+Q’)’]’ = S’(R+Q’) (S+Q)’ (R+Q’)’ 8 S’-R’ Latch – SR Latch with NAND Gates 0 signal to change its state (S,R)=(0,1): set (Q=1, the set state) (S,R)=(1,0): reset (Q=0, the reset/clear state) (S,R)=(1,1): normal condition (S,R)=(0,0): indeterminate state (Q=Q’=1) unpredictable next state 9 SR Latch with Control Input An additional input as an enable signal C=0 ⇒ quiescent condition, no change C=1 ⇒ S or R is allowed to affect the SR latch (1 signal to change its state) S_ 1/S' 0/1 R_ 1/R' 10 D Latch S=D and R=D’ Ensure S and R are never equal to 1 at the same time z Eliminate the undesirable conditions of the indeterminate state in the RS latch z One output Q and two inputs: D (data) and C (control) Q=D Q = no change when C=1 when C=0 S_ 1/D' 0/1 R_ 1/D 11 Graphic Symbols for Latches 12 5-3 Flip-Flops A trigger: the momentary change to switch the state of a latch or flip-flop z The transition it causes is said to trigger the flip-flop Types of triggers z Level triggered – latches z D latch is triggered every time the pulse stays at logic 1 level. Be used as a temporary storage between a unit and its environment Edge triggered – flip-flops If level-triggered flip-flops are used, the feedback path may cause instability problem as long as the clock pulse stays in the active level triggered only during a signal transition (0⇒1 or 1⇒0) 13 Edge-triggered D flip-flop Store binary info during transition Method 1: Master-slave D flip-flop two separate flip-flops a master flip-flop (positive-level triggered) a slave flip-flop (negative-level triggered) z change only during negative edge of clock z longer propagation delay 14 Edge-triggered D flip-flop (cont.) Method 2: D-type positive-edge-triggered flip-flop z The most efficient flip-flop constructed with 3 SR latches CLK=0 ⇒ S=R=1, no change CLK=positive transition ↑⇒ Q=D (state changes once) D=0 when CLK becomes 1 ⇒ R=1 to 0 ⇒ D changes further, no effect D=1 when CLK becomes 1 ⇒ R=stay 1 ⇒ D changes further, no effect CLK=negative transition or 1 ⇒ quiescent condition (state holds) (RD)’ S [S(RD)’]’=S’+RD S=CLK’+S(RD)’ Q=R ⇒ Q=D [S(RD)’]’ S (RD)’ R R=CLK’+S’+RD (RD)’ 15 (RD)’ S [S(RD)’]’=S’+RD S=CLK’+S(RD)’ [S(RD)’]’ S (RD)’ R R=CLK’+S’+RD =CLK’+[S(RD)’]’ (RD)’ D=0 D=1 S=CLK’+S R=CLK’+S’ S=CLK’+SR’ R=CLK’+(SR’)’ CLK=0 S=R=1 D=0 Q=Q S=R=1 D=1 Q=Q CLK=1 S=S R=S’ S=SR’ R=(SR’)’=S’ S=0, R=1, Q=1 t 0 1 2 3 4 5 6 7 8 9 10 12 14 16 18 20 22 24 26 28 30 CLK __--__--__--__--__--__--__--__-D _______--------________--------_ Q --________--------________----- 16 Setup Time and Hold Time Setup time a minimum time for which the D input must be maintained at a constant value (or be ready) prior to the occurrence of the clock transition data to the internal latch Hold time a minimum time for which the D input must not changes after the application of the positive transition of the clock clock to the internal latch These parameters are usually specified in manufacturer’s data books. 17 Graphic Symbols > dynamic indicator 18 JK Flip-Flop Edge-triggered D flip-flop z z z Store binary information during edge trigger Require the smallest number of gates Other types of flip-flops can be constructed using it JK Flip-Flop: D=JQ'+K'Q J=0, K=0: D=Q J=0, K=1: D=0 J=1, K=0: D=1 J=1, K=1: D=Q’ ⇒ Q no change ⇒ Q =0 reset to 0 ⇒ Q =1 set to 1 ⇒ Q =Q’ complement output 19 T Flip-Flop T (toggle) flip-flop: D = T⊕Q = TQ'+T'Q T=0: D=Q, no change T=1: D=Q' ⇒ Q=Q' 20 Characteristic Tables and Equations Characteristic Tables Characteristic equations D flip-flop JK flip-flop T flop-flop Q(t+1) = D Q(t+1) = JQ’+K’Q Q(t+1) = T⊕Q = TQ’ + T’Q 21 Direct Inputs preset/direct set: the inputs that sets the flip-flop to 1 clear/direct reset: the inputs that clears the flip-flop to 0 z to a known starting state asynchronous reset reset=0 ⇒ force Q=0, resetting 22 5-4 Analysis of Clocked Sequential Circuits State equation (transition equation) A(t+1) = A(t)x(t) + B(t)x(t) B(t+1) = A’(t)x(t) y(t)=[A(t)+B(t)]x’(t) or A(t+1)=Ax+Bx B(t+1)=A’x y=(A+B)x’ CSC diagram ⇒ state equation 23 State Table or Transition Table state table ⇐ state equation ⇐ CSC diagram Four sections: present state, input, next state and output List all possible binary combinations of present state and inputs Determine next states and outputs from the logic diagram or from the state equations A(t+1)=Ax+Bx B(t+1)=A’x y=(A+B)x’ m flip-flops and n inputs • 2m+n rows • m column of next-state 24 Second Form of State Table Only 3 sections: present state, next state, and output z Given one input, there are two possible next states and outputs for each present state What form to be used depends on applications 25 State Diagram - pictorial view of state transitions input/output x/y A(t+1)=Ax+Bx B(t+1)=A’x y=(A+B)x’ state diagram ⇔ state table ⇔ state equation ⇔ logic diagram 26 Input/Output Equations logic diagram of a sequential circuit consists of flip-flops + gates z z output equations: the circuit that generates external outputs input equations: the circuit that generates inputs to flip-flops output equations input equations state characteristic (or excitation equations) equations equations Symbol convention: DQ = x + y an OR gate with inputs x and y connected to the D input of a flip-flop whose output is labeled with the symbol Q x y 27 Flip-Flop Input Equations FF Input Equations State Equations DA=Ax+Bx A(t+1)=Ax+Bx B(t+1)=A’x ⇒ DB=A’x Output Equation y=(A+B)x’ y=(A+B)x’ D/JK/T FF input equation ⇔ state equation ⇔ CSC logic diagram ⇔ state diagram ⇔ state table 28 Analysis with D Flip-Flops Given: input function: DA=A⊕x⊕y state equation: A(t+1)=A⊕x⊕y one flip-flop and 2 inputs Find: ⇔ logic diagram ⇔ state table ⇔ state diagram 29 Analysis with JK Flip-Flops Given logic circuit, find the others (1) Flip-flop input equations (2) State equations (3) (4) 30 Analysis with T Flip-Flops Characteristic equation: Q(t+1)=T⊕Q=T’Q+TQ’ Input equations and output equation: TA=Bx; TB=x; y=AB State equations A(t+1)=(Bx)’A+(Bx)A’=AB’+Ax’+A’Bx B(t+1)=x⊕B Given logic circuit, find the others 31 Mealy and Moore Models Mealy model The output is a function of both the present state and input — — — The outputs may change if the inputs change during the clock cycle The outputs may have momentary false values due to delay To synchronize, the outputs must be sampled only during the clock edge Mealy finite state machine (FSM, machine): the Mealy model of a sequential circuit example: Fig. 5-15 (D) Moore model The output is a function of the present state only — The outputs are synchronized with the clock Moore finite state machine (FSM, machine): the Moore model of a sequential circuit example: Figure 5-19 (JK), 5-20 (T) 32 5-6 State Reduction and Assignment Sequential circuit analysis: starts from a circuit diagram and z culminates in a state table or state diagram z Sequential circuit design: starts from a set of specifications and z culminates in a logic diagram z State reduction problem: reduction of the number of flip-flops in a sequential circuit, while keeping the external input-output requirements unchanged m flip-flops produce 2m states z State reduction ⇒ fewer flip-flops z but may require more combinational gates 33 State Reduction Example: Figure 5-22 (7 states) Given a state table or state diagram z Find ways of reducing the number of states without altering the input-output relationships z Test sequence •Initial state: a •Input sequence: 01010110100 34 State Equivalence State equivalence: Two states are equivalent if, for each member of the set of inputs, they give exactly the same output and send the circuit either to the same state or to an equivalent state Algorithm: 1.Look for two present states that go to the same next state and have the same output for both input combinations 2.Remove one of the equivalent state and replace by the other state each time it occurs in the table Another approach: systematic reduction with an implication table (see Section 9-5) 35 State Reduction Example 36 State Assignment State assignment: assign coded binary values to the state z z In order to design a sequential circuit with physical components A circuit with m states need n bits where 2n >= m Transition table: a state table with a binary assignment z To distinguish it from a stable table with symbolic names for states 37 5-7 Design Procedure Design of a clocked sequential circuit starts from a set of specifications z obtains a state table/diagram (or equivalences) first z culminates in a logic diagram (or a list of Boolean functions) z Tasks z Choosing the flip-flops z Finding a combinational gate structure Determined from the number of states needed Derived from the state table by evaluating the flip-flop input equations and output equations Summarized procedure most challenging Synthesis 38 Example: Sequence Detector Specification: Design a circuit that detects three or more consecutive 1’s in a string of bits combining through an input line 1st Step – deriving state diagram or state table Moore model circuit –output is 1 when circuit is in state S3 and 0 otherwise 39 Synthesis Using D Flip-Flops Step 2-4: Assign binary codes and list state table (Table 5-11) Step 5:Choose type of flip-flops Step 6:Derive simplified input and output equations 0 1 2 3 4 5 6 7 40 Synthesis Using D Flip-Flops (cont.) Step 7 – Draw the logic diagram (using simplified functions) Excitation table: a table that lists required inputs 41 Analysis and Design present states input equations output equations ? state equations ? characteristic equations (1) Input/output equations (2) state equations (3) State table (4) State diagram ? present states output equations input equations next states Excitation Table (1) State diagram/table (2) Input/output equations (3) Circuit diagram 42 Excitation Tables The input equations for the circuit using flip-flops other than the D type, i.e. JK and T types, must be derived indirectly from the state table Excitation table: list the required inputs for a given change of state 43 Synthesis Using JK Flip-Flops The input equations must be evaluated from the present-state to next-state transition derived from the excitation table (1) (2) 44 Logic Diagram for Sequential Circuit with JK Flip-Flops (3) JA=Bx’ KA=Bx JB=x KB=(A⊕ x)’ 45 Synthesis Using T Flip-Flops Example: 3-bit counter (0) (1) 0 (2) 46 Logic Diagram of 3-Bit Binary Counter (3) TA2=A1A0 TA1=A0 TA0=1 47 Summary Chapter 5 Synchronous Sequential Logic 5-1 Sequential Circuits 5-2 Latches — SR latch, S’R’ latch, D latch 5-3 Flip-Flops — edge-triggered D, JK, T flip-flops 5-4 Analysis of Clocked Sequential Circuits 5-5 HDL for Sequential Circuits 5-6 State Reduction and Assignment 5-7 Design Procedure circuit diagram⇔input equation⇔state equation⇔state table⇔state diagram 48