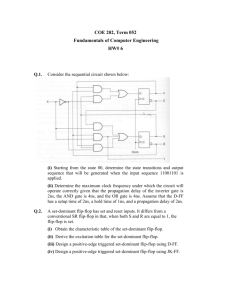

Lecture 5 Synchronous Sequential Logic

advertisement

Digital Circuit Design Synchronous Sequential Logic Lan-Da Van (范倫達), Ph. D. Department of Computer Science National Chiao Tung University Taiwan, R.O.C. Fall, 2012 ldvan@cs.nctu.edu.tw http://www.cs.nctu.edu.tw/~ldvan/ Digital Circuit Design Outlines Lecture 5 Sequential Circuits Storage Elements: Latches Storage Elements: Flip-Flops Analysis of Clocked Sequential Circuits State Reduction and Assignment Design Procedure Lan-Da Van DCD-05-2 Digital Circuit Design Sequential Circuits Lecture 5 Sequential Circuits a feedback path the state of the sequential circuit (inputs, current state) (outputs, next state) synchronous: the transition happens at discrete instants of time asynchronous: at any instant of time Lan-Da Van DCD-05-3 Digital Circuit Design Sequential Circuits Lecture 5 Synchronous sequential circuits a master-clock generator to generate a periodic train of clock pulses the clock pulses are distributed throughout the system clocked sequential circuits most commonly used no instability problems the memory elements: flip-flops binary cells capable of storing one bit of information two outputs: one for the normal value and one for the complement value maintain a binary state indefinitely until directed by an input signal to switch states Lan-Da Van DCD-05-4 Synchronous Clocked Sequential Circuit Lan-Da Van Digital Circuit Design Lecture 5 DCD-05-5 Digital Circuit Design S-R Latch Lecture 5 SR Latch with two NOR gates 1->0 0->1->0->1… 1->0 0->1->0->1… Lan-Da Van DCD-05-6 Digital Circuit Design S-R Latch Lecture 5 SR latch with two NAND gates an asynchronous sequential circuit (S,R)= (1,1): no operation (S,R)=(1,0): reset (Q=0, the clear state) (S,R)=(0,1): set (Q=1, the set state) (S,R)=(0,0): indeterminate state (Q=Q'=0) consider (S,R) = (0,0) (1,1) Lan-Da Van DCD-05-7 Digital Circuit Design S-R Latch Lecture 5 SR latch with control input En=0, no change En=1, see the function table Lan-Da Van DCD-05-8 Digital Circuit Design D Latch Lecture 5 D Latch eliminate the undesirable conditions of the indeterminate state in the RS flip-flop D: data gated D-latch D Q when C=1; no change when C=0 Lan-Da Van DCD-05-9 Digital Circuit Design Graphic Symbols Lan-Da Van Lecture 5 DCD-05-10 Digital Circuit Design Flip-Flops Lecture 5 A trigger: The state of a latch or flip-flop is switched by a change of the control input. Level sensitive – latches Edge triggered – flip-flops Clock response in latch and flip-flop Lan-Da Van DCD-05-11 Digital Circuit Design Flip-Flops Lecture 5 If level-triggered latches are used the feedback path may cause instability problem Edge-triggered flip-flops the state transition happens only at the edge eliminate the multiple-transition problem Lan-Da Van DCD-05-12 Negative Edge-Triggered D Flip-Flop Digital Circuit Design Lecture 5 Master-Slave D flip-flop Two separate flip-flops A master flip-flop (positive-level triggered) A slave flip-flop (negative-level triggered) The most economical and efficient Lan-Da Van DCD-05-13 Positive Edge-Triggered D Flip-Flop Digital Circuit Design Lecture 5 A D-type positive-edge-triggered flip-flop Three basic flip-flops (S,R) = (0,1): Q = 1 (S,R) = (1,0): Q = 0 (S,R) = (1,1): no operation (S,R) = (0,0): should be avoided D-type positive-edge-triggered flip-flop Lan-Da Van DCD-05-14 Positive Edge-Triggered D Flip-Flop Digital Circuit Design Lecture 5 Operations of D-type positive-edge-triggered flip-flop The S and R inputs of the output latch are maintained at the logic-1 level when Clk=0. If D=0 When Clk becomes 1, R changes to 0. This causes the flip-flop to go to reset state making Q=0. If there is a change in the D input while Clk=1, terminal R remains at 0, terminal S remains at 1, and Q=0. Thus, the filp-flop is locked out and is unresponsive to futher changes in the input. When the Clk returns to 0, R goes to 1, placing the output latch in quiescent condition without changing the output. Lan-Da Van DCD-05-15 Positive Edge-Triggered D Flip-Flop Digital Circuit Design Lecture 5 Clk D S R Q Lan-Da Van DCD-05-16 Digital Circuit Design J-K Flip-Flop Lecture 5 JK flip-flop D=JQ'+K'Q J=0, K=0: D=Q(t) Q(t+1) =Q(t): No change J=0, K=1: D=0 Q(t+1) =0: Reset J=1, K=0: D=1 Q(t+1) =1: Set J=1, K=1: D=Q‘(t) Q(t+1) =Q‘(t): Complement Lan-Da Van DCD-05-17 Digital Circuit Design T Flip-Flop Lecture 5 D = T⊕Q = TQ'+T'Q T=0: D=Q Q(t+1) =Q(t): No change T=1: D=Q' Q(t+1) =Q‘(t): Complement Lan-Da Van DCD-05-18 Digital Circuit Design Characteristic Table Lecture 5 Characteristic equations D flip-flop Q(t+1) = D JK flip-flop Q(t+1) = JQ'+K'Q T flip-flop Q(t+1) = T⊕Q Lan-Da Van DCD-05-19 Digital Circuit Design Direct Inputs Lecture 5 Asynchronous set and/or asynchronous reset 1 1 D flip-flop with asynchronous reset Lan-Da Van DCD-05-20 Digital Circuit Design Analysis of Clocked Sequential Ckts Lecture 5 State equation A(t+1) = A(t)x(t) + B(t)x(t) B(t+1) = A'(t)x(t) Output equation Lan-Da Van y(t) = (A(t)+B(t))x'(t) DCD-05-21 Digital Circuit Design State Table – First Form Lan-Da Van Lecture 5 DCD-05-22 Digital Circuit Design State Table – Second Form Lecture 5 A(t + 1) =Ax + Bx B(t + 1) = Ax y = Ax + Bx Lan-Da Van DCD-05-23 Digital Circuit Design State Diagram Lecture 5 State transition diagram a circle: a state a directed lines connecting the circles: the transition between the states Each directed line is labeled 'inputs/outputs‘ a logic diagram a state table a state diagram Lan-Da Van DCD-05-24 Digital Circuit Design Flip-Flop Input Equations Lecture 5 The part of circuit that generates the inputs to flipflops Also called excitation functions DA = Ax + Bx DB = A'x The output equations y = (A+B)x' Lan-Da Van DCD-05-25 Digital Circuit Design Analysis with D flip-flops Lecture 5 The input equation DA=A⊕x⊕y The state equation A(t+1)=A⊕x⊕y Lan-Da Van DCD-05-26 Digital Circuit Design Analysis with JK flip-flops Lecture 5 Determine the flip-flop input function in terms of the present state and input variables Use the corresponding flip-flop characteristic table to determine the next state Lan-Da Van DCD-05-27 Digital Circuit Design Analysis with JK flip-flops Lecture 5 JA = B, KA= Bx' JB = x', KB = A'x + Ax‘ derive the state table Lan-Da Van DCD-05-28 Digital Circuit Design Analysis with JK flip-flops Lecture 5 State transition diagram A(t 1) J A A' K A' A A(t 1) BA'(Bx' )' A A' B AB' Ax B(t 1) J B B' K B' B B(t 1) x' B'( A x)' B B' x' ABx A' Bx' State diagram Lan-Da Van DCD-05-29 Digital Circuit Design Analysis with T flip-flops Lecture 5 The characteristic equation Q(t+1)= T⊕Q = TQ'+T'Q Lan-Da Van DCD-05-30 Digital Circuit Design Analysis with T flip-flops Lecture 5 The input and output functions TA=Bx TB= x y = AB The state equations A(t+1) = (Bx)'A+(Bx)A' =AB'+Ax'+A'Bx B(t+1) = x⊕B Lan-Da Van DCD-05-31 Digital Circuit Design Analysis with T flip-flops Lecture 5 State table TA TB 0 0 0 1 0 0 0 1 0 1 0 1 0 1 0 1 Lan-Da Van DCD-05-32 Digital Circuit Design Mealy and Moore Models Lecture 5 Mealy model: the output is the function of both the present state and inputs. the outputs may change if the inputs change during the clock pulse period Moore model: the output is the function of the present state only. The outputs are synchronous with the clocks. Lan-Da Van DCD-05-33 Digital Circuit Design Mealy and Moore Models Lan-Da Van Lecture 5 DCD-05-34 State Reduction and Assignment Digital Circuit Design Lecture 5 State Reduction reductions on the number of flip-flops and the number of gates a reduction in the number of states may result in a reduction in the number of flipflops An example state diagram state input a a b c d e f f g f g abdf 0 1 0 1 0 110 10 0 111 output 0 0 0 0 0 110 10 0 001 Lan-Da Van DCD-05-35 Digital Circuit Design State Reduction Lecture 5 Algorithm: equivalent states Two states are said to be equivalent. For each member of the set of inputs, they give exactly the same output and send the circuit to the same state or to an equivalent state One of them can be removed g=e Lan-Da Van DCD-05-36 Digital Circuit Design State Reduction Lecture 5 Reducing the state table based on g=e f=d Lan-Da Van DCD-05-37 Digital Circuit Design State Reduction Lecture 5 The final sequence list: state input output aabcdeddedea 01010110100 00000110100 Lan-Da Van DCD-05-38 Digital Circuit Design Reduced State Diagram Lecture 5 Checking of each pair of states for possible equivalence can be done systematically The unused states are treated as don't-care condition fewer combinational gates Lan-Da Van DCD-05-39 Digital Circuit Design State Assignment Lecture 5 Minimize the cost of the combinational circuits Three possible binary state assignments Lan-Da Van DCD-05-40 Digital Circuit Design State Assignment Lecture 5 Any binary number assignment is satisfactory as long as each state is assigned a unique number use binary assignment 1 Lan-Da Van DCD-05-41 Digital Circuit Design Design Procedure Lecture 5 From the word description and specification of the desired operation, derive a state diagram for the circuit. Reduce the number of states if necessary. Assign binary values to the states. Obtain the binary-coded state table. Choose the type of flip-flops to be used. Derive the simplified flip-flop input equations and output equations. Draw the logic diagram. Lan-Da Van DCD-05-42 Digital Circuit Design Sequence Detector Using D Flip-Flops Lecture 5 Specification: Design a circuit that detects a sequence of three or more consecutive 1’s in a string of bits coming through an input line (i.e., the input is a serial bit stream). State Diagram: Starting with state S0, the reset state If the input is 0, the circuit stays in S0, but if the input is 1, it goes to state S1 to indicate that a 1 was detected. If the next input is 1 (i.e., two consecutive 1s), the change is to state S2 to indicate the arrival of two consecutive 1’s, but if the input is 0, the state goes back to S0. If the next input is 1, (i.e., three consecutive 1s), the change is to state S3 to indicate the arrival of three consecutive 1’s, but if the input is 0, the state goes back to S0. If more 1s are detected, the circuits stays in S3. Any 0 input sends the circuit back to S0. Moore machine!! Lan-Da Van DCD-05-43 Digital Circuit Design Sequence Detector Using D Flip-Flops Lecture 5 Sequence detector state diagram and state table 00 01 11 10 Lan-Da Van DCD-05-44 Digital Circuit Design Sequence Detector Using D Flip-Flops Lan-Da Van Lecture 5 DCD-05-45 Digital Circuit Design Sequence Detector Using D Flip-Flops Lecture 5 The flip-flop input equations A(t+1) = DA(A,B,x) = S(3,5,7) B(t+1) = DB(A,B,x) = S(1,5,7) The output equation y(A,B,x) = S(6,7) Logic minimization using the K map DA= Ax + Bx DB= Ax + B'x y = AB Lan-Da Van DCD-05-46 Digital Circuit Design Sequence Detector Using D Flip-Flops Lecture 5 The logic diagram Lan-Da Van DCD-05-47 Digital Circuit Design Excitation Tables Lecture 5 A state diagram flip-flop input functions straightforward for D flip-flops we need excitation tables for JK and T flip-flops Lan-Da Van DCD-05-48 Digital Circuit Design Synthesis Using JK Flip-Flops Lecture 5 The state table and JK flip-flop inputs Lan-Da Van DCD-05-49 Digital Circuit Design Synthesis Using JK Flip-Flops Lecture 5 Lan-Da Van DCD-05-50 Digital Circuit Design Synthesis Using JK Flip-Flops Lecture 5 Lan-Da Van DCD-05-51 Digital Circuit Design 3-Bit Binary Counter Using T Flip-Flops Lecture 5 An n-bit binary counter the state diagram no inputs (except for the clock input) Lan-Da Van DCD-05-52 Digital Circuit Design 3-Bit Binary Counter Using T Flip-Flops Lecture 5 The state table and the flip-flop inputs 0 Lan-Da Van DCD-05-53 Digital Circuit Design 3-Bit Binary Counter Using T Flip-Flops Lecture 5 Lan-Da Van DCD-05-54 Digital Circuit Design 3-Bit Binary Counter Using T Flip-Flops Lecture 5 Logic simplification using the K map TA2 = A1A0 TA1 = A0 TA0 = 1 The logic diagram Lan-Da Van DCD-05-55 Digital Circuit Design Conclusion Lecture 5 From this lecture, you have learned the follows: Storage Elements: SR Latch, D Latch Storage Elements: D Flip-Flop, JK Flip-Flop, T FlipFlop Analysis of Clocked Sequential Circuits State Reduction and Assignment Design Procedure Lan-Da Van DCD-05-56