Ch 4. Processor Architecture ISA Topics to cover

advertisement

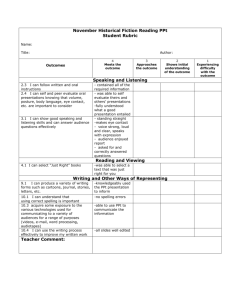

Ch 4. Processor Architecture Topics • Y86 ISA (Instruction Set Architecture) • Digital Logic • HCL • Sequential Y86 Implementation Wc11.arch.ppt ISA Instruction Set Architecture • Instructions supported by a particular processor and their byte-level encodings • Different families of processors, such as x86, PowerPC, Sparc, Alpha, HP-PA, MIPS, and Itanium have different ISAs. • There are many different models (or implementations) of processors within a single family. Micro-architecture • Various performance enhancement techniques pipelining, caching, branch prediction, OOO Wc11.arch.ppt 2 ENCE 3241 Topics to cover A Simple Instruction Set: Y86 • fewer data types, instructions and addressing modes • simpler byte-level encoding Digital Logic Design • • • • • • logic gates combinational logic multiplexer and decoder PLA finite state machines HCL (Hardware Control Language) Sequential Y86 Implementation • Organizing Processing into stages • SEQ stage implementation Wc11.arch.ppt 3 ENCE 3241 Y86 ISA IA-32/Y86 %eax %ecx %edx %ebx %esp %ebp %esi %edi Programmer-Visible State Register File Eight registers PC %eip Condition Codes Three single bit CC: OF,ZF,SF Memory %eip (PC) a large array of bytes OF Wc11.arch.ppt ZF ENCE 3241 4 Byte nop 0 0 0 halt 1 0 rrmovl rA, rB 2 0 rA rB irmovl V, rB 3 0 8 rB V rmmovl rA, D(rB) 4 0 rA rB D mrmovl D(rB), rA 5 0 rA rB D OPl 6 fn rA rB rA, rB 1 2 3 jXX Dest 7 fn Dest call Dest 8 0 Dest ret 9 0 A 0 rA 8 B 0 rA 8 pushl popl Wc11.arch.ppt SF rA rA 4 5 5 ENCE 3241 Byte-level encoding • Each instruction requires between 1 and 6 bytes • Every instruction has an initial byte to identify the instruction type. This byte has two parts: code part and function part. • Each register has an identifier: e.g. %eax is register 0, %ecx is register 1. Register 8 means no register is used. • Some instructions require four byte constant word to encode • immediate data, • displacement for address specifier, • destination of branches and calls. • Byte level encodings must have a unique interpretation. Wc11.arch.ppt 6 ENCE 3241 Operation Codes for Y86 Instruction Set The initial byte identifies the instruction type. This byte is split into two 4-bit parts: the operation code (OP Code) and the function code (FN Code). example: OP FN addl 0110 0000 xorl 0110 0011 OP code 0 nop 1 halt 2 rrmove 3 irmove 4 rmmove 5 mrmove 6 int op 7 jump/branch 8 call 9 ret A push B pop Wc11.arch.ppt ENCE 3241 7 Function Codes for Y86 Instruction Set Integer Operations Jump/Branches addl subl andl xorl jmp jle jl je jne jge jg 60 61 62 63 Wc11.arch.ppt 70 71 72 73 74 75 76 ENCE 3241 8 Y86 Register Identifier %eax %ecx %edx %ebx %esi %edi %esp %ebp Wc11.arch.ppt 9 (0) (1) (2) (3) (6) (7) (4) (5) ENCE 3241 Byte nop 0 0 0 halt 1 0 rrmovl rA, rB 2 0 rA rB irmovl V, rB 3 0 8 rB V rmmovl rA, D(rB) 4 0 rA rB D mrmovl D(rB), rA 5 0 rA rB D OPl 6 fn rA rB jXX Dest 7 fn Dest call Dest 8 0 Dest ret 9 0 A 0 rA 8 B 0 rA 8 rA, rB pushl popl rA rA 1 2 Wc11.arch.ppt 3 4 5 %eax %ecx %edx %ebx %esi %edi %esp %ebp (0) (1) (2) (3) (6) (7) (4) (5) ENCE 3241 10 Byte-level encoding Practice Example: (see textbook for encodings) What is the byte encoding of the following instructions 30 83 %ebx 0F 00 00 00 irmovl $15, rrmovl %ebx, %ecx 20 31 addl %eax, %ecx 60 01 rmmovl %ecx, 4(%ebx) 40 13 04 00 00 00 Wc11.arch.ppt 12 ENCE 3241 Byte-level encoding Practice Example: For the following byte sequence, determine the Y86 instruction sequence it encodes. 30 80 0F 00 00 00 61 43 00 20 10 62 10 30 80 0F 00 00 00 61 43 00 20 10 Wc11.arch.ppt 13 ENCE 3241 Byte-level encoding Practice Example: There is an illegal instruction in the following byte sequence. Which one is it? 30 81 01 00 00 00 00 43 00 00 10 00 00 Wc11.arch.ppt 15 ENCE 3241 Exercise 1) What if Y86 has 256 general purpose registers? 2) If Y86 support three operand registers such as OP rA,rB,rC rA = rB op rC will it fit in the current instruction format? 3) What if Y86 is a 64-bit architecture? 4) Y86 is far too simple, what instructions should we add? 5) What if Y86 supports only fixed length instructions? How long should the length be? Wc11.arch.ppt 17 ENCE 3241 Exercise 1) What if Y86 has 256 general purpose registers? It takes 8 bits to specify rA and rB, so instruction Rrmove, irmove, rmmove, mrmove, operations, push and pop will need one more byte in encoding 2) If Y86 support three operand registers such as OP rA,rB,rC rA = rB op rC will it fit in the current instruction format? It takes 9 bits to specify all three registers. The current register specifier has only one byte, insufficient for three registers. Wc11.arch.ppt 18 ENCE 3241 Brief Review of Elements of Digital Logic Wc11.arch.ppt 20 ENCE 3241 Wc11.arch.ppt 40 ENCE 3241 We can “blow” the fuses to create any logic circuit that we want. AC + A’B’ Wc11.arch.ppt 41 A’B’ + ABC’ ENCE 3241 We Often Illustrate the PLA Like This A B C F0 AC + A’B’ F1 A’B’ + ABC’ Wc11.arch.ppt 42 ENCE 3241 Wc11.arch.ppt 44 ENCE 3241 Wc11.arch.ppt 45 ENCE 3241 Wc11.arch.ppt ENCE 3241 46 Carry-In A B Sum Carry-out 0 0 0 0 0 0 0 1 1 0 0 1 0 1 0 0 1 1 0 1 1 0 0 1 0 1 0 1 0 1 1 1 0 0 1 1 1 1 1 1 Sum = A’BC’ + AB’C’ + A’B’C + ABC Carry-out = ABC’ + A’BC + AB’C + ABC Wc11.arch.ppt 47 ENCE 3241 The single input line into each AND gate represents 6 input lines The single input line into each OR gate represents 8 lines Darkened circles are placed at crosspoints to indicate connections are made Sum = A’BC’ + AB’C’ + A’B’C + ABC Wc11.arch.ppt 48 ENCE 3241 Wc11.arch.ppt 49 ENCE 3241 Wc11.arch.ppt 50 ENCE 3241 Wc11.arch.ppt 51 ENCE 3241 When A,B,C all changed from 0 to 1, there will Be a glitch. Wc11.arch.ppt 52 ENCE 3241 Wc11.arch.ppt 55 ENCE 3241 Finite State Machine from Sequential Logic Wc11.arch.ppt 64 ENCE 3241 Wc11.arch.ppt 65 ENCE 3241 Wc11.arch.ppt 66 ENCE 3241 Finite State Machine X1 X0 4X5 PLA Q D S0 Z2 Z1 Z0 CLK Q D S1 Wc11.arch.ppt 67 ENCE 3241 Truth Table for Vending Machine S1 0 0 0 0 0 0 1 1 1 1 1 1 S0 0 0 0 1 1 1 0 0 0 1 1 1 X1 0 0 1 0 0 1 0 0 1 0 0 1 X0 0 1 0 0 1 0 0 1 0 0 1 0 S1 0 1 0 1 1 0 1 0 0 0 0 0 Wc11.arch.ppt S0 1 0 0 0 1 0 1 0 0 0 0 1 Z0 0 0 1 0 0 1 0 1 1 1 1 1 Z1 0 0 1 0 0 0 0 0 1 0 1 1 Z2 0 0 0 0 0 1 0 0 1 0 0 1 ENCE 3241 68 Example • Assume our vending machine takes only nickels and dimes. • The machine vends items for 15 cents. • What is the state transition diagram? Wc11.arch.ppt ENCE 3241 69 Example • Assume our vending machine takes only nickels and dimes. • The machine vends items for 15 cents. • What is the state transition diagram? B 5 cent D/11 N/00 N/00 D/10 C 10 cent A 0 cent N/10 N/D: Nickel or Dime 0/1: dispense or not 0/1: return nickel or not D/00 Wc11.arch.ppt 70 ENCE 3241