FETs: Field Effect Transistors

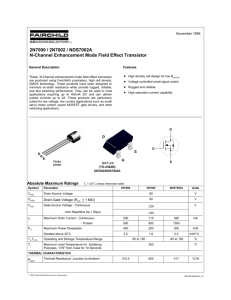

advertisement

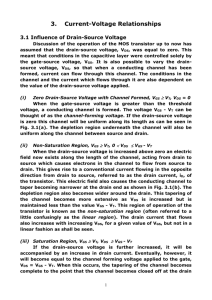

FETs: Field Effect Transistors • MOSFETs: Metal-Oxide Semiconductor Field Effect Transistors •gates are really polysilicon, not metal •extremely large input resistance •four terminal devices •occupy less area than BJTs --- predominant technology for digital •but do not provide the same gain as BJTs for analog • Used for analog mainly due to the need mixed-signal designs • JFETs: Junction Field Effect Transistors •not as popular as MOSFETs, but behave very similarly Lecture 19-1 Enhancement Mode MOSFETs • The basic structure of an enhancement mode mosfet Made of polysilicon or rarely metal. The oxide is very thin: e.g. 40 - 15 nm. h dt W i w l e n an ch n+ p n+ channel length L • Cross-section view source G gate drain S B D body Channel Lecture 19-2 Enhancement Mode MOSFETs • NOTE: 4 terminals!!! S D G B S n-channel transistor or N-MOSFET (p-type substrate) G B D p-channel transistor or P-MOSFET (n-type substrate) Lecture 19-3 Enhancement Mode MOSFETs • We keep the source and drain p-n junctions off at all times • They contribute small leakage currents, and some nonlinear capacitance G S D n+ n+ p B • The gate input has practically infinite resistance, and behaves like a capacitor G S idc=0 D n+ n+ p B Lecture 19-4 Enhancement Mode MOSFETs • Depletion regions around the p-n junctions due to the built-in voltages • With all of the voltages set to zero, the S-B-D connections form an NPN S G D n+ n+ p B • Even with a postive drain voltage, there is no significant current flow +G S n+ vDS D n+ p B Lecture 19-5 Enhancement Mode MOSFETs • The gate is used to establish a connection between the source and drain nodes • Postive gate voltage (for this NMOS enhancement transistor): •sets up an electric field from gate to bulk which tends to repel positive charges in the p-type bulk and create a depletion region •negative charge from the source and drain regions is attracted toward the channel by the same electric field +- vGS Lecture 19-6 Enhancement Mode MOSFETs • Gate to bulk acts like a capacitor ++ + QG + vGS + - - QB - p Lecture 19-7 Inversion • When the VGS grows high enough, there is not enough holes at the surface to allow for electron recombination. QB becomes a negative fixed charge with density equal to NAof the bulk. • Additional gate voltage causes the free electrons to be drawn to the surface of the channel --- forming an inversion layer. When concentration of electrons at surface equals NA we talk about strong inversion. Additional negative charge now comes from electrons in the channel. +- vGS + + ++ QG+ + + ++ - - - - - - QB - - - - QB p Lecture 19-8 Threshold Voltage • The gate voltage required to create strong inversion • If there is a small potential difference between the drain and source, then a current will flow across the inversison layer which acts like a resistor vGS vDS _ ++ iS=iD _ ++ iD iD Lecture 19-9 Flatband Voltage -- V FB • There is a depletion region (negative Q) under the channel even with VGS = 0 •Due to dangling bonds at the material interfaces and unwanted positive charges at the surfaces and in the oxides 0v +- • The flatband voltage (generally negative) is the gate voltage required to exactly cancel this charge +- vFB Lecture 19-10 Threshold Voltage • The threshold voltage is the flatband voltage plus whatever voltage is required to cause inversion in the channel VG + _ + Vox VDEPLETION n+ n+ _ VB Lecture 19-11 Threshold Voltage • Once -QB = NA, then further increases in gate voltage brings about the inversion layer • The depletion charge and voltage becomes fixed at a value called respecitively: QB0 and 2φf • Increases in channel charge correspond to the inversion layer charge, QI VG ++ n+ QB0 2φ f _ n+ VB Lecture 19-12 Threshold Voltage • Assuming VB and VS are both zero, the threshold voltage is: V t0 = V G threshold = V OX + V DEPL + V FB VG VS = 0 ++ n+ 2φ f _ QB0 n+ VB = 0 Lecture 19-13 Strong Inversion • With a small positive drain voltage, the inversion layer charge will drift from source to drain VG > Vt VS = 0 VDS > 0 + n+ QI QB0 n+ VB = 0 • The conductance of the layer is proportional to VGS - Vt Lecture 19-14 Inversion Layer Conductance • Triode or linear region of operation • Example: W=L=1 micron 0.0 0.1 VDS 0.2 IDS (µA) 20 10 G ~ VGS - Vt VGS=2.5V VGS=2.0V VGS=1.5V 0 VGS=1.0V Lecture 19-15 Pinch-Off Region --- Saturation • The conductance is not always proportional to VGS-Vt for all VDS • As VDS increases, the bulk charge closer to the drain increases, and the inversion layer charge there decreases • Conductance varies with position along the channel VG > Vt VS = 0 VDS >> 0 + QI n+ n+ QB VB = 0 Lecture 19-16 Pinch-Off Region --- Saturation • As VDS increases further for a fixed VGS, the inversion layer eventually goes to zero at the drain edge of the channel --- pinch-off VG > Vt VS = 0 VDS >> 0 + QI n+ n+ QB VB = 0 • Current is considered to saturate at this point since further increases in VDS do not increase the current significantly V DS sat˙ ≅ V GS – V t why? Lecture 19-17 Saturation Region • Region of interest for analog design • W=1 micron and L=10 microns 0 1 2 3 4 VDS 5 5 VGS=3.0V IDS (µA) triode region 4 3 saturation region VGS=2.5V 2 1 VGS=2.0V VGS=1.5V 0 VGS=1.0V Here, staturation means “current saturation” which is different than “voltage saturation” in bipolar transistors Lecture 19-18 Equations • Triode region equations for enhancement mode N-MOSFET v GS ≥ V t v DS ≤ v GS – V t 2 i D = K [ 2 ( v GS – V t )v DS – v DS ] W 1 K = --- µ n C ox ----L 2 In SPICE: K n = µ n C ox A ------2 V • For very small vDS, as on page 15, what is rDS? Lecture 19-19 Equations • Saturation region equations for enhancement mode N-MOSFET v GS ≥ V t v DS ≥ v GS – V t 2 i D = K [ 2 ( v GS – V t )v DS – v DS ] v DS i D = K [ ( v GS – V t ) ] 2 sat = v GS – V t W K = ------K n 2L K n = C ox µ n • Current varies quadratically with vGS Lecture 19-20 Saturation • For v DS ≥ v GS – V t 0 1 2 3 4 VGS 5 IDS (µA) 20 W=1 micron L=10 microns V t0= 1 volt 2 K n=2e-5 (A/v ) 10 0 D G • Large signal model in saturation + id K ( v GS – V t ) _ 2 S Lecture 19-21 Saturation --- Channel Length Modulation • VDS at the edge of the inversion layer remains fixed at VGS-Vt • But the effective length of the channel decreases with increasing VDS • Especially a factor when channel length is short VG > Vt VS = 0 VDS >> 0 + L ∆L n+ n+ VB = 0 K nW 2 iD = ------------------------- [ ( v GS – V t ) ] 2 ( L – ∆L ) sat Lecture 19-22 Saturation --- Channel Length Modulation • Sometimes expressed in terms of channel length modulation parameter K nW 2 iD = ------------- [ ( v GS – V t ) ] ( 1 + λv DS ) 2L sat • SPICE can calculate the modulation for you... 0 1 2 3 4 VDS 5 100 VGS=3.0V IDS (µA) 80 60 VGS=2.5V 40 W=1 micron L=1 microns V t0= 1 volt 2 K n=2e-5 (A/v ) phi =0.6 N A=1e15 VGS=2.0V 20 VGS=1.5V 0 VGS=1.0V Lecture 19-23 Saturation --- Channel Length Modulation • Or we can specify lambda explicitly in the model K nW 2 = ------------- [ ( v GS – V t ) ] ( 1 + λv DS ) iD 2L sat VDS 0 60 1 2 3 4 5 VGS=3.0V IDS (µA) 50 40 VGS=2.5V 30 W=1 micron L=1 microns V t0= 1 volt 2 K n=2e-5 (A/v ) lambda = 0.8 20 VGS=2.0V 10 0 VGS=1.5V VGS=1.0V Lecture 19-24 Output Resistance • We can add a resistor to model the channel length modulation effect for the large-signal model in saturation G + _ id D K ( v GS – V t ) 2 ro S • What is the value of ro? ∂i DS ro = ∂ v DS –1 2 –1 W 1 = λK n ------ ( V GS – V t ) ≈ ----------------2L λI Dsat Lecture 19-25