MSI logic circuits

MSI logic circuits bvhieu@cse.hcmut.edu.vn

Department of Computer Engineering

Ho Chi Minh City University of Technology

Copyright © 2013, Bui Van Hieu – All rights reserved

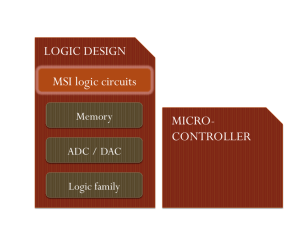

LOGIC DESIGN

MSI logic circuits

MICRO-

CONTROLLER

Encoder / Decoder

Multiplexer /

Demultiplexer

Data busing

Content

What is an encoder / decoder ?

N inputs

M outputs

1 of 2 N

N inputs 2 N outputs

Inputs represent a binary number

Activate only one output corresponding

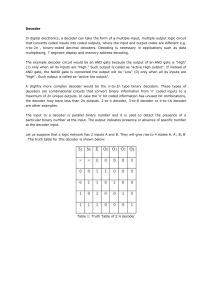

C (MS

B)

0

0

B

0

0

A

0

1

0

1

1

1

1

1

0

0

1

1

1

0

1

0

1

1-of-8 (3-to-8) decoder

O7 O6 O5 O4 O3 O2 O1 O0

1

1

1

1

1

1

1

1

1

1

1

1

1 0

0 1

1-of-8 decoder circuit

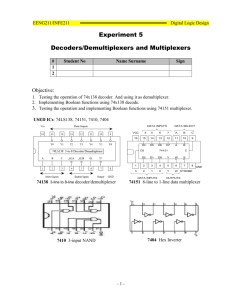

1-of-8 decoder IC (74138)

Exercises

Determine outputs of 74xx138

E

3

=E

2

=E

1

=0 A

2

=A

1

=0 A

0

=0

E =1, E

2

=E

1

=0 A =0

74138 circuit

Implement

5-to-32 decoder from four

Problems 1

5 inputs

.

.

.

32 outputs

7442 IC (4-to-10 decoder)

All of outputs are deactivated if an invalid input is applied

(1010 1111)

Application example

Provide timing and sequencing operations

BCD-to-7-segment Decoder/Driver

Form the decimal characters 0 9

Each segment is a LED

Normal brightness: 10mA, 2.7V

Exercises

Determines outputs for each case

Inputs DCBA = 1001

Inputs DCBA = 0110

Inputs DCBA = 0011

Inputs DCBA = 0000

D is the most significant bit

7446/7447 BCD-to-7-segment decoder

7446/7447 truth table

Problem 2

Implement 7446/7447 by logic gates

Encoder

The opposite of decoding process

Depend on the context, terms encoder and decoder are interchangeable

2 N -line-to-N-line encoder

2 N inputs

Only one input is activated at a given time

Produces a N-bit binary code

8-to-3 encoder

A7 A6 A5 A4 A3 A2 A1 A0

1 1 1 1 1 1 1 0

1 1 1 1 1 1 0 1

1 1 1 1 1 0 1 1

1 1 1 1 0 1 1

1 1 1 0 1 1 1

1 1 0 1 1 1 1

1 0 1 1 1 1 1

0 1 1 1 1 1 1

1

1

1

1

1

O2 O1 O0

0 0 0

0 0 1

8-to-line encoder

More than one inputs are activated?

74147 Decimal-to-BCD Priority

Encoder

More than one input is activated, output code respond to the highest-numbered input

Exp: A6, A2, A0 are activated output code is

110 (6)

Exercises

Determine outputs of 74147 if A

9

-A

0 inputs are

1110111111

, A

3

All low except A

9

, A

1

, A

0

Example – Switch encoder

Example

3 groups

Each group stores code of pressed key

Magnitude comparator

Compare two input binary quantities

Generate outputs to indicate which one is greater

7485 truth table

Exercise

Problem 3

Implement the comparator by logic gates

8-bit magnitude comparator

12, 16 … bit comparator ?

Exercise

Describe operation of the 8-bit comparator for the following cases

A

7

A

6

A

5

A

4

A

3

A

2

A

1

A

0

B

7

B

6

B

5

B

4

B

3

B

2

B

1

B

0

= 10101111

= 10110001

A

7

A

6

A

5

A

4

A

3

A

2

A

1

A

0

B

7

B

6

B

5

B

4

B

3

B

2

B

1

B

0

= 10101111

= 10101111

A

7

A

6

A

5

A

4

A

3

A

2

A

1

A

0

B

7

B

6

B

5

B

4

B

3

B

2

B

1

B

0

= 10101111

= 10101001

Application example

Code converter

Change data presented in one type of binary code to another type of binary code

BCD to binary

Binary to BCD

Binary to Gray code

Gray code to binary

…

Encoder /

Decoder

Multiplexer /

Demultiplexer

Data busing

Content

Multiplexers (MUX - Data

Selectors)

Select one inputs to pass on to the output

Desired input is controlled by SELECT inputs

S I1 I0

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

Z

0

1

Two-input multiplexer

Z = I

0

S’ + I

1

S

Four-input multiplexer

Problem 4

Implement eight-input multiplexer with enable signal (74151)

Sixteen-input multiplexer

Quad Two-Input MUX (74157)

Application – Data routing select = 0 select = 1

Applications – Parallel to serial

Applications – Logic function generation

Problem 5: combine Enable signal to generate 4-input logic functions

Select : input variables

Data : connect 0 or 1 (based on truth table)

Example – Control system

Demultiplexers (Data distributor)

Revert of MUX

I

S1 S0

O3

O2

O1

O0

1-to-4 demultiplexer

S1 S0 I

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

O3 O2 O1 O0

0 0 0 0

0 0 0 1

1-to-8 demultiplexer

DEMUX vs. 1-to-N decoder

Application – Synchronous data transmission

Waveform

Real application examples

Encoder /

Decoder

Multiplexer /

Demultiplexer

Data busing

Content

Bus ?

Bus ?

Common connecting lines for data transferring

Many devices connect their inputs/outputs

Device 0 Device 1 Device 2

Data bus

Device 3 Device 4

Open collector

74173 circuit

Example

Signal sequence

t1 : reg. A outputs are enabled

t2 : reg. C inputs data

t3 : reg. A outputs are disabled, data bus return to Hi-Z state

Expanding bus size

Bus representation

Bidirectional busing

Review questions

Can more than one decoder output be active at one time?

What is the function of a decoder’s enable input?

How does a priority encoder differ from an ordinary encoder?

What are the functions of a multiplexer ?

What are some major applications of a multiplexer?

Problems

1 3 4 5 (7 40) 8 9

13 14 15 16

27 29 30 31 (33 34) 35 36 37

38 (all students)

39 41 43 44

45*

56 57 58 59 60 61 62

Examiner

Each group must solve all the problems

Write down the problems and solutions

Other group will comment