\\VHDL Program for Two input And GATE\\

advertisement

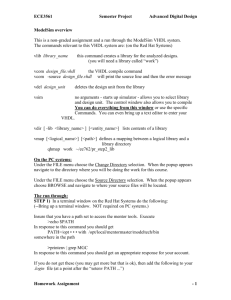

NAME OF LABORATORY: LAB SUBJECT CODE: NAME OF DEPARTMENT: VLSI Lab EC-606 Electronics and Comm. EXPERIMENT NO.1 VHDL Program for Two inputs OR GATE Date of conduction:- Date of submission:- Submitted by other members:1. 2. 3. 4. 5. 6. 7. 8. Group no:- Signature Name of faculty incharge: Name of Technical Assistant: Department of Electronics and Communication 46 EC-606 Lab Manual Page 1 of Objective: - Write a VHDL Program for two input OR Gate Apparatus:1. VHDL Simulation Software (Modelsim/Xilinx) 2. Personal Computer Theory: - Procedure: 1. Open VHDL project by File-> Open->Open Project-> vhdl.mpf 2. Open source code window using View->Source 3. Type Program source code and save it using File->Save as -> <Name>.vhd 4. Compile the program using File->Compile 5. If any error then read the error message and debug the source code. 6. After successful compilation load the design by Design->Load New Design. 7. Now open signal window by using View->Signals. 8. Apply inputs by using Edit->Clock with these properties time period 100 µs, 200 µs, 400 µs and first edge is Falling Edge. 9. View the output waveform by View->Signals in Region. Department of Electronics and Communication 46 EC-606 Lab Manual Page 2 of 10. In Waveform windows press the Run Button multiple times to get the required output wave form. 11. Place the cursor for each entry of truth table and get Results: Print out of output waveform is attached. Conclusion:Output waveform of the design is verified with truth table. Precautions:1. Open vhdl project compulsorily. 2. Type the program in lowercase. 3. Save the file with .vhd extension. 4. The file name does not white space character. 5. Check proper print setting before taking printout. Suggestions:1. Try different type modeling approach for the same design. 2. Observe the delay. Lab Quiz :1. Design the schematic diagram for this design using universal gate. 2. Write the Boolean expression of the design. 3. Apply the Demorgan law on the design. 4. Calculate the total time delay of design. 5. List the all error you have faced to execute this design. Further reading resources: Book: Lab experiment related theory available in following books: Book Name 1. Circuit Design with VHDL Author Page No. Volnei A. Pedroni - 2. VHDL : Programming By Example Douglas L. Perry - Department of Electronics and Communication 46 EC-606 Lab Manual Page 3 of 3. Verilog HDL Primer –synthesis Bhasker - Web resources: 1. http://cis.poly.edu/cs2204/vhdlprg.pdf 2. esd.cs.ucr.edu/labs/tutorial/ 3. www.ccessengineeringlibrary.com 4. www.etidweb.tamu.edu 1. library IEEE; 2. use IEEE.std_logic_1164.all; 3. entity or2 is 4. port(a,b:in bit; c:out bit); 5. end or; 6. architecture data of or2 is 7. begin 8. c <= a or b; 9. end data; Department of Electronics and Communication 46 EC-606 Lab Manual Page 4 of EXPERIMENT NO.2 VHDL Program for Two inputs AND GATE Date of conduction:- Date of submission:- Submitted by other members:1. 2. 3. 4. 5. 6. 7. 8. Group no:- Signature Name of faculty incharge: Name of Technical Assistant: Objective: - Write a VHDL Program for two input OR Gate Department of Electronics and Communication 46 EC-606 Lab Manual Page 5 of Apparatus:3. VHDL Simulation Software (Modelsim/Xilinx) 4. Personal Computer Theory: - Procedure: 12. Open VHDL project by File-> Open->Open Project-> vhdl.mpf 13. Open source code window using View->Source 14. Type Program source code and save it using File->Save as -> <Name>.vhd 15. Compile the program using File->Compile 16. If any error then read the error message and debug the source code. 17. After successful compilation load the design by Design->Load New Design. 18. Now open signal window by using View->Signals. 19. Apply inputs by using Edit->Clock with these properties time period 100 µs, 200 µs, 400 µs and first edge is Falling Edge. 20. View the output waveform by View->Signals in Region. 21. In Waveform windows press the Run Button multiple times to get the required output wave form. Department of Electronics and Communication 46 EC-606 Lab Manual Page 6 of 22. Place the cursor for each entry of truth table and get Results: Print out of output waveform is attached. Conclusion:Output waveform of the design is verified with truth table. Precautions:6. Open vhdl project compulsorily. 7. Type the program in lowercase. 8. Save the file with .vhd extension. 9. The file name does not white space character. 10. Check proper print setting before taking printout. Suggestions:3. Try different type modeling approach for the same design. 4. Observe the delay. Lab Quiz :6. Design the schematic diagram for this design using universal gate. 7. Write the Boolean expression of the design. 8. Apply the Demorgan law on the design. 9. Calculate the total time delay of design. 10. List the all error you have faced to execute this design. Further reading resources: Book: Lab experiment related theory available in following books: Book Name 4. Circuit Design with VHDL Author Page No. Volnei A. Pedroni - 5. VHDL : Programming By Example Douglas L. Perry - 6. Verilog HDL Primer –synthesis Department of Electronics and Communication 46 Bhasker EC-606 Lab Manual - Page 7 of Web resources: 1. http://cis.poly.edu/cs2204/vhdlprg.pdf 2. esd.cs.ucr.edu/labs/tutorial/ 3. www.ccessengineeringlibrary.com 4. www.etidweb.tamu.edu 1 library IEEE; 2 use IEEE.std_logic_1164.all; 3 entity and2 is 4 port (a,b:in bit;c:out bit); 5 end and2; 6 architecture data of and2 is 7 begin 8 c <=a and b; 9 end data; Department of Electronics and Communication 46 EC-606 Lab Manual Page 8 of EXPERIMENT NO.3 VHDL Program for Two inputs OR NOR GATE Date of conduction:- Date of submission:- Submitted by other members:1. 2. 3. 4. 5. 6. 7. 8. Group no:- Signature Name of faculty incharge: Name of Technical Assistant: Department of Electronics and Communication 46 EC-606 Lab Manual Page 9 of Objective: - Write a VHDL Program for two input NOR GATE Apparatus:5. VHDL Simulation Software (Modelsim/Xilinx) 6. Personal Computer Theory: - Procedure: 23. Open VHDL project by File-> Open->Open Project-> vhdl.mpf 24. Open source code window using View->Source 25. Type Program source code and save it using File->Save as -> <Name>.vhd 26. Compile the program using File->Compile 27. If any error then read the error message and debug the source code. 28. After successful compilation load the design by Design->Load New Design. 29. Now open signal window by using View->Signals. 30. Apply inputs by using Edit->Clock with these properties time period 100 µs, 200 µs, 400 µs and first edge is Falling Edge. 31. View the output waveform by View->Signals in Region. 32. In Waveform windows press the Run Button multiple times to get the required output wave form. Department of Electronics and Communication 46 EC-606 Lab Manual Page 10 of 33. Place the cursor for each entry of truth table and get Results: Print out of output waveform is attached. Conclusion:Output waveform of the design is verified with truth table. Precautions:11. Open vhdl project compulsorily. 12. Type the program in lowercase. 13. Save the file with .vhd extension. 14. The file name does not white space character. 15. Check proper print setting before taking printout. Suggestions:5. Try different type modeling approach for the same design. 6. Observe the delay. Lab Quiz :11. Design the schematic diagram for this design using universal gate. 12. Write the Boolean expression of the design. 13. Apply the Demorgan law on the design. 14. Calculate the total time delay of design. 15. List the all error you have faced to execute this design. Further reading resources: Book: Lab experiment related theory available in following books: Book Name 7. Circuit Design with VHDL Author Page No. Volnei A. Pedroni - 8. VHDL : Programming By Example Douglas L. Perry - 9. Verilog HDL Primer –synthesis Department of Electronics and Communication 46 Bhasker EC-606 Lab Manual - Page 11 of Web resources: 1. http://cis.poly.edu/cs2204/vhdlprg.pdf 2. esd.cs.ucr.edu/labs/tutorial/ 3. www.ccessengineeringlibrary.com 4. www.etidweb.tamu.edu 10. library IEEE; 11. use IEEE.std_logic_1164.all; 12. entity nor2 is 13. port(a,b:in bit; c:out bit); 14. end nor2; 15. architecture data of nor2 is 16. begin 17. c <= NOT (a or b); 18. end data; Department of Electronics and Communication 46 EC-606 Lab Manual Page 12 of EXPERIMENT NO.5 VHDL Program for Three input OR GATE Date of conduction:- Date of submission:- Submitted by other members:1. 2. 3. 4. 5. 6. 7. 8. Group no:- Signature Name of faculty incharge: Name of Technical Assistant: Objective: - Write a VHDL Program for three input OR Gate Department of Electronics and Communication 46 EC-606 Lab Manual Page 13 of Apparatus:7. VHDL Simulation Software (Modelsim/Xilinx) 8. Personal Computer Theory: - Procedure: 34. Open VHDL project by File-> Open->Open Project-> vhdl.mpf 35. Open source code window using View->Source 36. Type Program source code and save it using File->Save as -> <Name>.vhd 37. Compile the program using File->Compile 38. If any error then read the error message and debug the source code. 39. After successful compilation load the design by Design->Load New Design. 40. Now open signal window by using View->Signals. 41. Apply inputs by using Edit->Clock with these properties time period 100 µs, 200 µs, 400 µs and first edge is Falling Edge. 42. View the output waveform by View->Signals in Region. 43. In Waveform windows press the Run Button multiple times to get the required output wave form. Department of Electronics and Communication 46 EC-606 Lab Manual Page 14 of 44. Place the cursor for each entry of truth table and get Results: Print out of output waveform is attached. Conclusion:Output waveform of the design is verified with truth table. Precautions:16. Open vhdl project compulsorily. 17. Type the program in lowercase. 18. Save the file with .vhd extension. 19. The file name does not white space character. 20. Check proper print setting before taking printout. Suggestions:7. Try different type modeling approach for the same design. 8. Observe the delay. Lab Quiz :16. Design the schematic diagram for this design using universal gate. 17. Write the Boolean expression of the design. 18. Apply the Demorgan law on the design. 19. Calculate the total time delay of design. 20. List the all error you have faced to execute this design. Further reading resources: Book: Lab experiment related theory available in following books: Book Name Author Page No. 10. Circuit Design with VHDL - 11. VHDL : Programming By Example Douglas L. Perry - Department of Electronics and Communication 46 Volnei A. Pedroni EC-606 Lab Manual Page 15 of 12. Verilog Bhasker HDL Primer –synthesis - Web resources: 1. http://cis.poly.edu/cs2204/vhdlprg.pdf 2. esd.cs.ucr.edu/labs/tutorial/ 3. www.ccessengineeringlibrary.com 4. www.etidweb.tamu.edu 1 library IEEE; 2 use IEEE.std_logic_1164.all; 3 entity or3 Is 4 port(a,b,c:in bit; d:out bit); 5 end or3; 6 architecture data of or3 is 7 begin 8 d <= a or b or c; 9 end data; Department of Electronics and Communication 46 EC-606 Lab Manual Page 16 of EXPERIMENT NO.6 VHDL Program for three inputs AND GATE Date of conduction:- Date of submission:- Submitted by other members:1. 2. 3. 4. 5. 6. 7. 8. Group no:- Signature Name of faculty incharge: Name of Technical Assistant: Objective: - Write a VHDL Program for two input OR Gate Apparatus:- Department of Electronics and Communication 46 EC-606 Lab Manual Page 17 of 9. VHDL Simulation Software (Modelsim/Xilinx) 10. Personal Computer Theory: - Procedure: 45. Open VHDL project by File-> Open->Open Project-> vhdl.mpf 46. Open source code window using View->Source 47. Type Program source code and save it using File->Save as -> <Name>.vhd 48. Compile the program using File->Compile 49. If any error then read the error message and debug the source code. 50. After successful compilation load the design by Design->Load New Design. 51. Now open signal window by using View->Signals. 52. Apply inputs by using Edit->Clock with these properties time period 100 µs, 200 µs, 400 µs and first edge is Falling Edge. 53. View the output waveform by View->Signals in Region. 54. In Waveform windows press the Run Button multiple times to get the required output wave form. 55. Place the cursor for each entry of truth table and get Department of Electronics and Communication 46 EC-606 Lab Manual Page 18 of Results: Print out of output waveform is attached. Conclusion:Output waveform of the design is verified with truth table. Precautions:21. Open vhdl project compulsorily. 22. Type the program in lowercase. 23. Save the file with .vhd extension. 24. The file name does not white space character. 25. Check proper print setting before taking printout. Suggestions:9. Try different type modeling approach for the same design. 10. Observe the delay. Lab Quiz :21. Design the schematic diagram for this design using universal gate. 22. Write the Boolean expression of the design. 23. Apply the Demorgan law on the design. 24. Calculate the total time delay of design. 25. List the all error you have faced to execute this design. Further reading resources: Book: Lab experiment related theory available in following books: Book Name Author Page No. 13. Circuit Design with VHDL - Volnei A. Pedroni 14. VHDL : Programming By Example Douglas L. Perry - 15. Verilog HDL Primer –synthesis Bhasker - Department of Electronics and Communication 46 EC-606 Lab Manual Page 19 of Web resources: 1. http://cis.poly.edu/cs2204/vhdlprg.pdf 2. esd.cs.ucr.edu/labs/tutorial/ 3. www.ccessengineeringlibrary.com 4. www.etidweb.tamu.edu 1 library IEEE; 2 use IEEE.std_logic_1164.all; 3 entity and3 is 4 port(a,b,c:in bit; d:out bit); 5 end and3; 6 architecture data of and3 is 7 begin 8 d <= a and b and c; 9 end data; Department of Electronics and Communication 46 EC-606 Lab Manual Page 20 of EXPERIMENT NO.7 VHDL Program for four inputs OR GATE Date of conduction:- Date of submission:- Submitted by other members:1. 2. 3. 4. 5. 6. 7. 8. Group no:- Signature Name of faculty incharge: Name of Technical Assistant: Objective: - Write a VHDL Program for two input OR Gate Apparatus:- Department of Electronics and Communication 46 EC-606 Lab Manual Page 21 of 11. VHDL Simulation Software (Modelsim/Xilinx) 12. Personal Computer Theory: - Figure 1 Procedure: 56. Open VHDL project by File-> Open->Open Project-> vhdl.mpf 57. Open source code window using View->Source A 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 B 0 0 0 0 1 1 1 0 0 0 0 0 0 0 0 0 C 0 0 1 1 0 0 1 0 0 0 0 0 0 0 0 0 D 0 1 0 1 0 1 0 0 0 0 0 0 0 0 0 0 Z 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 58. Type Program source code and save it using File->Save as -> <Name>.vhd 59. Compile the program using File->Compile 60. If any error then read the error message and debug the source code. 61. After successful compilation load the design by Design->Load New Design. 62. Now open signal window by using View->Signals. 63. Apply inputs by using Edit->Clock with these properties time period 100 µs, 200 µs, 400 µs and first edge is Falling Edge. 64. View the output waveform by View->Signals in Region. 65. In Waveform windows press the Run Button multiple times to get the required output wave form. 66. Place the cursor for each entry of truth table and get Results: Print out of output waveform is attached. Conclusion:Output waveform of the design is verified with truth table. Precautions:Department of Electronics and Communication 46 EC-606 Lab Manual Page 22 of 26. Open vhdl project compulsorily. 27. Type the program in lowercase. 28. Save the file with .vhd extension. 29. The file name does not white space character. 30. Check proper print setting before taking printout. Suggestions:11. Try different type modeling approach for the same design. 12. Observe the delay. Lab Quiz :26. Design the schematic diagram for this design using universal gate. 27. Write the Boolean expression of the design. 28. Apply the Demorgan law on the design. 29. Calculate the total time delay of design. 30. List the all error you have faced to execute this design. Further reading resources: Book: Lab experiment related theory available in following books: Book Name Author Page No. 16. Circuit Design with VHDL - Volnei A. Pedroni 17. VHDL : Programming By Example Douglas L. Perry - 18. Verilog HDL Primer –synthesis Bhasker - Web resources: 1. http://cis.poly.edu/cs2204/vhdlprg.pdf 2. esd.cs.ucr.edu/labs/tutorial/ 3. www.ccessengineeringlibrary.com Department of Electronics and Communication 46 EC-606 Lab Manual Page 23 of 4. www.etidweb.tamu.edu 10 library IEEE; 11 use IEEE.std_logic_1164.all; 12 entity or4 Is 13 port(a,b,c,d:in bit; y:out bit); 14 end or4; 15 architecture data of or4 is 16 begin 17 d <= a or b or c or d; 18 end data; Department of Electronics and Communication 46 EC-606 Lab Manual Page 24 of EXPERIMENT NO.8 VHDL Program for Three inputs NAND GATE Date of conduction:- Date of submission:- Submitted by other members:1. 2. 3. 4. 5. 6. 7. 8. Group no:- Signature Name of faculty incharge: Name of Technical Assistant: Objective: - Write a VHDL Program for three input NAND Gate Apparatus:- Department of Electronics and Communication 46 EC-606 Lab Manual Page 25 of 13. VHDL Simulation Software (Modelsim/Xilinx) 14. Personal Computer Theory: - Procedure: 67. Open VHDL project by File-> Open->Open Project-> vhdl.mpf 68. Open source code window using View->Source 69. Type Program source code and save it using File->Save as -> <Name>.vhd 70. Compile the program using File->Compile 71. If any error then read the error message and debug the source code. 72. After successful compilation load the design by Design->Load New Design. 73. Now open signal window by using View->Signals. 74. Apply inputs by using Edit->Clock with these properties time period 100 µs, 200 µs, 400 µs and first edge is Falling Edge. 75. View the output waveform by View->Signals in Region. 76. In Waveform windows press the Run Button multiple times to get the required output wave form. 77. Place the cursor for each entry of truth table and get Department of Electronics and Communication 46 EC-606 Lab Manual Page 26 of Results: Print out of output waveform is attached. Conclusion:Output waveform of the design is verified with truth table. Precautions:31. Open vhdl project compulsorily. 32. Type the program in lowercase. 33. Save the file with .vhd extension. 34. The file name does not white space character. 35. Check proper print setting before taking printout. Suggestions:13. Try different type modeling approach for the same design. 14. Observe the delay. Lab Quiz :31. Design the schematic diagram for this design using universal gate. 32. Write the Boolean expression of the design. 33. Apply the Demorgan law on the design. 34. Calculate the total time delay of design. 35. List the all error you have faced to execute this design. Further reading resources: Book: Lab experiment related theory available in following books: Book Name Author Page No. 19. Circuit Design with VHDL - Volnei A. Pedroni 20. VHDL : Programming By Example Douglas L. Perry - 21. Verilog HDL Primer –synthesis Bhasker - Department of Electronics and Communication 46 EC-606 Lab Manual Page 27 of Web resources: 1. http://cis.poly.edu/cs2204/vhdlprg.pdf 2. esd.cs.ucr.edu/labs/tutorial/ 3. www.ccessengineeringlibrary.com 4. www.etidweb.tamu.edu 1 library IEEE; 2 use IEEE.std_logic_1164.all; 3 entity and4 is 4 port(a,b,c,d:in bit; y:out bit); 5 end and4; 6 architecture data of and4 is 7 begin 8 d <= a and b and c and d; 9 end data; Department of Electronics and Communication 46 EC-606 Lab Manual Page 28 of EXPERIMENT NO.9 VHDL Program for HALF ADDER Date of conduction:- Date of submission:- Submitted by other members:1. 2. 3. 4. 5. 6. 7. 8. Group no:- Signature Name of faculty incharge: Name of Technical Assistant: Objective: - Write a VHDL Program for two input OR Gate Department of Electronics and Communication 46 EC-606 Lab Manual Page 29 of Apparatus:15. VHDL Simulation Software (Modelsim/Xilinx) 16. Personal Computer Theory: - Procedure: 78. Open VHDL project by File-> Open->Open Project-> vhdl.mpf 79. Open source code window using View->Source 80. Type Program source code and save it using File->Save as -> <Name>.vhd 81. Compile the program using File->Compile 82. If any error then read the error message and debug the source code. 83. After successful compilation load the design by Design->Load New Design. 84. Now open signal window by using View->Signals. 85. Apply inputs by using Edit->Clock with these properties time period 100 µs, 200 µs, 400 µs and first edge is Falling Edge. 86. View the output waveform by View->Signals in Region. Department of Electronics and Communication 46 EC-606 Lab Manual Page 30 of 87. In Waveform windows press the Run Button multiple times to get the required output wave form. 88. Place the cursor for each entry of truth table and get Results: Print out of output waveform is attached. Conclusion:Output waveform of the design is verified with truth table. Precautions:36. Open vhdl project compulsorily. 37. Type the program in lowercase. 38. Save the file with .vhd extension. 39. The file name does not white space character. 40. Check proper print setting before taking printout. Suggestions:15. Try different type modeling approach for the same design. 16. Observe the delay. Lab Quiz :36. Design the schematic diagram for this design using universal gate. 37. Write the Boolean expression of the design. 38. Apply the Demorgan law on the design. 39. Calculate the total time delay of design. 40. List the all error you have faced to execute this design. Further reading resources: Book: Lab experiment related theory available in following books: Book Name 22. Circuit Design with VHDL - Department of Electronics and Communication 46 Author Page No. Volnei A. Pedroni EC-606 Lab Manual Page 31 of 23. VHDL : Programming By Example L. Perry 24. Douglas Verilog HDL Primer –synthesis Bhasker - Web resources: 1. http://cis.poly.edu/cs2204/vhdlprg.pdf 2. esd.cs.ucr.edu/labs/tutorial/ 3. www.ccessengineeringlibrary.com 4. www.etidweb.tamu.edu 1 library IEEE; 2 use IEEE.std_logic_1164.all; 3 entity half_adder is 4 port(a,b:in bit;sum,carry:out bit); 5 end half_adder; 6 architecture data of half_adder is 7 begin 8 sum <=a xor b; 9 carry <= a and b; 10 end data; Department of Electronics and Communication 46 EC-606 Lab Manual Page 32 of EXPERIMENT NO.10 VHDL Program for FULL ADDER Date of conduction:- Date of submission:- Submitted by other members:1. 2. 3. 4. 5. 6. 7. 8. Group no:- Signature Name of faculty incharge: Name of Technical Assistant: Objective: - Write a VHDL Program for two input OR Gate Department of Electronics and Communication 46 EC-606 Lab Manual Page 33 of Apparatus:17. VHDL Simulation Software (Modelsim/Xilinx) 18. Personal Computer Theory: - Procedure: 89. Open VHDL project by File-> Open->Open Project-> vhdl.mpf 90. Open source code window using View->Source 91. Type Program source code and save it using File->Save as -> <Name>.vhd 92. Compile the program using File->Compile Department of Electronics and Communication 46 EC-606 Lab Manual Page 34 of 93. If any error then read the error message and debug the source code. 94. After successful compilation load the design by Design->Load New Design. 95. Now open signal window by using View->Signals. 96. Apply inputs by using Edit->Clock with these properties time period 100 µs, 200 µs, 400 µs and first edge is Falling Edge. 97. View the output waveform by View->Signals in Region. 98. In Waveform windows press the Run Button multiple times to get the required output wave form. 99. Place the cursor for each entry of truth table and get Results: Print out of output waveform is attached. Conclusion:Output waveform of the design is verified with truth table. Precautions:41. Open vhdl project compulsorily. 42. Type the program in lowercase. 43. Save the file with .vhd extension. 44. The file name does not white space character. 45. Check proper print setting before taking printout. Suggestions:17. Try different type modeling approach for the same design. 18. Observe the delay. Lab Quiz :41. Design the schematic diagram for this design using universal gate. 42. Write the Boolean expression of the design. 43. Apply the Demorgan law on the design. 44. Calculate the total time delay of design. 45. List the all error you have faced to execute this design. Department of Electronics and Communication 46 EC-606 Lab Manual Page 35 of Further reading resources: Book: Lab experiment related theory available in following books: Book Name Author Page No. 25. Circuit Design with VHDL - Volnei A. Pedroni 26. VHDL : Programming By Example Douglas L. Perry - 27. Verilog HDL Primer –synthesis Bhasker - Web resources: 1. http://cis.poly.edu/cs2204/vhdlprg.pdf 2. esd.cs.ucr.edu/labs/tutorial/ 3. www.ccessengineeringlibrary.com 4. www.etidweb.tamu.edu 1 library IEEE; 2 use IEEE.std_logic_1164.all; 3 entity full_adder is 4 port(a,b,cin:in bit; sum,cout:out bit); 5 end full_adder; 6 architecture data of full_adder is 7 begin 8 process(a,b,cin) 9 begin Department of Electronics and Communication 46 EC-606 Lab Manual Page 36 of 10 sum <= (a xor b) xor cin; 11 cout <= (a and b) or (a and cin) or (b and cin); 12 end process; 13 end data; Department of Electronics and Communication 46 EC-606 Lab Manual Page 37 of EXPERIMENT NO.11 VHDL Program for Latch Date of conduction:- Date of submission:- Submitted by other members:1. 2. 3. 4. 5. 6. 7. 8. Group no:- Signature Name of faculty incharge: Name of Technical Assistant: Department of Electronics and Communication 46 EC-606 Lab Manual Page 38 of Objective: - Write a VHDL Program for two input OR Gate Apparatus:19. VHDL Simulation Software (Modelsim/Xilinx) 20. Personal Computer Theory: - Procedure: 100. Open VHDL project by File-> Open->Open Project-> vhdl.mpf 101. Open source code window using View->Source 102. Type Program source code and save it using File->Save as -> <Name>.vhd 103. Compile the program using File->Compile 104. If any error then read the error message and debug the source code. 105. After successful compilation load the design by Design->Load New Design. 106. Now open signal window by using View->Signals. 107. Apply inputs by using Edit->Clock with these properties time period 100 µs, 200 µs, 400 µs and first edge is Falling Edge. 108. View the output waveform by View->Signals in Region. 109. In Waveform windows press the Run Button multiple times to get the required output wave form. 110. Place the cursor for each entry of truth table and get Department of Electronics and Communication 46 EC-606 Lab Manual Page 39 of Results: Print out of output waveform is attached. Conclusion:Output waveform of the design is verified with truth table. Precautions:46. Open vhdl project compulsorily. 47. Type the program in lowercase. 48. Save the file with .vhd extension. 49. The file name does not white space character. 50. Check proper print setting before taking printout. Suggestions:19. Try different type modeling approach for the same design. 20. Observe the delay. Lab Quiz :46. Design the schematic diagram for this design using universal gate. 47. Write the Boolean expression of the design. 48. Apply the Demorgan law on the design. 49. Calculate the total time delay of design. 50. List the all error you have faced to execute this design. Further reading resources: Book: Lab experiment related theory available in following books: Book Name Author Page No. 28. Circuit Design with VHDL - Volnei A. Pedroni 29. VHDL : Programming By Example Douglas L. Perry - 30. Verilog HDL Primer –synthesis Bhasker - Department of Electronics and Communication 46 EC-606 Lab Manual Page 40 of Web resources: 1. http://cis.poly.edu/cs2204/vhdlprg.pdf 2. esd.cs.ucr.edu/labs/tutorial/ 3. www.ccessengineeringlibrary.com 4. www.etidweb.tamu.edu 1 library IEEE; 2 use IEEE.std_logic_1164.all; 3 entity latch is 4 port(data,enable:in bit; qout:out bit); 5 end latch; 6 architecture test of latch is 7 begin 8 process(data,enable) 9 begin 10 if(enable='1') then 11 qout <= data; 12 end if; 13 end process; 14 end test; Department of Electronics and Communication 46 EC-606 Lab Manual Page 41 of EXPERIMENT NO.12 VHDL Program for Binary Counter Date of conduction:- Date of submission:- Submitted by other members:1. 2. 3. 4. 5. 6. 7. 8. Group no:- Signature Name of faculty incharge: Name of Technical Assistant: Department of Electronics and Communication 46 EC-606 Lab Manual Page 42 of Objective: - Write a VHDL Program for two input OR Gate Apparatus:21. VHDL Simulation Software (Modelsim/Xilinx) 22. Personal Computer Theory: - Procedure: 111. Open VHDL project by File-> Open->Open Project-> vhdl.mpf 112. Open source code window using View->Source 113. Type Program source code and save it using File->Save as -> <Name>.vhd 114. Compile the program using File->Compile 115. If any error then read the error message and debug the source code. 116. After successful compilation load the design by Design->Load New Design. Department of Electronics and Communication 46 EC-606 Lab Manual Page 43 of 117. Now open signal window by using View->Signals. 118. Apply inputs by using Edit->Clock with these properties time period 100 µs, 200 µs, 400 µs and first edge is Falling Edge. 119. View the output waveform by View->Signals in Region. 120. In Waveform windows press the Run Button multiple times to get the required output wave form. 121. Place the cursor for each entry of truth table and get Results: Print out of output waveform is attached. Conclusion:Output waveform of the design is verified with truth table. Precautions:51. Open vhdl project compulsorily. 52. Type the program in lowercase. 53. Save the file with .vhd extension. 54. The file name does not white space character. 55. Check proper print setting before taking printout. Suggestions:21. Try different type modeling approach for the same design. 22. Observe the delay. Lab Quiz :51. Design the schematic diagram for this design using universal gate. 52. Write the Boolean expression of the design. 53. Apply the Demorgan law on the design. 54. Calculate the total time delay of design. 55. List the all error you have faced to execute this design. Further reading resources: Department of Electronics and Communication 46 EC-606 Lab Manual Page 44 of Book: Lab experiment related theory available in following books: Book Name Author Page No. 31. Circuit Design with VHDL - Volnei A. Pedroni 32. VHDL : Programming By Example Douglas L. Perry - 33. Verilog HDL Primer –synthesis Bhasker - Web resources: 1. http://cis.poly.edu/cs2204/vhdlprg.pdf 2. esd.cs.ucr.edu/labs/tutorial/ 3. www.ccessengineeringlibrary.com 4. www.etidweb.tamu.edu 1 library IEEE; 2 use IEEE.std_logic_1164.all; 3 entity counter is 4 port (count : buffer bit_vector(8 downto 1); 5 clk : in bit; 6 reset : in bit); 7 end; 8 9 architecture only of counter is 10 constant tpd_reset_to_count : time := 10 ns; 11 constant tpd_clk_to_count : time := 5 ns; 12 13 function increment(val : bit_vector) return bit_vector is 15 -- normalize the indexing 16 alias input : bit_vector(val'length downto 1) is val; 17 variable result : bit_vector(input'range) := input; 18 variable carry : bit := '1'; 19 begin 20 for i in input'low to input'high loop 21 result(i) := input(i) xor carry; 22 carry := input(i) and carry; Department of Electronics and Communication 46 EC-606 Lab Manual Page 45 of 23 exit when carry = '0'; 24 end loop; 25 return result; 26 end increment; 27 begin 28 29 ctr: 30 process(clk, reset) 31 begin 32 if (reset = '1') then 33 if reset'event then 34 count <= (others => '0') after tpd_reset_to_count; 35 end if; 36 elsif clk'event and (clk = '1') then 37 count <= increment(count) after tpd_clk_to_count; 38 end if; 39 end process; 40 end only; Department of Electronics and Communication 46 EC-606 Lab Manual Page 46 of