word - University of Arizona

ECE 369A – Fall 2015

MWF 10:00am-10:50am, Room: CHVZ405

Fundamentals of Computer Architecture (4 credits)

Instructor : Ali Akoglu

Office : ECE 356B

Phone

: (520) 626-5149

: akoglu@ece.arizona.edu

Office Hours : Monday 1:00pm-2:00pm, Friday 2:00-4:00pm

Textbook

D. A. Patterson and J.L. Hennessy, Computer Organization and Design: The Hardware/Software

Interface, Fifth Edition, Morgan Kaufmann Publishers.

Overall Educational Goal

Computer architecture is the science and art of selecting and interconnecting hardware components to create a computer that meets functional, performance and cost goals. This course qualitatively and quantitatively examines computer design trade-offs, teaches the fundamentals of computer architecture and organization, including CPU, memory, registers, arithmetic unit, control unit, and input/output components. Topics include reduced instruction set computer architectures (RISC), using the MIPS central processor as an example, interface between assembly and high level programming constructs and hardware, instruction and memory cache systems, performance evaluation, benchmarks, and use of the SPIM/WinDLX/Verilog

Simulators for the MIPS architecture. ECE369 serves students two ways. For those who will continue in computer architecture, it lays foundation of state-of-the-art techniques implemented in current and future high-performance computing platforms. For those students not continuing in computer architecture, it gives an overview of the kind of techniques used in today's microprocessors.

Prerequisite

You must have the following background:

ECE274 (Logic Design): Full Adder Design , Sequential Logic vs. Combinational

Logic, Synchronous vs Asynchronous Circuits, Finite State Machine Design, Latches,

Flip Flops (RS, D, etc) and their characteristics

Programming in C

Programming in Veriolg/VHDL

Course outline

Computer Abstractions and Technology

Arithmetic for Computers

Role of Performance

Instruction Sets and Software Systems

SPIM/WinDLX/Verilog Simulators

MIPS CPU and Control Unit Organization

Pipelining in MIPS CPU

Exploiting Memory Hierarchy

Multicores, Multiprocessors, and Clusters

Philosophy

"I never did anything by accident, nor did any of my inventions come by accident; they came

by work." Thomas Alva Edison.

Read before the class

Participate and ask questions

Manage your time (3 hours outside class for each credit hour)

Start working on assignments early

Outcomes

Each one of you will soon have a degree from Electrical and Computer Engineering

Department. You are getting closer to graduation. Believe me time passes very quickly. In the very near future you will have interviews for internships and then for full time jobs. May be you will apply for graduate schools. In my opinion ECE369 is a class that an Electrical and Computer Engineering student has to take to call him/herself as engineer. This class will be a big step into computer architecture world and we will build the fundamentals throughout this semester. My task is to convey the significance of this field to you and motivate you to explore computer architecture paradigm. By the end of the semester I want each one of you to have the ability to articulate the design issues involved in the computer architecture both in theoretical and application levels. I want you to reach a level of confidence where you can go for an interview and talk comfortably about design tradeoffs involved in computer design, issues in instruction set architecture, pipelining concepts, memory hierarchy and the state of the art multicore/manycore architectures. Finally you should be able to apply the techniques you have learnt and analytical thinking skills you have gained throughout the computer architecture experience to other courses as well.

Accessibility and Accommodations:

It is the University’s goal that learning experiences be as accessible as possible. If you anticipate or experience physical or academic barriers based on disability or pregnancy, please let me know immediately so that we can discuss options. You are also welcome to contact Disability Resources (520-621-3268) to establish reasonable accommodations. Please be aware that the accessible table and chairs in this room should remain available for students who find that standard classroom seating is not usable.

Course organization

Course involves class (3 credits) and laboratory (1 credit) activities.

Class activities will involve 3-4 assignments , several quizzes , 5 examinations and a semester long project

Laboratory (@ECE232)

Lab component of the class involves hands-on and coordinated sequence of weekly activities in which, students incrementally design, develop and test a pipelined processor for a given instruction set architecture using modern synthesis tools and FPGA prototyping boards. In parallel to the hardware design activities, students design, develop and optimize a real world algorithm based on the target instruction set architecture supported by their pipelined processor. Finally laboratory concludes with students

running their optimized algorithm on the FPGA-based pipelined processor they have designed. Competition oriented processor and algorithm design allows students grasp the joint effects of the hardware-, software-, and compiler-design realms on performance.

Students leave the class with a complete understanding of computer organization from theory to practice, and with industry-relevant skills in design, development, debugging and testing.

Laboratory activities will accompany the topics covered in the lectures with hands on programming based assignments. A coordinated sequence of lab assignments will help students design, program, debug, and evaluate specific components of a datapath using the Xilinx ISE and a FPGA board.

Laboratory activities (programming and debugging) and assignments (6 to 8) will help students build the foundation for the semester long datapath-design based project. Final project will require students implement a synthesizable datapath based on a given instruction set architecture and evaluate its performance on a specific FPGA platform.

A lab assignment may have a pre-lab and code-check. You must additionally submit your Verilog files for each lab assignment to the designated D2L dropbox on the day the lab assignment is due. Note, the code submitted on D2L should be the same code demoed in lab.

Students must work in a group of two. Graduate students are required to work on an individual basis. Please note that you may need to work outside of the lab section to complete all of your assignments.

This term we will be using Piazza for class discussion. The system is highly catered to getting you help fast and efficiently from classmates, the TA, and myself. Rather than emailing questions to the teaching staff, I encourage you to post your questions on

Piazza. If you have any problems or feedback for the developers, email team@piazza.com.

Find our class page at: https://piazza.com/arizona/fall2015/ece369a/home

Reading, Quizzes and Participation

Quizzes will be used for checking whether students have completed the reading assignment prior to the class or not. Reading assignments will be posted on the D2L.

Piazza participation (responding to questions of other students, posting your solutions to exercise problems prepared by the instructor) will be monitored closely.

General policies

NO LATE ASSIGNMENTS WILL BE ACCEPTED, except under extreme nonacademic circumstances discussed with the instructor at least one week before the assignment is due.

Make-ups for assignments and exams may be arranged if a student's absence is caused by documented illness or personal emergency. A written explanation (including supporting documentation) must be submitted to your instructor; if the explanation is acceptable, an alternative to the graded activity will be arranged. When possible, makeup arrangements must be completed prior to the scheduled activity.

Any extenuating circumstances that have an impact on your participation in the course should be discussed with your instructor as soon as those circumstances are known.

Inquiries about graded material have to be turned in within 3 days of receiving a grade.

Approximate weight of each assignment will be specified when the assignment is handed out. Assignments will be due in class on the due date.

The instructor reserves the right to modify course policies, course calendar, assignment values and due dates, as circumstances require.

Students are strongly encouraged to attend the class. Lecture notes are intended to serve as a supplement and not as a substitute for attending class.

You are encouraged to discuss the assignment specifications with your instructor, your teaching assistant, and your fellow students. However, anything you submit for grading must be unique and should NOT be a duplicate of another source. The Department of

Electrical and Computer Engineering expects all students to adhere to UofA’s policies and procedures on Code of Academic Integrity. http://web.arizona.edu/~studpubs/policies/cacaint.htm

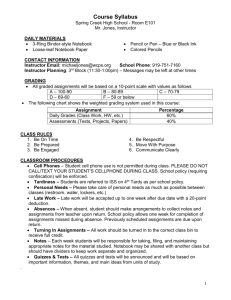

Distribution of Components Grades Scale

Component

Class Participation

Percentage

10

Percentage

90-100%

Grade

A

Laboratory

Exam-I

10

8

80-89%

70-79%

B

C

Exam-II

Exam-III

Exam-IV

Exam-V

Project

10

10

12

15

25

60-69%

Below 60%

D

E

Class Participation: Piazza participation (3%), Quizzes (7%) (in-class)