Case Study HDL Description of a Basic Computer

Case Study HDL Description of a Basic Computer

In this Case study we write a HDL description for a basic computer. In our computer, the Central Processing Unit consists of Arithmetic Logic Unit (ALU), Registers, and a

Control unit. The ALU performs all arithmetic and logic operations, see Table 7.3. The registers inside the CPU store data and communicate with the ALU and the memory.

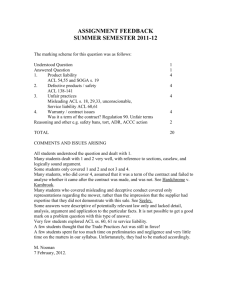

The memory here is 16x8 bits. Figure 7.9 shows the different registers in our computer. The registers in our computer are:

*** Insert Figure 7.9 here***

Figure 7.9 Registers in the Basic Computer.

Program Counter (PC): it stores the address of the instruction to be executed. It is 4 bits wide.

Address Register (AR): it is connected to the address bus of the memory. It supplies addresses to the memory. It is 4 bits wide. In our computer AR is the only register that can provide addresses to the memory.

Data Register (DR): it is connected to the data bus of the memory. It receives and stores data from the memory. It is 8 bits wide. It is connected to the data bus of the memory.

In our computer DR is the only register that can communicate with memory data bus.

Accumulator (AC): it is a general register that stores data. This register has two equal halves low (ACL) and high (ACH) each is 8 bits. The AC is 16 bits wide.

Instruction Register (IR): it stores 3 bits operation code (op code).

The control unit supervises on all other units of the computer. It provides timing and control signals for all units. In our basic computer, all programs are stored in the

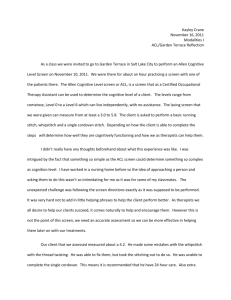

memory. A program is a group of instructions and the data it is processing. The instruction is 8 bits wide. See Figure 7.10. The instruction has two fields: operation code (op code) and address. The op code field determines the type of operation the computer should perform. The address

*** Insert Figure 7.10 here***

Figure 7.10 Instruction Format determines the location of the operand in the memory The operand is the data on which the operation is performed. In our computer we have 8 different instructions, so we need

3 bits to decode the operations of the instructions. Table 7.3 shows a possible decoding of these operations.

Table 7.3 operation codes for operations.

OP Code Operation in Mnemonic

HALT

ADD

MULT

DIVID

XOR

PRITY

NAND

CLA

000

001

010

011

100

101

110

111

The memory we use here is 16x8 bits. To access this memory we need 4-bit address; we use 5 bits here for the address with one extra bit for any future expansion of the memory. So our instruction is 8-bit wide with 3 bits for the op code and 5 bits for the address. The following is a brief description of the instructions shown in Table 7.3.

HALT: it halts the computer by deactivating the master clock; all registers retain their current data

ADD: this is addition operation. The contents of the lower half of the

Accumulator Register (ACL) are added to the contents of a memory location; the result is stored in ACL.

MULT: multiply the contents of the lower half of the AC with an operand in the memory and store the result in AC (both halves).

DIVID: this is integer division. Divide the contents of the lower half of the AC by the contents of memory location; the result is stored in ACL.

XOR: performs the logical operation EXCLUSIVE OR between the contents of

ACL and a memory location; the result is stored in ACL.

PRITY: this is an even parity generator. The parity bit for the least significant 7 bits of ACL is calculated and then the parity bit inserted in the most significant bit of ACL

NAND: performs the logical operation NAND between the contents of ACL and a memory location; the result is stored in ACL.

CLA; this is to clear the contents of the ACL.

The memory location in all of the above instruction is determined by the address provided by the instruction and stored in the Register Address (AR). More details about basic computers can be found in [Hayes98], [Mano 00], and [Nelson95]. Some examples to show the detailed explanation of some instructions are shown below.

ADD 7: this instruction adds the contents of the lower half of the accumulator to the contents of memory location 7; the result is stored in ACL.

DIVID 5: this instruction divides the contents of the lower half of the accumulator by the contents of memory location 5. The result is stored in ACL.

Our basic computer executes the instructions in two cycles, fetch and execute. See

Figure 7.11. The control unit supplies all required signals necessary for operation of the two cycles. In the fetch cycle, the instruction is moved from the memory to the DR.

The lower 4 bits (0 to 3) of DR are stored in AR; bits 5 to 7 of the DR are stored in IR.

The PC is incremented to point at the next instruction to be fetched. The 3 bits of the IR is decoded into 8 outputs by a 3x8 decoder. The output of the decoder determines the type of operation requested by the instruction. For example, if the least significant output of the decoder is active, then the operation requested belongs to the op code 000 which is HALT.

*** Insert Figure 7.11 here***

Figure 7.11 Fetch and execute cycles of the basic computer

In the execute cycle, the computer executes the instruction that has been fetched. For example, if the instruction is ADD, then the execute cycle issues a memory read DR ←

M [AR] to move the operand from the memory to the DR. M stands for memory. This movement is necessary since the ALU can operate only on DR and AC but not on data stored in memory. After moving the operand to DR, an add operation in the ALU is selected. Different operations of the ALU are selected by control signals supplied by the control unit. The ALU executes the microoperation AC ← AC + DR. For the instruction PRITY, the execute cycle calculates the parity bit (bit 7 of the accumulator) as:

Parity (ACL(7)) = ACL(6) XOR ACL(5) XOR ACL(4) XOR ACL(3) XOR ACL(2)

XOR

ACL(1) XOR ACL(0)

As we mentioned before, the control unit oversees the fetch and execute cycle. We design the control unit as a finite sequential state machine. Figure 7.12 shows state diagram of the machine. The Figure shows only transitions between states; it does not show outputs. The states state0, state1, and state2 are performing the three steps of the fetch cycle, while state3 performs the

*** Insert Figure 7.12 here***

Figure 7.12 State diagram of the machine. execute cycle, see Figure 7.11. To illustrate the operation of the basic computer, we store a program inside the memory. The program is shown in Table 7.4. Table 7.4 shows the instructions of the program with the op code written in mnemonic and the instructions written in hexadecimal. For example the instruction:

1 ADD 9 29 is stored in memory location 1. The op code is ADD, the address is 9. The instruction adds the contents of the accumulator (AC) to the contents of memory location 9; the result of addition is stored in the accumulator. Accumulator in our computer is always the default register. The binary value of the op code ADD is 001, see Table 7.3. The instruction is 8-bit wide , so the binary representation of the instruction is: 00101001 which is 29 in hexadecimal.

Table 7.4 Contents of Memory of the Basic Computer

Location in Instruction in Mnemonic or

Hex

0 CLA

Data in Hex

Memory Contents (8 bits) in

Hex

1 ADD 9

E0

29

6

7

8

9

A

2

3

4

5

XOR

MULT

DIVID

XOR

C

5

A

B

C

D

NAND E

PRITY

HALT

B

C

D

4

9

3

04

09

03

E

F

9

7

09

07

Listing 7.10 shows the HDL code for the program shown in Table 7.4.

CE

A0

00

0C

05

8A

4B

6C

8D

Referring to Listing 7.10a. The package Comp_Pkg declares one dimensional array with 16 elements; each element is 8 bits. This array represents the memory of the computer. In the entity computer_basic, the signal clk_master simulates the master clock of the computer. The signal ON_OFF simulates an ON/OFF switch. The data flow statement : clk <= clk_master and ON_OFF; simulates an AND gate. The signal clk simulates the clock signal of the CPU; if the switch is off, the clock signal to the CPU is inactive and accordingly, the CPU is inactive. The statement

z(0) <= ACL(6) xor ACL (5) xor ACL (4)xor

ACL (3)xor ACL (2)xor ACL (1)xor ACL (0); generates an even parity bit. We selected to write this statement as data flow (outside always) because it is easier to write the Boolean as data flow description than the behavioral of this parity generator circuit. The statements:

ARI := TO_INTEGER(AR);

DR := Memory (ARI); converts AR from unsigned to integer by the built-in function TO_INTEGER. This function is a member of the package ieee.numeric_std. We convert to integer because the index of the array ARI has to be of type integer in VHDL.

Referring to the Verilog description in Listing 7.10b. The memory is simulated by the statement: reg [7:0] Memory [0:15]; which describes an array of 15 elements (words); each element is 8 bits. In contrast to

VHDL, Verilog can accept an index of array declared as bit_vector. For example we can write:

DR = Memory [AR]; without specifying AR to be of type integer.

Listing 7.10 HDL Code for the Program of Table 7.4. a) VHDL. b) Verilog a) VHDL Description

--Write the code for Package Comp_Pkg library IEEE; use IEEE.STD_LOGIC_1164.all; use ieee.numeric_std.all; package Comp_Pkg is

constant N: integer := 15;

--N+1 is the number of elements in the array. constant M: integer := 7;

--M+1 is the number of bits of each element

--of the array.lements in the array. subtype wordN is unsigned (M downto 0); type strng is array (N downto 0) of wordN; type states is (state0, state1, state2, state3); end Comp_Pkg;

--Now write the code for the control unit library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; use ieee.numeric_std.all; use work.Comp_Pkg. all; entity computer_basic is

generic (N:integer :=15; M: integer := 7);

--N+1 is the number of words in the memory; M+1 is the

--number of bits of each word.

Port ( Memory : inout strng; PC: buffer unsigned (3 downto 0);

clk_master: std_logic;

ACH : buffer unsigned (7 downto 0);

ACL : buffer unsigned (7 downto 0);

Reset: buffer std_logic; ON_OFF : in std_logic );