Study Guide – Exam 1 – CSC 317

advertisement

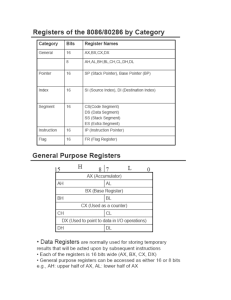

Study Guide – Exam 1 – CSC 317 What to expect: About 3-5 multiple-choice questions, 1-3 True/False questions and 3-5 longer problems or essay questions. Chapters 1, 2 and external sources Motivation for learning COA Optimize code Vocabulary/acronyms – Comparing systems, benchmarking Interfacing systems (hardware compatibility) Writing device drivers Writing compilers How floating point arithmetic works What is a computer? A system that accepts data, processes the data according to some instruction, & produces some results. abstraction I P O Basic elements of a computer 1. Processor 2. System interconnection 3. Main memory 4. Input/output Architecture vs. Organization Architecture Those features “visible” to a programmer Instruction set # bits used for data representation Addressing modes E.g. ADD A, B, C - 3-operand instruction ADD A, B ADD A - accumulator Organization How features are implemented. E.g. o How multiply is implemented o Control signals o Interfaces o Memory technology Evolution of computers: o ENIAC John Mauchly, John Eckert, University of Pennsylvania, first general purpose electronic digital computer, purpose: develop range and trajectory tables for the Army’s Ballistics Research Laboratory for WWII year built: started in 1943, finished in 1946 o Von Neumann machine Importance: stored program concept Stored program concept: Memory holds instructions & data No more rewiring Program can be altered by changing the memory content IAS architecture Princeton Institute of Advanced studies Completed 1952 Same general structure and function as today’s computers o A main memory, which stores both data & instructions o An arithmetic and logic unit (ALU) capable of operating on binary data o A control unit, which interprets the instructions in memory and causes them to be executed o Input and output (I/O) equipment operated by the control unit Memory ALU Program Control Unit I/O Data Processing Control Unit AC MQ ALU I/O MBR memory IBR IR MAR Control unit PC control signals Program Control Unit o IBM 7094 Data channel Independent I/O module with its own processor & instruction set Multiplexer Precursor of the bus architecture It schedules access to main memory from CPU & data channels o Moore’s Law States that chip density doubles every 12 months Gordon Moore o Important technology in each computer generation 0. devices before computers mechanical calculators 1. vacuum tubes 2. transistors 3. IC (Integrated Circuits) 4. microprocessor processor in a chip 5. RISC (reduced Instruction Set Computer) 6. Large capacity, low cost disc system & memory Faster microprocessors Performance considerations: o Mismatch interface between processor and main memory o Solutions to solving the mismatch Make DRAM “wider” rather than “deeper” Increase the # of bits retrieved at one time Change DRAM interface to make it more efficient By including cache Reduce frequency of memory access Using complex cache structure Increase interconnection bandwidth Use higher speed buses Use hierarchal buses Performance measures: o Benchmark programs Measure of execution performance based on average figures o Equation about execution time Suppose you have a set of benchmark programs: Q It takes T seconds to execute them N: is number of instruction executed Parameter 1: average # of instructions per second: I Parameter 2: average # of cycles per instruction: C f: clock frequency in MHz f 106 C I N N C architecture T 6 6 hardware f 10 f 10 C Chapter 3 CPU registers Instruction cycles o Fetch PC holds address of the next instruction to be fetched Processor fetches next instruction pointed to by the PC Increments PC (unless told otherwise) Instruction is loaded into IR Processor decodes instruction in IR o Execute Processor executes one of the following actions CPU – MM data transfer CPU – I/O data transfer Data Processing Control Combination of above o Interrupt start Fetch Interrupt Execute What is an interrupt, and its advantage? Mechanism by which other modules (e.g. I/O) may interrupt the normal processing of the CPU. Classes of interrupts o Program: as a result of program execution Example: division by zero o Timer: generated by internal processor timer used in preemptive, multitasking OS o I/O: on I/O controller signal the CPU at the completion of some I/O task, (or some error condition) o Hardware failure: e.g. memory parity error Handling multiple interrupts 2 ways of handling o Define priority Allow a higher priority interrupt to interrupt a lower priority interrupt Processor returns to previous interrupt after the hi priority has been processed o Disable interrupts Physical implementation of interrupts 1 CPU INTA M1 Daisy chain 1 M2 0 Mn INTN INT2 CPU interrupt arbiter INT1 M1 Mn M2 INTA1 INTA2 INTAn Types of exchanges between different components of a computer Buses o Definition A bus is a communication pathway connecting 2 or more devices. o Fundamental groups Data bus Address bus Control bus o Single bus problem Propagation delay more time to coordinate the bus bandwidth shared o Hierarchal buses Bus types o Traditional bus architecture o High-performance architecture Bus arbitration Bus timing PCI bus: (Peripheral Component Interconnect) o Principal features High bandwidth Processor-independent Released by Intel in 1990 Current standard 64 data lines 528 Mbytes/sec Address and data multiplexed lines 49 mandatory lines o Bus transfer operation Diagram pg 86 Chapter 9 Integer representation o Sign magnitude Left-most bit indicates if # positive: 0 negative: 1 o two’s compliment Negative for a number A takes the complement of 1 add 1 Range: -2n-1 to (2n-1-1) o Addition o Subtraction B register A register Complimenter Adder Result o Multiplication (Booth’s algorithm) o Division Floating point representation o Number representation and normalization o IEEE 754 standard o Addition o Subtraction o Multiplication o Division Precision considerations: o Guard bits and rounding 1. 4 types 2. ?? 3. ?? 4. ?? Chapter 10 Elements of an instruction 1. opcode 2. source operands 3. result operands 4. next instruction Number of addresses Types of operands Types of operations o Procedure call instructions o Stack frame o Frame pointer