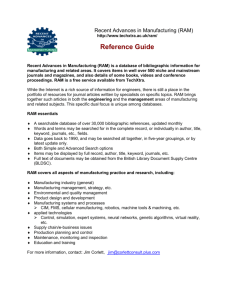

ACOE201_Lab2

advertisement

Computer Engineering Department Computer Architecture I Lab (ACOE201) Experiment #2 RAM Access Student’s Name: Semester: Date: Assessment: Assessment Point Weight Methodology Presentation and discussion of results Participation Assessment Points’ Grade Comments: 1 Grade Experiment #2: RAM Access Objective: To examine the way RAM devices are accessed for both Write and Read operations. Conventions: The symbol indicates an operation that must be done in hardware e.g. pressing a button or switch, making a connection on the board, a jumper etc. The symbol indicates an operation that must be done in software e.g. a command that must be entered, a window that must be opened etc. Introduction: RAM stands for Random Access Memory also known as a Read/Write memory. RAM devices are used to store temporarily information. A RAM can be viewed as a huge register array incorporated in a single package. They have a set of data lines over which data can be stored and retrieved, a set of address lines, used to select a particular location for either data storage (WRITE operation) or data retrieval (READ operation). A set of control lines are used to select either a READ or WRITE operation. A memory write operation is done in three steps: 1. Load the data lines with the data to be stored. 2. Load on the address line the binary code representing the address of the memory location to be accessed. 3. Activate the Write Enable signals. Some RAMs use the same signal for both read and write operations. One state of this signal is used for a write operation and the other for a read operation. In this lab two different signals are used. Procedure: 2 Step 1. Launch the Xilinx ISE environment and create a new project (Lab2). Select the Spartan-6 Device family from the drop-down menu Select the XC6LX16 device from the drop-down menu Select the CSG324 package from the drop-down menu Select schematic as the design entry method. Select “ISim” in the simulator selection. Create a new schematic. Enter the schematic of Fig. 1 using the Xilinx hardware environment tools. Download the testbench file "Lab2_tb.v found in http://staff.fit.ac.cy/com.tk/ACOE201/Lab2_tb.v Select "Project => Add Source". Select "Lab2_tb.v". g) Go to the “simulation” tab. Select the "Lab2_tb" source file. Expand Isim simulator. Double click on simulate behavioral model Insert simulation screenshot here…. Step3. Download the UCF file specifying the input and output pin connections from: http://staff.fit.ac.cy/com.tk/ACOE201/Lab2.ucf Add it to the project as a source file. Open it with a text editor and add the following line: NET "BTNW" CLOCK_DEDICATED_ROUTE = FALSE ; Step 4. Synthesize and Implement the circuit of Figure 2. Generate the programming file. Step 5. Connect the FPGA to your PC through the USB cable provided and turn on the power switch. Configure the Spartan-3E board by clicking on Start => Programs => Digilent => Adept => Adept. Adept should identify the Nexys3 board. Browse to the project folder and select the .bit file. Click on "Program". Wait until the message that programming is successful. Step 6. Set the BTNE (Write Enable) to 1 and BTNN (Read) to 0. 3 Step 7. Write the binary number 0000 into memory location 00H, i.e. Data = 0000, Address = 0000. Step 8. Increment the address by one and the data by one and repeat steps 3 and 4 until the 16 locations are filled. Fill in the memory Table 1 with your entries. Figure 1. 16 x 4 RAM Schematic Address (HEX) Contents 4 Table 1. Step9: Read the data stored in the 16 x 4 RAM and compare it with the data stored in steps 3 and 4. Fill in the RAM memory Table 2. Write down the steps you followed to do this. Steps: Address (HEX) Contents 5 Table 2. Questions: What would have happened if BTNE7 (Write Enable) was 0 in step 2 during the writing process? What would have happened if BTNN (Read) was 1 in step 2 during the writing process? What would have happened if BTNE was 1 during the read process? How many LUTs/FFs were used for this design? 6