How to include a FPGA program

advertisement

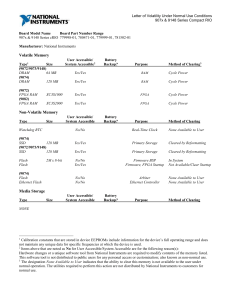

Compiling and Loading of the Logic Units and IDBs FPGAs Feb. 11, 2008 (contact boek@physik.uni-wuppertal.de, voss@physik.uni-wuppertal.de, susanne.kersten@cern.ch) This manual consists of 4 parts: 1. create a *.vhd file 2. compile the FPGA programming files 3. extract the Flash Pro Files 4. load the program into the FPGA with Flash Pro Please notice: The Libero software is installed at CERN on the DCS Laptop: pcatlpixlt02 in Wuppertal on Jennys desktop PC (wpdo166) and on the PC in the DCS lab (wpdo38) 1. How to create a *.vhd file A *.vhd file consists of 3 parts: header and end of the source code, logic and the program address. They have to be combined to get the necessary *.vhd file. This *.vhd file is the source code of the FPGA program and has to be compiled with the Libero software before the resulting files can be loaded on the FPGA. 1. Header and end of the source code: Header and end of the source code can be found at the DCS quarks account in the folder “Interlock programs\SRC\*.vhd” Choose “emptyIDBvhdlFile071016.vhd” (for an IDB FPGA program), “emptyLUvhdlFile071016.vhd” (for a Logic Unit FPGA program for the PIT) or “emptyLUvhdlFile071016_SR1.vhd“ (for a Logic Unit FPGA program in SR1) and save it as <ProgramName>.vhd. It is very important to change all 4 <ProgramName> entries to the real program name in the <ProgramName>.vhd file, like it is shown in figure 1. In this figure, 4 arrows in the header part show where the <ProgramName> has to be changed. The 4 lines are: (change only the <ProgramName>!!!) 1. -- <ProgramName>.vhd 2. ENTITY <ProgramName> is 3. end <ProgramName> ; 4. architecture behaviour of <ProgramName> is <Program Name> is for example IDB_SC02_070903 2. Logic: The file with the assignment of incoming and outgoing interlock signals (the 1 interlock logic) has to be copied into <ProgramName>.vhd under the header code. The place where the logic has to be inserted is marked (see figure 1). If there is more than one file, copy every file after each other at the marked position. 3. Program address: Every interlock logic part (one file of assignment of incoming and outgoing interlocks) has to be addressed with the line: when “1000” => ”1000” is the number with which a logic part can be adressed. LU adress 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 switch adress IDB adress 00000 0 00001 1 00010 2 00011 3 00100 4 00101 5 00110 6 00111 7 01000 8 01001 9 01010 10 01011 11 01100 12 01101 13 01110 14 01111 15 10000 10001 10010 10011 10100 10101 10110 10111 11000 11001 11010 11011 11100 switch adress 0000 1000 0100 1100 0010 1010 0110 1110 0001 1001 0101 1101 0011 1011 0111 1111 2 Figure 1 shows an example of a FPGA program to understand the steps how to create a complete *.vhd file. H e a d e r insert the logic part here green box: interlock logic part which has to be adressed The VHDL syntax to adress the logic part Last part of the program Figure 1: Example of a FPGA program with the steps how to create a complete *.vhd file 3 2. Compile the FPGA programming files The *.vhd file is the source code of the FPGA program but this code can not directly be loaded on the FPGA. It has to be compiled and the pin assignment of the FPGA must be added. At the end one gets two resulting files which finally can be loaded on the FPGA. The following steps describe how to do this. 1. Start Libero. 2. The user interface shown in figure 2 opens: Figure 2: Libero User Interface This is the InterlockLogicUnit project. If it has to change into the InterlockDistributionBox project, click on FileOpen Project and in the pop up window choose the folder InterlockDistributionBox and in this folder the *.prj file. 3. To import the *.vhd file (the *.vhd file created in the first part) click on FileImport Files and choose the *.vhd file which is needed. 4. Set the included files as root by right click on the program name in the left window of the user interface, this is shown in figure 3. 4 set file as root click to view the design flow click to view the code Figure 3: Set file as root and get design flow or code The chosen file will be shown in fat letters. In figure 3 the file “SR1_LU_FPGA[SR1_LU_FPGA.vhd]” is set as root. 5. Synthesis Synplify checks the *.vhd file for errors and converts the *.vhd file. Start Synplify by clicking on the following button: 6. The Synplify panel opens. Now click on the “RUN” button to compile the FPGA program. Where the button can be found is shown in figure 4: 5 click on the disk to save Figure 4: The Synplify user interface 7. If the red ”Ready…” changes into a red “Done!” the Synplify panel must be saved and can be closed. 8. With the “Place&Route Designer” the FPGA pin assignment can be imported, in addition the netlist is build.The “Place&Route Designer” has to be opened by clicking on the Icon as shown below. Wait a moment! 9. At the pop up window “Device Selection Wizard” all settings must be kept. Now the FPGA pin assignment has to be imported into the program: 10. Click in the “Place&Route Designer” panel on FileImport Source Files. There should be open a panel like in figure 5. 6 Figure 5: Import source files pop up window Click in the left part of the first free line and click on the “Add…” button. Choose in the pop up window “Add Source Files” as shown in figure 6 the filetype *.gcf. The necessary *.gcf files are located at the DCS quarks account in the folder “Interlock programs/PinAssignment”. Please note that the PIN assignments for the units of SR1 can be different. 7 Click on the button “Import”. It is important to choose filetype *.gcf Figure 6: Add source files 11 There should be open a panel like figure 7: Figure 7: Warning pop up window 8 Answer with “Ja” (Yes). Sometimes the pop up window “Import file” as shown in figure 8 shows up. If it opens click “OK”. Figure 8: Import File pop up window At the “EDIF Import Options” panel “GENERIC” must be choose and after that the “OK” button should be pressed. This panel is shown in figure 9. Figure 9: EDIF Import Options pop up window Now the FPGA pin assignment is imported 9 11. Click on “Compile” icon in the Designer panel as shown in figure 10: Figure 10: Click on Compile Icon to compile your program 12. After the “Compile” button lights up green, first it must be clicked on “Layout”. A pop up window opens- click OK. After the Layout Icon (also shown in figure 10) lights up green, click on the Programming File Icon (shown in figure 10 too). In the pop up window (figure 11) “Generate Programming File” choose the file type “STAPL” and press “OK”. Figure 11: Choose file STAPL If the “Programming File” button is green too, then save and close the Designer panel. This creates the *.stp file which is relevant to program the FPGA. 10 13. To get one of the two necessary files to program the FPGA, the Flash Pro program must be started and saved. Click on the “Programming” Flash Pro Icon. Figure 12: Flash Pro Icon The Flash Pro panel (shown in figure 12) should be open: Figure 13: Flash Pro user interface 14. Click on the disk icon in this panel to save. With this the *.pro file will be constructed. With this file and the *.stp file the FPGA program can be loaded into the FPGA. 15. If one wants to load the program into the FPGA, click on the button “PROGRAM” after connecting the FPGA to the PC. 11 3. Extracting the Flash Pro Files 1. To program the FPGA only by using Flash Pro, two files of the Libero compiled program are used. The *.stp file and the *.pro file. 2. The *.stp file is located in the following folder: C:\Actelprj\project name\designer\impl1\<program name>.stp 3. In this path in a further folder the *.pro file can be found: C:\Actelprj\project name\designer\impl1\<program name>\<program name>_fp.pro If this file is not located in this folder, please open your Libero project and set your program as root (described in the second part of this manual in step 4. Then open Flash Pro as it is described in the second part of this manual in step 14. Click on the disk to save and close Flash Pro. The *.pro file should now be created in the file path above. 4. Both files 4. Load the program into the FPGA with Flash Pro In Fig. 14 it is shown how the FlashPro programmer must be connected to the FPGA of the Interlock Distribution Box. The connection between Programmer and PC is established via USB. Fig.14: The FlashPro Programmer and the adapter board 12 To program the FPGA of the Logic Unit, the block on the very right of the Logic Unit must be opened and the FPGA board must be taken out. After programming install the FGA board in the same as it has come out (please note, connectors on both sides are identical, the naming of the board must be above and readable). The FPGA must not be powered while programming! You need two file for downloading: *.pro and *.stp. Put them on the laptop and check that you have the latest version of the files. (As the stp file describes the hardware, this file must not necessarily be updated during the last compilation.) Now: Start FlashPro via the icon located on the desktop, Fig. 13 shows its control panel. Open Project browse to your .pro file and open it configure stapl file browse to the .stp file and open it program In addition there should be the programmer on port USB.. visible. If not check the connections to the FPGA and the power supply. In the “Programmer Status” field there should be a blue bar to show the programmer status. The FPGA programming is completed when the “Programmer Status” field reports “run passed”. Typically it takes 2 -3 minutes. Then the program can be closed and the FPGA can be disconnected from the PC. If the “Scan chain failed”, check the connections of the FPGA and the power supply. 13