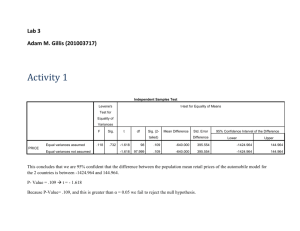

Comm 471: Digital Circuit Design Lab 7

advertisement

Comm 471: Digital Circuit Design Lab 7 some slides modified from: S. Dandamudi, “Fundamentals of Computer Organization and Design” 1 Outline • Introduction to FPGAs • FPGA Design Flow • Exercise 2 Introduction to FPGAs 3 Major FPGA Vendors: Xilinx Spartan-6 Artix-7 Kintex-7 Kintex Virtex UltraScale UltraScale Logic Cells 147,443 215,360 760 ,477 1,954,560 1,160,880 4,432,680 4.8Mb 13Mb 34Mb 68Mb 76Mb 132.9Mb BlockRAM 576 500 500 1,200 832 1,456 I/O Pins I/O Voltage 1.2V – 3.3V 1.2V – 3.3V 1.2V – 3.3V 1.2V – 3.3V 1.0 – 3.3V 1.0 – 3.3V http://www.xilinx.com/products/silicon-devices/fpga.html Virtex-7 4 Major FPGA Vendors: Altera • High-End FPGAs • Mid-Range FPGAs • Low Cost FPGAs http://www.altera.com/devices/fpga/fpga-index.html 5 General structure of an FPGA Programmable interconnect Programmable logic blocks The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www.mentor.com) 6 Configurable Logic Blocks (CLB) Configurable logic block (CLB) CLB CLB CLB CLB Slice Slice Logic cell Logic cell Logic cell Logic cell Slice Slice Logic cell Logic cell Logic cell Logic cell The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www.mentor.com) 7 Simplified view of a Logic Cell 16-bit SR 16x1 RAM a b c d e 4-input LUT y mux flip-flop q clock clock enable set/reset The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www.mentor.com) 8 LUT (Look-Up Table) Functionality x1 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 x2 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 x3 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 x4 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 x1 x2 x3 x4 y 1 1 1 1 1 1 1 1 1 1 1 1 0 0 0 0 LUT y x1 x2 x3 x4 x1 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 x2 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 x3 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 x4 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 y 0 1 0 0 0 1 0 1 0 1 0 0 1 1 0 0 • Look-Up tables are primary elements for logic implementation • Each LUT can implement any function of 4 inputs x1 x2 y y 9 Other FPGA Components Block RAMs Block RAMs Configurable Logic Blocks I/O Blocks Block RAMs • Multipliers • RAM • Clocking & PLLs 10 FPGA Design Flow 11 FPGA Design Process 12 Logic Synthesis VHDL description Circuit netlist architecture MLU_DATAFLOW of MLU is signal A1:STD_LOGIC; signal B1:STD_LOGIC; signal Y1:STD_LOGIC; signal MUX_0, MUX_1, MUX_2, MUX_3: STD_LOGIC; begin A1<=A when (NEG_A='0') else not A; B1<=B when (NEG_B='0') else not B; Y<=Y1 when (NEG_Y='0') else not Y1; MUX_0<=A1 and B1; MUX_1<=A1 or B1; MUX_2<=A1 xor B1; MUX_3<=A1 xnor B1; with (L1 & L0) select Y1<=MUX_0 when "00", MUX_1 when "01", MUX_2 when "10", MUX_3 when others; end MLU_DATAFLOW; 13 Mapping LUT0 LUT4 LUT1 LUT5 FF1 LUT2 FF2 LUT3 14 Placing FPGA CLB SLICES 15 Routing FPGA Programmable Connections 16 Configuration & Programming • Once a design is implemented, you must create a file that the FPGA can understand. This file is called a bit stream. • The bit stream file can be downloaded directly to the FPGA, or can be converted into a PROM file which stores the programming information 17 Exercise 18 Counter • In this lab, we will make a counter by 7 & test it using an FPGA. • The used FPGA is Altera UP2 Education Kit and we will use Quartus software to program the FPGA. 19 Altera UP2 Education Kit 20 Altera UP2 Education Kit Description 21 Quartus II Steps 22 Creating a Project (1) 23 Creating a Project (2) 24 Creating a Project (3) 25 Creating a new file 26 VHDL Code LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_arith.all; ENTITY counter IS port (clk, rst: in std_logic; count: out std_logic_vector(6 downto 0)); END counter; ARCHITECTURE rtl OF counter IS signal count_sig: integer range 0 to 7; BEGIN process(clk, rst) begin if (rst='1') then count_sig <= 0; elsif (rising_edge(clk)) then count_sig <= count_sig + 1; end if; if (count_sig=0) then count <= "1000000"; elsif (count_sig=1) then count <= "1111001"; elsif (count_sig=2) then count <= "0100100"; elsif (count_sig=3) then count <= "0110000"; elsif (count_sig=4) then count <= "0011001"; elsif (count_sig=5) then count <= "0010010"; elsif (count_sig=6) then count <= "0000011"; elsif (count_sig=7) then count <= "1111000"; end if; end process; END rtl; 27 Compiling the project 28 Compilation Results 29 Viewing Synthesized Netlist (1) 30 Viewing Synthesized Netlist (2) 31 UP2 FPGA Datasheet 32 Pin Assignment 33 Re-compiling the project 34 Programming the FPGA (1) 35 Programming the FPGA (2) 36 TO BE CONTINUED Thank you 37