CS345: Computer Organization

advertisement

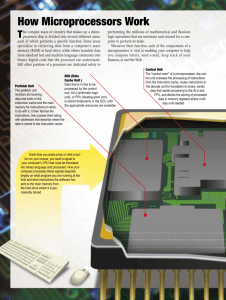

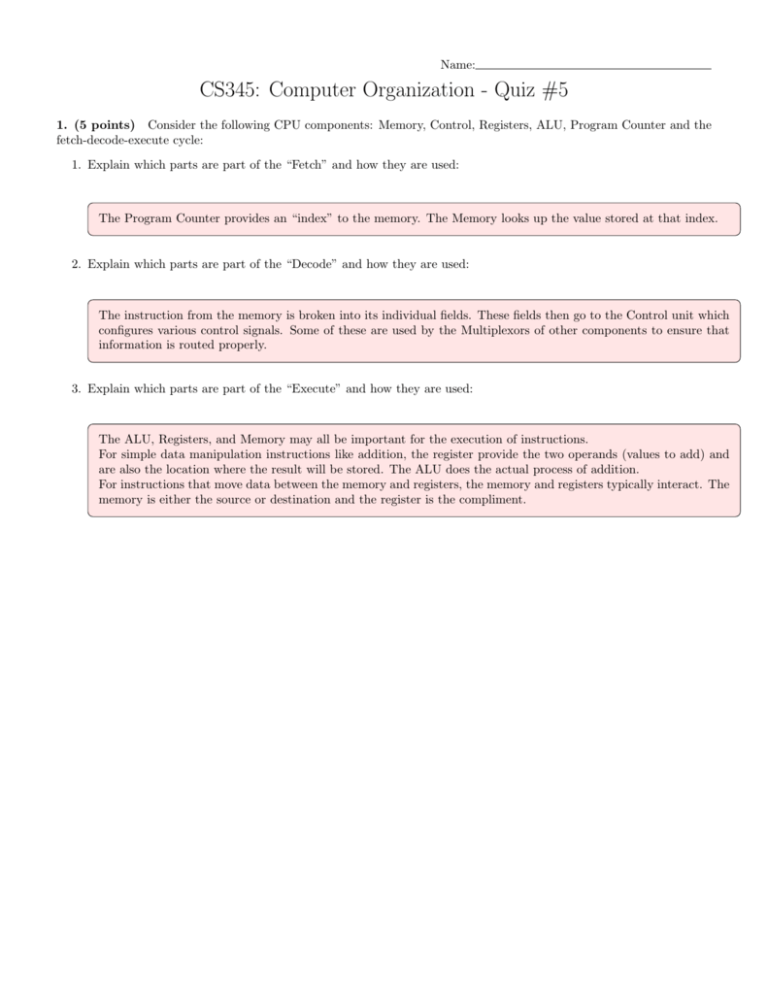

Name: CS345: Computer Organization - Quiz #5 1. (5 points) Consider the following CPU components: Memory, Control, Registers, ALU, Program Counter and the fetch-decode-execute cycle: 1. Explain which parts are part of the “Fetch” and how they are used: The Program Counter provides an “index” to the memory. The Memory looks up the value stored at that index. 2. Explain which parts are part of the “Decode” and how they are used: The instruction from the memory is broken into its individual fields. These fields then go to the Control unit which configures various control signals. Some of these are used by the Multiplexors of other components to ensure that information is routed properly. 3. Explain which parts are part of the “Execute” and how they are used: The ALU, Registers, and Memory may all be important for the execution of instructions. For simple data manipulation instructions like addition, the register provide the two operands (values to add) and are also the location where the result will be stored. The ALU does the actual process of addition. For instructions that move data between the memory and registers, the memory and registers typically interact. The memory is either the source or destination and the register is the compliment. 2. (5 points) Performance Review 1. In your opinion which is faster, a 1MHz processor or a 3MHz processor? Explain your opinion: If they have the same design (use the same ISA and are identical in nearly every respect), then the 3MHz would be 3x faster for CPU only operations. (Things that depend on external parts, like the memory, may have to perform at the slower rate of the external part, so it may not matter what rate the CPU can run at) 2. A single cycle CPU is running at 1MHz and needs to complete a program that will run 1000000 instructions. How long will the program take to execute? . We could juggle this around a little to say that for each 1 second there are 1,000,000 cycles. 1M Hz = 1,000,000cycles second 1second As a fraction this is 1,000,000cycles . Multiplying out all the parts: 1, 000, 000instructions · 1cycle instruction · 1second 1,000,000instructions = 1s 3. A Multi-cycle CPU is running at 3MHz and needs to complete a program that has 500,000 instructions that require 4 cycles, 250,000 instructions require 5 cycles, and 250,000 instructions require 3 cycles. How long will the program take to execute? 3M Hz = 3,000,000cycles . We could juggle this around a little to say that for each 1 second there are 3,000,000 cycles. second 1second As a fraction this is 3,000,000cycles . 4cycles To find the total number of cycles needed: 500, 000instructions · instruction + 250, 000instructions · 3cycles 250, 000instructions · instruction = 4, 000, 000cycles. 1second To find the total time: 4, 000, 000cycles · 3,000,000instructions = 1.3333s 5cycles instruction 3. (3 points) For the one-cycle CPU (handout from class and/or the JLS file posted in Homework #A), explain the execution of a lw instruction. Carefully explain all the relevant control signals and the details of how the memory address of the data is computed. The Control will identify the lw opcode and use it to activate the following outputs: • ALUSrc=1 • RegWrite=1 • MemRead=1 • ALUOp=0 (This is important because the ALU is used for this instruction) The ALU will be adding the values on its A and B inputs. The A input comes from the ReadData1 output of the registers, which is controlled by the rs field. (If you think of the Registers as an array, Reg[rs] is the value on ReadData1) The B input comes from the multiplexor which is controlled by ALUSrc, which was set to a 1 by the control. This means that the value for B comes from the ImmData(32) bus, which is basically the I-data portion of the instruction. For a lw instruction this is the “offset”. Essentially the ALU is computing: Reg[rs] + IData. This represents the actual memory address of the value we want to retrieve and is provided as the “index” into the memory. So the lw instruction “loads” the value of Memory[ Reg[st] + IData ]. A full description of the interaction between the Register array, the Memory array, and the fields of the instruction (rs, rt, and IData) would be: Reg[rt] = Memory[ Reg[rs] + IData ]. 2 +