View PDF

advertisement

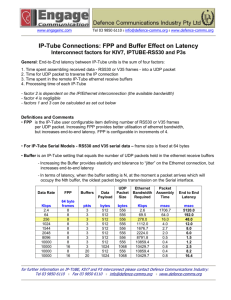

MATLAB® Digest Modeling System Architecture and Resource Constraints Using Discrete-Event Simulation By Anuja Apte Optimizing system resource utilization is a key design objective for system engineers in communications, electronics, and other industries. System resources such as processors, memory, or bandwidth on a communication bus are often shared by various components in the system. To Products Used ■ Simulink® ■ SimEvents™ ■ Stateflow® understand the utilization of a shared resource, system engineers must do two things: identify constraints on the resource, such as number of processors and memory size, and analyze the effect of input traffic or load on the shared resource. The time-varying nature of the input traffic SimEvents™ extends the Simulink® envi- Ethernet Communication Bus makes it difficult to analyze behaviors such as ronment for Model-Based Design into the The system in this example is a LAN consist- congestion, overload, end-to-end latencies, discrete-event simulation domain. In this ing of three network interface cards (NICs) or packet loss. The challenge is to efficiently article, we use SimEvents to analyze resource that share bandwidth on an Ethernet bus. model the system’s response to changing in- constraints on three typical systems: We want to add another NIC and a printer put traffic patterns. These systems are best • An Ethernet communication bus to this bus—but will the bus have enough modeled as event-driven or activity-based systems, since the input traffic activity places the load on the shared resource. Discrete- • A real-time operating system (RTOS) with prioritized task execution event simulation (DES) is the most suitable • A shared memory management system simulation paradigm for modeling event- In each case, the simulation results will en- driven or activity-based systems. able us to understand the effects of resource constraints on the system and to determine next steps. 1 MATLAB Digest www.mathworks.com bandwidth to support them? To answer this question, we must determine the channel utilization by evaluating the current load on the bus. As utilization increases, the end-to-end latency experienced by a packet increases in a non-linear fashion. Figure 1. Ethernet bus. If the Ethernet bus is heavily utilized by the controller that governs each computer’s use Standard Ethernet networks use a Carrier current load, it cannot support additional of the shared channel, and a T-junction that Sense Multiple Access with Collision Detec- devices; connecting new devices will in- connects the computer to the network. tion (CSMA/CD) protocol to manage use of crease communication latencies and reduce The terminator, T-junction, and cable blocks the shared channel. Within this protocol, a throughput for all the devices. at the bottom of the model represent physical Figure 1 shows the SimEvents model of the components of the bus. The blocks labeled system. The model includes the application “Cable” model the communication latency that sends and receives data over the Eth- based on the cable length. ernet bus, a medium-access control (MAC) collision occurs if transmissions from two computers compete for use of the channel. The colliding packets can make additional attempts to access the channel. The number of attempts and the time intervals between them are determined by a binary exponential backoff algorithm—implemented in the MAC Controller subsystem in our example. The Stateflow® chart in Figure 2 shows the implementation of the binary exponential backoff algorithm. In this setup, all applications transmit at an average rate of 100 packets per second and the packet size varies from 64 byte to 1500 bytes. Simulation of this system enables us to visualize characteristics such as the utilization of the Ethernet bus, the throughput for a particular computer, and the average latency for message transmission. Figure 2. Stateflow® chart showing binary exponential backoff algorithm. 2 MATLAB Digest www.mathworks.com tasks in the main loop of the RTOS and highpriority interrupt tasks that invoke interrupt service routines (ISRs). Execution of interrupt service routine delays the processing of application tasks, since the application tasks wait Figure 3a. Channel utilization. Figure 3b. Throughput of node B. in the task queue while the ISR is executing. Ideally, the number of tasks waiting in the Figure 3a shows the overall channel utili- Next steps could include testing the model task queue should not increase and the RTOS zation, or the proportion of time that the with different parameter sets and traffic should return to the idle task to avoid exces- channel is in use. We can also visualize patterns by using SimEvents with System- sive processing delays. How can we verify other characteristics, such as the through- Test to perform Monte Carlo analysis on that the RTOS satisfies this requirement? put of node B (Figure 3b). the model. To answer this question we must model the Channel utilization is low, indicating that the Real-Time Operating System with Prioritized Task Execution shared processor and its interaction with bus might be able to support additional traffic. We can now incorporate the traffic from additional devices into the model and study their effect on overall channel utilization and the throughput of individual devices. This example models the prioritized task execution in an RTOS. Tasks with different priority levels share the processor in such a system. Typical tasks include low-priority application Figure 4. Operating system with prioritized task execution. 3 MATLAB Digest www.mathworks.com application tasks and interrupts. Specifi­cally, the model should demonstrate priority-based task execution and preemption. Figure 4 shows the SimEvents model of such a system. The Task Token Generators section contains Since we cannot control the input rate of tasks, to model behaviors such as packet loss from subsystems that generate high-priority to- next steps might include exploring the use of a the receive buffer and its relation to the size of kens for interrupts and low- priority tokens high-speed processor to reduce the number of the shared memory. for application tasks. The tokens carry an tasks waiting in the task queue. Figure 6 shows the SimEvents model of this Shared Memory Management system. The upper part of the model describes attribute (TaskExecTime) that indicates the execution time for that task. The Task Token Manager section contains the task queue and the processor shared by the input tasks. The Priority-Based Task Queue sorts the current queued tasks according to priority. Interrupt task tokens entering this queue preempt the application task token being served in the processor. Upon preemption, the application task returns to the Priority Based Queue. The system in this example is a communication device on a custom hardware board or a system on a chip that manages a buffer shared by the transmit buffering and receive buffering functions. Messages are dropped when the buffer is a receive buffer, where messages arrive from an I/O device such as a universal asynchronous receiver transmitter (UART). The lower part of the model describes a transmit buffer, where messages wait before transmission. full. Low packet drop rate for the receive buffer Both receive and transmit buffers model the is more important than the transmit buffer following processes: because packets can be retransmitted if they Generation of variable-size messages. The This task resumes its processing when the are dropped from the transmit buffer. interrupt service routine is complete. The The quality of service (QoS) requirements with variable size. Each message consumes a dashed function-call signal lines are used to limit the probability of losing received pack- certain space from the shared memory, de- generate tasks whose execution depends on ets to 1%. How do we determine whether the pending on its size. the completion of another task. design has enough memory to satisfy this We simulate this model and generate a plot requirement? To answer this question we need showing the number of tasks in the task queue changing over simulation time (Figure 5). Figure 5. Task queue length. The plot indicates that the number of tasks waiting to be processed increases over time, and that the task queue does not return to Figure 6. Shared memory management. an empty state. It seems that the processor is not fast enough to support the high input rate of tasks. 4 MATLAB Digest www.mathworks.com traffic-generation process generates messages Regulation of the messages that cannot from a buffer when the buffer size crosses be stored in the buffer. When a buffer the threshold. An advanced version of this size crosses a user-defined threshold, the model shows that the packet loss rate can be Message Flow Regulation subsystems begin reduced using these techniques. The follow- to drop incoming messages. ing table shows the packet loss rates with this Storage of messages in a buffer. The advanced model. receive and transmit buffers share memory, and the receive buffer is given a preference. The memory available for transmitting Memory Size Rx Packet Loss without Priority based QoS 8192Packet Loss (Low Priority): 1.13% messages is limited to that which is unused Packet Loss by the receive buffer. The Transmit Buffer (High Priority): 0 % and Receive Buffer subsystems both have input signals labeled “cap” that represent the capacity of each buffer. Benefits of this Approach Service of messages. The block labeled Rx This article illustrates the value of discrete- Message Server models the delay in forward- event simulation using SimEvents to per- ing messages over the I/O bus that connects form the following design tasks: to other components. The block labeled Tx Message Server models the delay in transmitting messages. • Identify constraints on shared resources and bottlenecks in a system • Simulate the effects of variable input During simulation, the Rx Message Loss Rate block displays packet loss rate for traffic, such as congestion, packet loss, and increased end-to-end latencies receive buffer. As Figure 6 shows, the packet • Explore different design techniques and loss rate at the receive buffer is 6%, which algorithms to optimize resource allocation does not satisfy the QoS requirement of 1% . The real strength of this approach comes To study the effect of memory size on this from the integration of SimEvents with packet loss rate, we simulate this system MATLAB® and Simulink. In addition, inte- with increased memory size. The following gration with tools such as SystemTest™ and packet loss rates are observed for these simu- Stateflow enable many other design tasks, lation runs: such as Monte Carlo analysis or implement- Memory Size 8192 10240 16384 Rx Packet Loss without Priority based QoS 6.6% 4.4% 0% These results indicate that packet loss rates decrease as memory size increases. As a system engineer, however, you might want to explore other techniques to reduce the packet loss rate, such as implementing prioritized regulation of messages (dropping low-priority messages before high-priority messages) and clearing the oldest messages 5 MATLAB Digest ing control logic in event-driven systems for Model-Based Design. ■ References Cassandras, C. G. and S. Lafortune. Introduction to Discrete Event Systems. 2nd edition. Springer Publishers (2007). Lenand, W.; Taqqu, M; Willinger, W; and Wilson, D. “On the Self Similar Nature of Ethernet Traffic (Extended Version).” IEEE/ACM Transactions on Networking, February 1994 . www.mathworks.com Resources For More Information visit www.mathworks.com Demos Technical Support www.mathworks.com/support ■Distributed Processing of Packets: www.mathworks.com/des_packets ■Modeling a Multitasking Operating System: Online User Community www.mathworks.com/matlabcentral www.mathworks.com/des_operatingsys ■Performance Evaluation of a Distributed Processing Network using SimEvents and SystemTest: www.mathworks.com/des_network Demos www.mathworks.com/demos Training Services www.mathworks.com/training Webinars ■Discrete Event and Hybrid Modeling Third-Party Products and Services www.mathworks.com/connections with SimEvents: www.mathworks.com/wbnr14278 ■Integrating MATLAB, Simulink and Stateflow Worldwide CONTACTS www.mathworks.com/contact Components in a SimEvents Model: www.mathworks.com/wbnr15638 e-mail info@mathworks.com © 2008 The MathWorks, Inc. MATLAB and Simulink are registered trademarks of The MathWorks, Inc. See www. mathworks.com/trademarks for a list of additional trademarks. Other product or brand names may be trademarks or registered trademarks of their respective holders. 91564v00 03/08 6 MATLAB Digest www.mathworks.com